抗辐照刷新电路在星载电子系统中的应用

2021-07-05钱小东宣浩韩晋乔兴旺

钱小东 宣浩 韩晋 乔兴旺

(1.中国电子科技集团公司第三十八研究所 安徽省合肥市 230088)(2.孔径阵列与空间探测安徽省重点实验室 安徽省合肥市 230088)

1 引言

基于CMOS 工艺的SRAM 型FPGA 以其功能密度高、体积小、功耗低、半定制可灵活配置、速度快、可重复编程和容量大等优点,被大量应用于卫星电子产品中[1]。但是受地球辐射带和宇宙射线等恶劣空间环境的影响,卫星系统中的电子元器件受单粒子事件和总剂量等空间辐射影响,会出现工作异常,甚至会导致整个系统的崩溃。随着电子系统复杂度越来越高,对FPGA 等超大规模集成电路的依赖性越来越强,电路容量增大,工作电压的降低使得在空间辐射环境下的可靠性大幅降低。因此对FPGA 进行抗单粒子容错设计是各国航天界的研究重点和热点。

针对SRAM 型FPGA,在实际空间应用中实施并能显著提高FPGA 可靠性的技术可分为设计缓解技术和重配置技术。设计缓解技术是指利用冗余(硬件冗余、信息冗余)技术对设计进行故障屏蔽,比如硬件主备份、三模冗余(TMR)或者检错纠错码(DEAC)等技术,但是冗余设计势必需要增加额外资源,因此会带来系统的性能、大小、重量、功能和可靠性的影响。除此以外,对SRAM 型FPGA 的配置存储器进行自动刷新、回读和重配置是一种有效的抗SEU 的方法[2]。自动刷新能够周期性地消除SEU 对FPGA 配置位带来的影响。回读和重配置则是在FPGA 运行过程中通过回读检验配置数据的正确性,仅在发现错误时进行重新配置,因此能够减少配置次数,更加高效地对故障进行恢复。

传统的针对国内星载应用较多的SRAM 型FPGA,特别是Xilinx Virtex4 或者Virtex5 实现的回读刷新纠错技术、重构技术等,主要在FPGA 配置接口添加外围电路,包括使用反熔丝FPGA 作为控制芯片、抗辐照PROM 作为码流存储芯片,例如使用A54SX32A芯片实现的对SRAM 型FPGA 配置数据进行ms 级的周期刷新[3]。但是此种方式需要针对应用SRAM 型FPGA 的配置方式、配置帧格式,刷新配置流程等熟悉掌握,软硬件设计较为复杂。因此本文使用国产智能刷新控制芯片实现SRAM 型FPGA 的刷新配置、在轨重构等功能,且软硬件设计难度大幅降低,同时可靠性极大提高。

2 系统设计

作为一款专用集成电路,北京微电子技术研究所研制的通用智能刷新控制电路BM501‐003ECBRH 可以支持Xilinx 公司多种耐辐射型以及北京微电子技术研究所兼容类型的SRAM 型FPGA 空间应用提供上电配置、实时刷新、在轨重构、单粒子功能中断监测的应用解决方案,保证FPGA 在轨使用的可靠性和安全性,大幅度降低刷新系统设计的难度和复杂度。基于BM501‐003ECBRH 的高可靠性星载FPGA 平台设计方案如图1所示。

图1:基于动态重构管理集成电路的FPGA 平台系统设计

由图1 可知,BM501 位于FPGA 与存储码流的PROM 或者Flash 之间,起到数据交换的桥梁作用。BM501 对外主要有Nor Flash 接口、PROM 接口、与FPGA 的SelectMAP 接口以及硬件配置端口。针对本设计方案中选用的BQR5VSX95T 型FPGA,Flash选用一片复旦微电子的64Mb Nor Flash JFM29LV641RH 作为重构的码流存储器,同时支持使用两片串联的XCF32P PROM 作为调试配置存储,并且为了调试方便,采用主串模式配置电路将FPGA 的JTAG 调试口接出。后期可使用XQR17V16/B17V16RH 作为正样配置存储器替代Flash 型PROM XCF32P。系统时钟Sysclk 最高频率为20MHz,所有功能都由该时钟驱动,使用晶振持续提供工作时钟确保刷新周期的完整性。外围电源监测芯片上电产生低电平复位信号给BM501,复位后即进入上电配置状态。

FPGA 上电/复位后工作于从SelectMAP 模式,BM501 根据SEL_BIT 管脚状态选择从PROM(SEL_BIT 管脚下拉接低电平)或者Flash(SEL_BIT 管脚上拉接高电平)读取配置码流对FPGA 进行上电/复位配置,一旦检测到DONE 信号拉高,说明上电配置成功,随后进行工作模式获取以及任务调度,工作模式默认由外部FPGA 动态配置使能信号(DYNA_PROG,接1,动态重配使能)、FPGA 刷新模式控制信号(MODE_SCRUB,接0,定时刷新使能)、FPGA 刷新使能信号(EN_SCRUB,接1,刷新使能)、刷新/回读间隔设置信号(INTERVEL,接000,刷新间隔设置为最低时间间隔,214.7s)等信号管脚设定,改变管脚状态或者由UART 输入指令可以更新内部寄存器状态,并根据内部寄存器状态确定相应的工作模式,对FPGA 执行器件识别、GoldenCRC 获取、指令配置、定时刷新、定时回读等工作任务。

初始设计时将SEL_BIT 管脚下拉接地,上电配置期间BM501读取PROM 中固化的码流数据配置FPGA 配置空间,一旦配置成功,会根据外围电路设置执行定时刷新、回读等操作。如果需要更改工作模式,则通过UART 读取内部寄存器确定当前状态并写相应内部寄存器执行相应任务,比如更改刷新间隔,或者从Flash 中读取码流文件对FPGA 进行重配置。

配置/刷新/回读的状态实时更新在内部寄存器中。SEFI 检测中对 DONE 信号的监测贯穿在整个流程中,DONE 变低时根据当前设置的码流信息源立即执行 FPGA 配置;对FAR 寄存器、STATUS 寄存器的监控在每次回读/刷新之前进行,SEFI 监测结果同步更新在内部寄存器中。

通过UART 接口命令,用户可以读取内部寄存器、设置工作模式、对FLASH 进行操作控制、发送指令配置FPGA。UART 接口采用9 位的传输模式,包含1bit 起始位、8bit 数据位和1bit 结束位,每一字节的数传按照以下格式自左向右传输,具体如表1所示。

表1:UART 接口字节传输格式

在进行多字节传输时,先发送最高字节数据,然后发送次高字节数据,最后发送最低字节数据,各字节低位在前,高位在后。通过设置UART_BR_SEL 管脚决定UART 的传输波特率,也可以通过向内部寄存器写入自定义的波特率重载值完成UART 接口波特率的切换。

3 基于BM501对FPGA在轨重构功能的实现

当FPGA 的码流源选择为Flash 时,在每次刷新/回读操作之前,BM501 都会对Flash 中的数据进行轮巡校验,每组编码后的数据若存在1bit/2bit 错误则会自动纠正将正确的数据写入Flash,若存在3bit 及以上错误将在内部寄存器中指示出错的扇区并终止后续的刷新操作。除了纠正Flash 中码流的错误,利用有限的星上硬件资源,发挥可重构技术的技术优势可以实现目前星载,特别是小卫星多任务可并行、应用功能可重构、系统高集成度的发展趋势[4]。

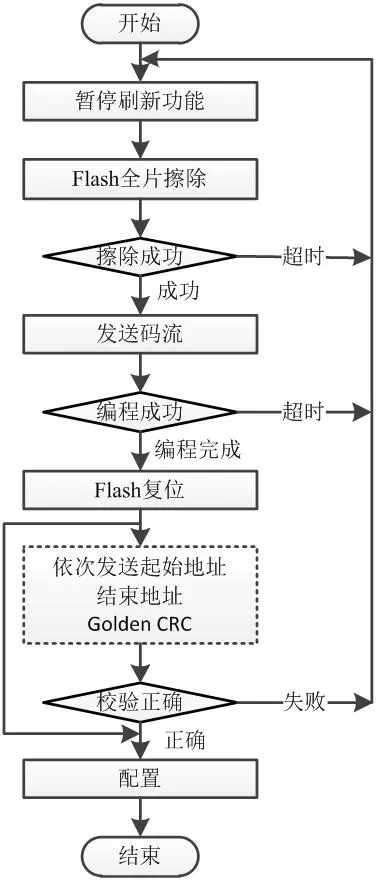

通过其他处理器与BM501 建立的UART 通信,只需按照BM501 UART 接口数据链路层传输协议就可以实现对Flash 的擦除、编程、复位等操作,从而实现在轨重构的功能。执行FLASH 操作建议先将芯片设置为空闲工作模式。图2 为码流烧写软件流程图。

图2:FPGA 重构操作流程

数据链路层的帧包含命令帧和应答帧,应答帧分为2 种,一种是代表校验结果与超时信号的应答帧,另外一种是有效数据应答帧,在读取BM501 内部寄存器和读Flash 时会返回有效应答帧。以暂停刷新功能为例,向BM501 内部寄存器2 发送“写寄存器”操作,会立即返回0xD2D2。命令格式如表2所示。

表2:写寄存器

其中UART ID 为UART 接口ID 地址信号,通过UART_ID[4:0]外部管脚配置本节点UART 接口地址;长度域自命令域开始的字节数;命令域0x05 表示写寄存器命令;地址域低6 位为写寄存器的起始地址,此时为寄存器2;数据域为UART 链路层有效数据,最大长度不超过1024 字节,且约定采用偶数字节的长度;校验域采用异或和的校验方式,校验范围从帧头到数据域部分。

把一个原始FPGA 码流或经BCH 编码之后的码流烧写到Flash中,需要发送若干个重构数据帧,每帧发送之后读寄存器0 的[7:4]标志位判断该帧数据是否编程成功(0xa 表示编程完成,0x9 表示发生编程超时)。若编程成功则可以继续发下一帧,编程未完成时,读寄存器串口无响应。

码流发送完成之后,如果需要对Flash 中烧写的码流进行校验,发送FLASH 存储码流的起始地址和结束地址。若采用BCH 编码方式预先对码流进行编码,为实现EDAC功能,还需将每个扇区的Golden CRC 写入FLASH。可选择全局 Golden CRC 命令对码流进行整体校验,在以上数据和命令发送完毕之后再发送一个全局Golden CRC 命令即可。

4 结束语

本文基于国产智能刷新控制芯片设计实现了一种空间高可靠性FPGA 应用平台方案,借助于智能刷新电路的“智能性”、“易用性”使用较少的外围电路和简单的管脚配置,结合软件流程设计就可以实现较为复杂和全面的SRAM 型FPGA 智能刷新、纠错、重构等高级功能,进而可以有效解决SRAM 型FPGA 在空间应用中面临的单粒子翻转挑战,同时大幅降低刷新重构软硬件复杂度,提高系统可靠性,满足航天领域的应用需求。