低成本数字低频信号源设计

2021-07-05张开骁宋建平雷撼胡利群

张开骁 宋建平 雷撼 胡利群

(1.河海大学理学院 江苏省南京市 210098 2.济南冠鼎信息科技有限公司 山东省济南市 250000)

低频信号源是一种最常用信号源,成本较低的产品一般由模拟电路构成,稳定度和精度都比较低,稳定度和精度高的数字式低频信号源得成本都比较高,为了降低成本,论文给出在ATmega8[1]单片机和通用芯片的低成本硬件平台上如何实现数字信号源优良技术指标的技术方案,主要是通过可预置数定时计数器与PLL 锁相环技术实现频率合成,基于通用EPROM 存储器和DA 芯片的数字波形合成器工作原理和实施方案,介绍了如何充分利用ATmega8 单片机内部资源,给出了全部的电原理图,元器件参数,论文还给出了符合使用习惯的人机界面设计以及电源、功放等外围电路设计。

1 电路工作原理

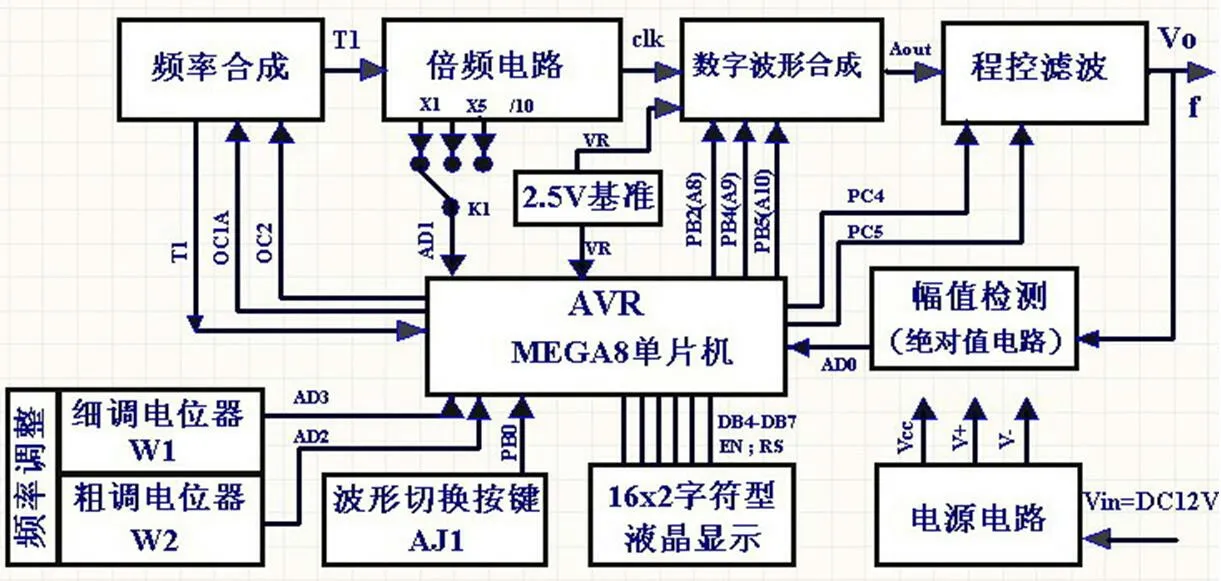

整机电路由频率合成电路、倍频电路、数字波形合成电路、程控滤波电路、单片机人机界面和控制电路以及其它外围电路组成,其电路原理框图如图1所示。电路的信号流程为:频率合成电路产生步距为256Hz 的可调频率信号T1,T1 经过倍频电路进行X1、X5 和÷10 选择,转换成频率为clk 的信号,作为波形存储器的地址,送到数字波形合成电路,读取存储器中存储的波形数据,经由DA转换成模拟信号Aout,送到程控滤波器滤波后生成整机输出信号。调整W1 和W2,可以改变输出频率,K1 可以改变输出频率范围和调整步距,按键AJ1 可以改变输出波形。输出信号的幅值大小、频率值和波形代码可由每行16 字符、每字符5x8 点阵、共两行的液晶显示器显示。整机用单12V 未稳压直流供电,不进行功率放大时工作电流小于100 毫安。

图1

采用PLL 锁相环频率合成器[2]方案,其原理框图如图2所示,在VCO 与Pc 之间设有由N 分频器构成的反馈回路,把VCO 输出的频率为fVCO的信号进行N 分频后得频率为Ft 的信号送到相位比较器Pc 输入端,Pc 的另一输入端输入频率为fr 的标准信号,Pc 的输出信号经低通滤波器LPF 滤波后变成直流电压Vr 送到VCO 输入端。

图2

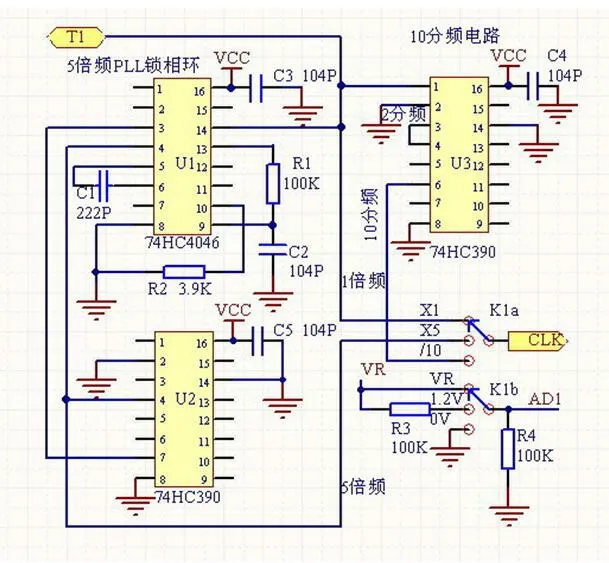

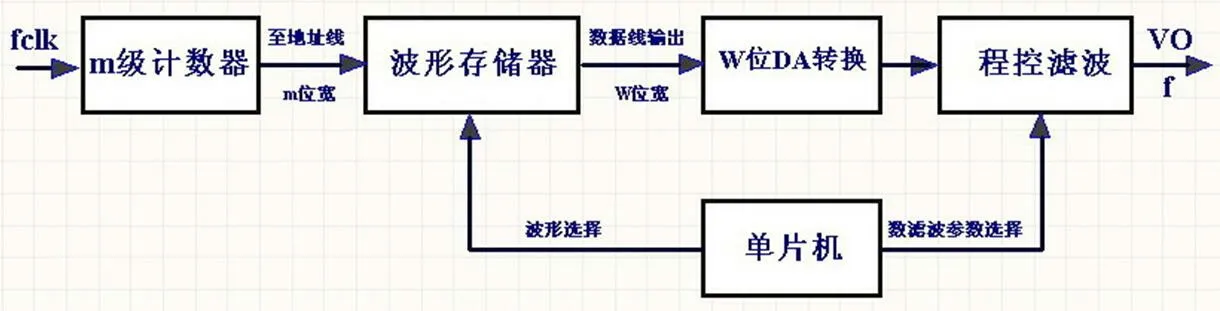

为了扩展输出频率范围,设计了倍频电路,电路如图3所示。共设计有3 种倍频方式:X1 直通方式、X5 方式和÷10 方式。当倍率开关K1 处于x1 位置时,T1 直接送到输出端作为clk 信号;当K1 处于/10 位置,74HC390 工作于计数器状态,FT1 经由U3 组成的10 分频电路送到输出端作为Fclk 信号信号;当K1 处于X5 位置,FT1 经由U1 和U2 组成的PLL 倍频电路进行5 倍频,由于工作频率较高,U1 选用74HC4060[3],元件参数也作相应调整,FT1 经5倍频后作为clk 信号;改变K1 位置就可以获得:在X1 位置时,输出信号范围10Hz~4000Hz,步距1Hz,有效数字5 位;在/10 位置时,输出信号范围10Hz~400Hz,步距0.1Hz;有效数字5 位;在X5 位置时,输出信号范围50Hz~20KHz,步距5Hz;有效数字5 位;通过K1b,K1 在不同位置时AD1 可以获取整数为2V、1V、0V 电压,作为程序判定K1 位置的变量,程序据此判定在液晶上的频率显示值和小数点位置。数字波形合成[4‐5]原理见图4所示,电路实际电路如图5所示。

图3

图4

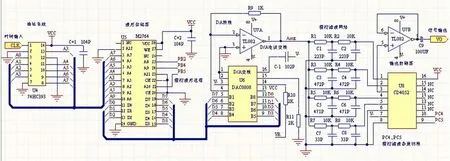

图5

本设计采用74HC393 作为8 级计数器,EPROM 存储器2764作为波形存储器,DAC0808 作为DA 转换器件,这样每周期可获得256 个样本点,幅值量化精度为1/28即<0.5%,既可以满足大部分使用需要,又可以降低成本。此时有fin=fvco=256*N与f=fin/2m=256*N/2m,若m=8,则有f=N。即输出频率简单地在数值上等于N 分频器的分频数,因此只要在TC1 的预置数寄存器OCR1A 中写入N‐1,就获得与N 值相等的输出频率。实际上2716、2732 均可使用,但鉴于性价比选用2764,其高2 位地址线A11、接地,每个存储区域存放一张256 点的波形数据表格,单片机通过控制A8、A9、A10 达到输出不同波形的目的,该控制信号由单片机端口PB2、PB4、PB5 输出。程控滤波器一共提供4种滤波参数,通过模拟开关CD4052 切换不同滤波参数,滤波参数由R1~R8,C1~C8 决定,CD4052 控制信号由单片机端口PC4、PC5 输出。单片机采用美国Atmel 公司AVR 系列8 位单片机ATmega8。基准电路采用TL431,VR=2.5V 的基准电压,用于AD采样基准和DA 输出电路基准,VR 还提供W1、W2 电源,这样做的好处是电位器最大电压恒等于AD 基准电压,理论上确保产品相互之间无离散。

应用程序由初始化、数据输入、输出等模块组成。

初始化过程完成函数声明、子程序定义、变量定义、对调用的硬件资源进行初始化设置等工作。

数据输入模块功能:

(1)通过指定的IO 口获取用户的各种操作,包括旋钮位置、开关状态、按键动作等;

(2)读取AD 对输出信号幅值的测量结果;

(3)把输入数据转换为程序中的变量待处理。

数据输出模块功能:

(1)驱动LCD 液晶显示器,显示输出信号的频率值、输出幅值和波形代码;

(2)控制波形转换;

(3)根据输出频率设置滤波参数。

总言之,由于硬件完成了大部分功能,应用程序只须扫描采集按键和电位器状态数据,据此设置计数器预置数获得预期波形和频率,并把结果送LCD 显示即可。

2 实测指标

实现的技术指标如下。频率范围X1 档10~4000Hz,步距:1Hz;X5 档50~20000Hz,步距:5Hz;X0.1 档1~400Hz,步距:0.1Hz;输出波形为方波、正弦波、三角波、锯齿波等几种;输出电压峰峰值:±2.5V;负载阻抗:≥1kΩ;LCD 显示:2 行,每行16 字符,可同时显示两路信号的波形、频率、输出电压;电源:DC12V;电流≤100mA。在本设计中,频率有效数字位数和温漂、时漂精度取决于石英晶振的精度,本文采用的石英晶振具有如下技术指标。5 位有效数字的频率值:4.0960MHz,时漂和温漂:10‐6ppm/hour.℃,上述指标可以通过提高晶振指标得到改善。采用GFG‐813 型频率计作为标准频率计对样品进行频率精度检测,检测结果见表1。测试结果表明,与标准频率相比,在16KHz 以下符合得很好,超过16KHz 开始有0.001KHz 的微小差别。

表1:测试结果(单位:Hz)

3 结语

论文给出在通用元器件和低成本硬件平台上如何实现数字信号源优良技术指标的技术方案,设计的全部电路均经过实际运行验证,自制的信号源设备已经被河海大学物理实验中心用于实验教学多年,运行效果良好。设备充分利用ATmega8 单片机内部资源和低成本元器件,元件成本可控制在百元以下,样机可生成多种波形,具有数字信号源的主要技术指标,同时又有结构简单、成本低廉、维护方便的优点,具有较高的实用价值,尤其适用于大面积实验教学。