基于神经网络的IC芯片图形缺陷检测技术研究

2021-07-02魏鹏

魏鹏

(中国电子科技集团公司第十一研究所,北京100015)

集成电路(IC)芯片生产过程中往往要经历数十道甚至上百道工艺处理过程。在流片过程中,有许多因素会造成IC芯片质量受损。所以在工艺线上往往会在各个工艺节点完成后增加一个质检环节。通过人工在显微镜下目测芯片图形线条的完好程度,间接地判断芯片有无受损情况,从而达到对芯片进行中间检验和质量把关的目的。另外,近年来在一些特殊的行业,如航空航天,由于对IC芯片的封装体积、散热效率等因素非常敏感,因此不采用封装好的IC芯片,而是直接使用未经过封装的芯片,即称为裸芯片。在裸芯片使用前,必须对每颗裸芯片进行检测,检测的方法也是目视镜检。这一检测环节对航空航天部件、装备的可靠性保障来说尤为重要。

本文主要研究了采用何种技术方法对IC芯片图形缺陷进行可靠、有效、快速地识别与检测。论述的主要内容包括介绍国际上先进的几种图形图像识别检测技术,分析比较了各自的技术特点。

1 IC芯片缺陷检测中所面临的问题

在IC芯片的生产过程中,由于生产环境不理想、制造工艺不完善等问题,IC芯片表面会出现如划痕、外来物污染、短路、断路等各种缺陷问题。这些缺陷不仅影响元器件的外观,甚至会影响元器件的可靠性,对元器件的工作寿命产生重大影响,因此芯片的表面质量检测是值得重视的质检过程。

目前在大多数集成电路生产线上,IC芯片测试是通过探针台和测试仪两种设备联合来完成的。它仅限于对已经具有完全的电路功能的成品芯片进行电气功能的实际加电测试。但这种方法不能对尚未具备完全功能的前工艺流片节点上的芯片进行半成品芯片测试,因此具有一定的使用局限性。

基于卷积神经网络的IC芯片图形缺陷检测是通过对IC芯片经光学系统成像后,进行图像采集,然后利用计算机算法对芯片的图形图像进行识别、分析、归类,以达到芯片缺陷检测的目的。因此这种方法可检测的芯片对象不再拘泥于已具有完全电路功能的成品芯片,而且能对IC生产线上各工艺节点的所有对半成品或成品芯片进行检测,具有适用范围宽,通用性好,测试项目组态灵活,运行成本低等特点。它属于一种间接的质检方法,对及早发现芯片缺陷,避免成本浪费有极大的意义。

2 问题的分析及论述

过去传统芯片的缺陷检测方法是通过人工使用高分辨率数字或光学显微镜进行目测来完成的。该方法不足之处在于:人工操作容易疲劳,检测精度低,进而影响到芯片的目视质检结果。而且受到人眼空间和时间分辨率的限制,人工检测具有主观性强、不确定性大的缺点,很难满足现代工业高精度、高效率的检测需求。现代的检测方法是用计算机图形图像自动识别技术,即机器视觉技术,来代替人工目视镜检。

随着现代图像处理技术及相关信息技术的发展,基于光学图像传感的表面缺陷机器视觉已广泛应用于自动光学检查系统中,提高了缺陷检测的准确性。有许多专家学者对于集成电路缺陷检测技术进行了研究。目前,在计算机视觉技术领域,关于集成电路缺陷的检测方法主要基于传统图像处理的检测方法、传统机器学习法以及深度卷积神经网络法。

基于传统图像处理的检测方法主要是对目标图像进行阈值分割、特征提取等操作实现缺陷的识别、分割与检测[1];基于传统机器学习的检测方法则是通过浅层神经网络、SVM(Support Vector Machine)支持向量机[2],使计算机能够自动学习或发现目标图像中的缺陷特征,实现缺陷检测;基于深度卷积神经网络的检测方法是利用CNN(Convolutional Neural Network)卷积神经网络构建适合于缺陷图形检测的深度模型[3],实现卷积神经网络识别、缺陷分类及判别,进而对产品质量进行评判。本文对目前在IC芯片图形缺陷检测领域所采用的几种检测方法进行了分析比较。

2.1 基于传统图像处理的缺陷检测方法

基于传统图像处理的缺陷检测方法一般可以通过图像阈值分割,图像边缘检测和连通域生长等方法实现。集成电路缺陷检测通常可以分为以下几个步骤:第一步,是对图像的获取与预处理,就是对目标图像进行图像增强、去噪滤波、修复及直方图分析等处理;第二步,是对目标图像进行边缘检测根据图像内容进行阈值分割,提取图像的特征信息,边缘检测常用canny的边缘检测算法,阈值分割可以根据图像的直方图特征选择自适应阈值分割法[4]、OTSU[5]等阈值选择算法;第三步,是通过目标图像中缺陷特征确定缺陷的位置和形态,最终进行缺陷分类识别。

2.2 基于传统机器学习的缺陷检测方法

传统的机器学习缺陷检测主要是通过从已有的大量图像数据中通过学习找出数据中蕴含的知识和规则,然后对新的目标图像做出预测。一般可以分为监督学习和无监督学习两类。国内外大部分关于缺陷检测方法的研究都是基于监督学习,即通过已标记的缺陷图像集,学习得到一个参数模型,当输入一个新的目标图像可以根据得到的参数模型预测其结果。因为集成电路芯片划痕、污染、短路、断路等缺陷特征、尺度多样。缺陷检测的重点集中在特征提取、特征选择和分类器设计三个方面。常见的监督学习方法主要包括SVM支持向量机,ANN(Artificial Neural Network)人工神经网络[6],随机森林[7]和决策树[8]等。

2.3 基于深度卷积神经网络的缺陷检测方法

深度学习DL(Deep Learning)是机器学习的一个分支,卷积神经网络作为深度学习的代表性算法之一,近些年来在图像分割、识别、分类领域表现突出,无论从检测率还是检测精度方面都具有一定的优势,因此本文对基于CNN的集成电路芯片缺陷检测方法进行了详细地论述。

3 问题的解决方法及步骤

传统的缺陷检测方法是基于图像处理,但这些方法只能在特定的检测条件下(如:缺陷轮廓明显,对比度强,噪声低,尺度固定,特定光照)检测出缺陷,本文从实际工业环境中捕获的输入图像,通过卷积神经网络(CNN)将芯片缺陷的输入图像通过机器学习的方法,经过训练生成分类模型,将芯片缺陷划为不同的特定分类;再通过测试集验证各种条件下的工业芯片缺陷检测效果。

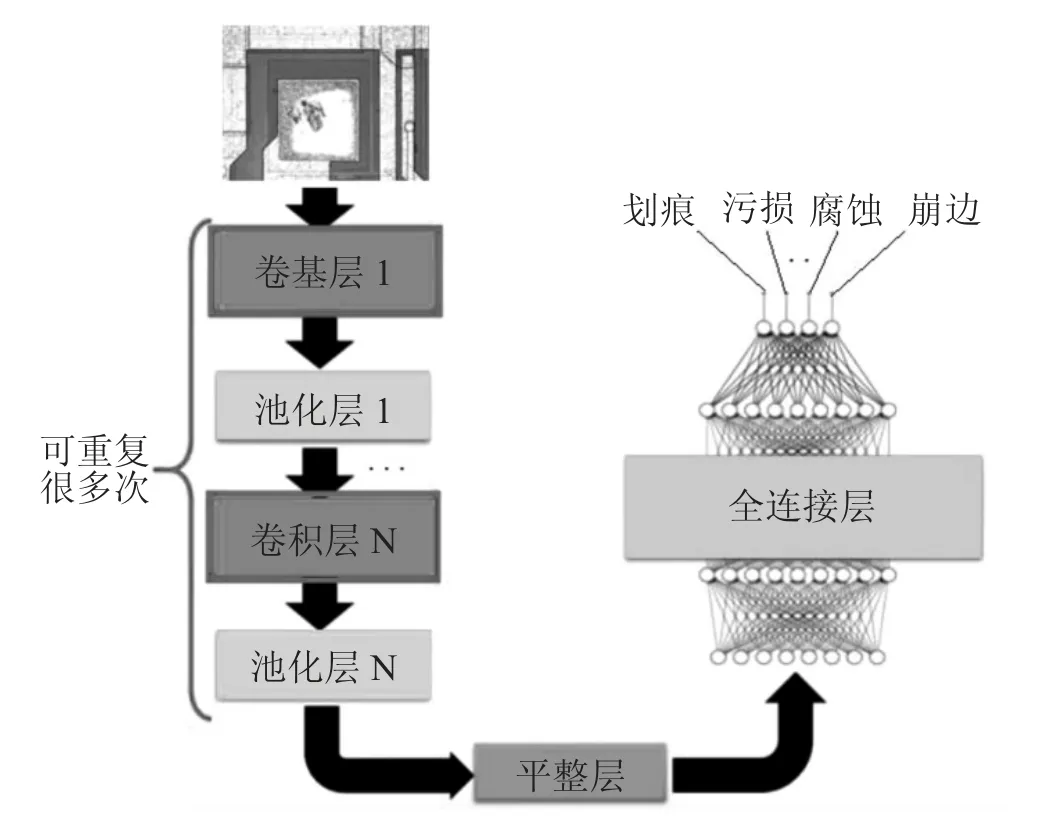

3.1 卷积神经网络

卷积神经网络(CNN)是一种专门用来处理类似网格结构的数据神经网络,图像数据可以看作二维的像素网格。基础的卷积神经网络是由卷积层(convolution layer)、非线性激活层(Nonlinear activation layer)、池化层(pooling layer)、全连接层(FC layer)构成,一般对于CNN来说非线性激活层中的激活函数一般选择修正线性单元Relu(Rectified Linear Unit),和单/多通道图像卷积运算一起统称卷基层。CNN的基本架构如图1所示。

图1 CNN基本架构(缺陷检测)

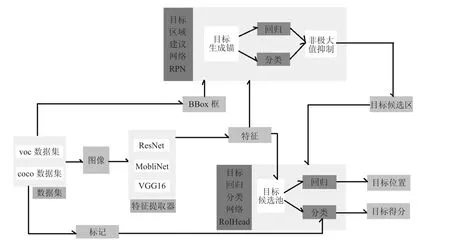

3.2 Faster R-CNN

Faster R-CNN[9]在CNN架构基础上进行了优化,将特征抽取(feature extraction)、候选区建议生成(proposal)、标记矩形回归(bounding box regression)、目标分类(classification)整合在一个网络中,使得综合性能有较大提高,在检测速度方面尤为明显。因此本文选择了Faster R-CNN架构来实现集成电路缺陷检测,整体架构如图2所示。

图2 Faster R-CNN整体架构

Faster R-CNN主要分为4部分:

(1)数据Dataset:提供符合要求的数据格式(常见数据集数据集VOC、COCO);

(2)特征提取器Extractor:利用预训练的网络提取图片特征features(常见的特征提取卷积神经网络,如ZF、VGG16[10],ResNet50、ResNet101[11]);

(3)区域建议网络RPN(Region Proposal Network):负责提供候选区域rois(region of interests),利用提取的特征(feature)经过RPN网络,找出一定数量的rois;

(4)候选区回归RoIHead:分类与回归,负责对候选区域rois进行分类,与ground truth(真实标签)数据对比进行微调,针对RPN找出的rois,判断它是否包含目标,并修正框的位置和坐标。

3.3 残差网络ResNet

集成电路缺陷分类的流程涉及两个模块:缺陷特征提取和缺陷分类。CNN模型与人类学习识别物体的过程是相似的。CNN模型通过大量已标记的训练集图像来捕获缺陷特征,随着深度学习层级的加深,它接触学习到更多的缺陷特征,从而学会了分类缺陷,就像一个孩子通过感知周围环境,随着他的成长,他接触更多的数据,从而学会了识别物体。卷积神经网络就是通过识别图像的特征来进行提取并基于有标签数据进行分类的。

理论上,随着卷积神经网络深度增加,网络的准确度应该同步增加。但是网络深度增加会带来两个问题:

(1)梯度消失/爆炸问题:隐层的增加意味着更多的参数需要确定,根据逆向传播原理,梯度是从后向前传播,当网络深度比较大时比较靠前的层梯度会很小,学习基本就停止了。

(2)优化问题更困难:简单地去增加网络深度与下文提到的残差网络ResNet相比反而会出现更高的训练误差。残差网络设计一种残差模块让我们可以训练更深的网络。

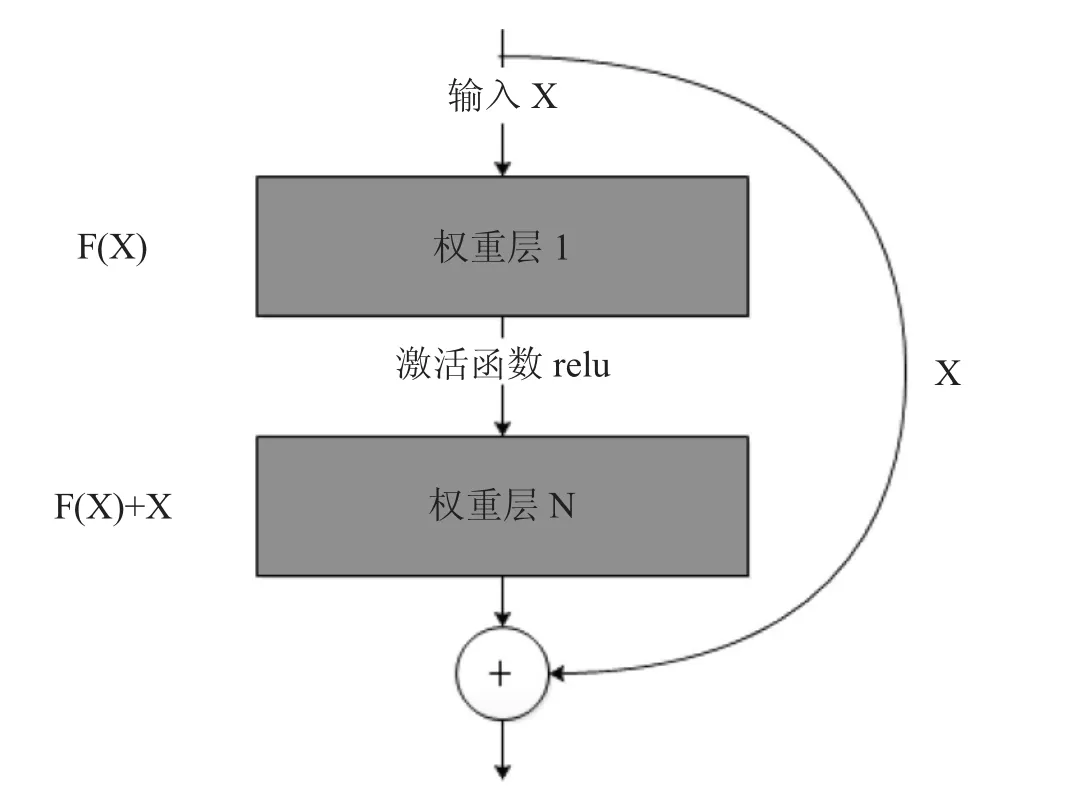

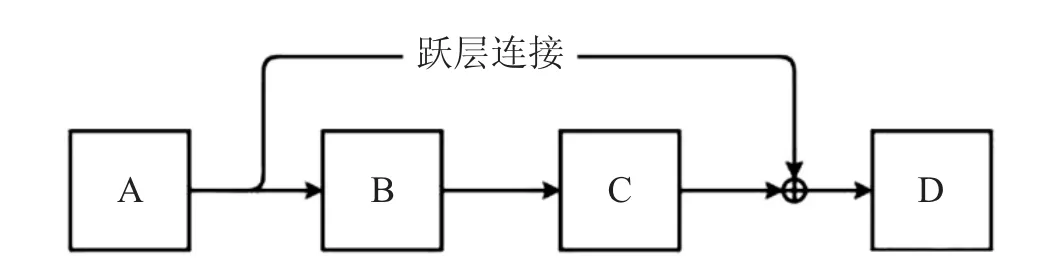

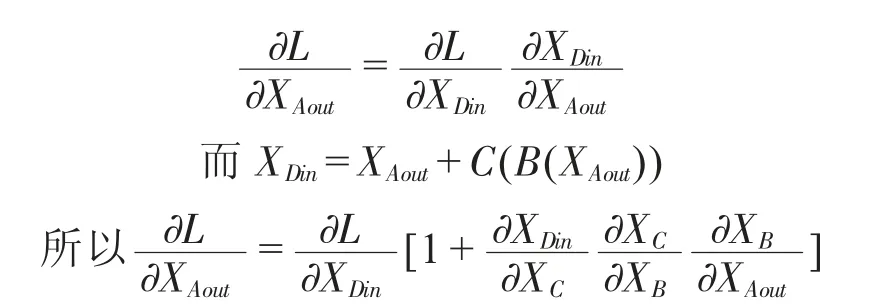

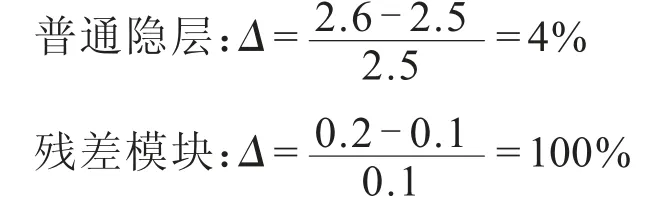

在单纯的前向传播基础上深度残差网络增加了跃层连接(如图3所示)。实践表明,深度残差网路可以有效地改善“深度”网络的性能。

图3 跃层连接

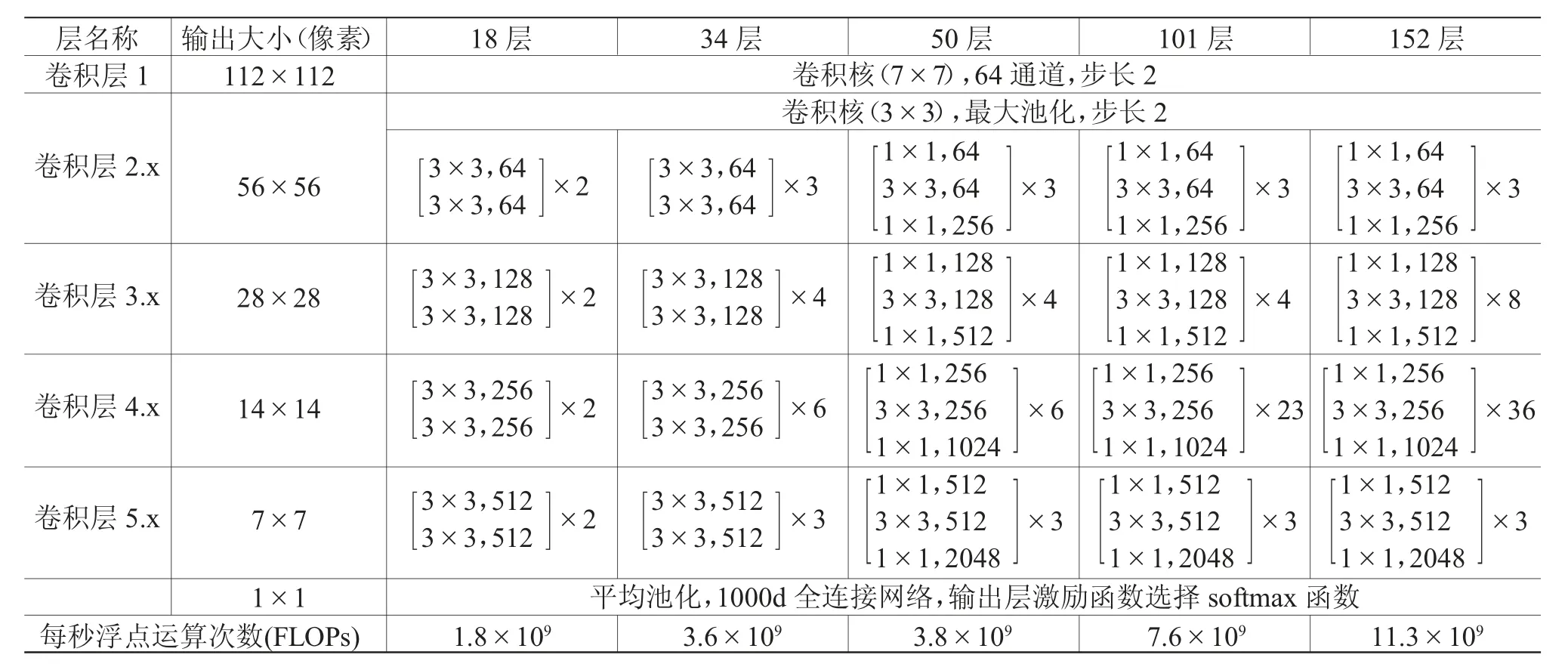

图4(A、B、C、D为4个不同的网络块,箭头代表数据流)解释了为什么看似简单的跃层连接操作能够解决深度网络中梯度消失的问题。假设网络输入从A到D经历两次前向传播以及一次跃层连接,根据后向传播的链式法则:

图4 跃层连接解决梯度消失问题原理图

即使在A-B-C的后向传播中出现梯度衰减的情况,D处的梯度依然能够直接传递到A,也就是实现了梯度的跨层传播。

举例:H(x)=F(x)+x

假设x=2.5,经过n个conv层处理F(x)=0.1,因此H1(x)=2.6,

x=2.6,经过n个conv层处理F(x)=0.2,因此H2(x)=2.7。

由图5及以上实例可以看出由于残差的引入去掉了主体部分,从而突出了微小的变化。因此从应用场景来看,对于像集成电路缺陷这样的微小的目标ResNet比较适合,因此选择了基于残差的faster R-CNN架构。

图5 残差网络示意图

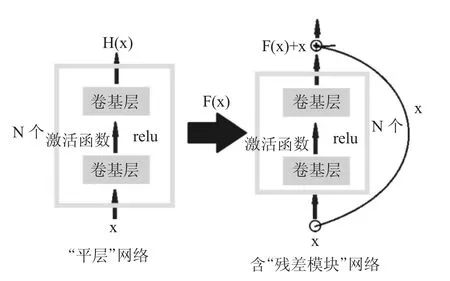

同时残差网络ResNet是当今应用最为广泛的特征提取网络,不同深度的残差网络卷积核也有所不同(如图6所示),在基础的CNN拓扑结构上引入了跨层连接和批量正则化(batch normalization),有效地抑制了梯度消失/爆炸现象。

图6 不同深度的ResNet残差网络

4 结果分析

实验在intel corei7-8550u CPU,4.00 GHz内存8G,64位的操作系统的硬件环境下执行,同时搭载了NVIDA GTX980显卡进行GPU加速,软件实现平台采用OpenCV4.0+PyTorch1.6+Python3.8搭建,由于本实验用于训练的样本数量只有几千张,通常目标缺陷检测的样本需要上万张的量级。

本文通过OpenCV对原数据集进行了缺陷尺度变化、位移等图像处理,将原有图像样本总数从4 000张扩充至10 000张。然后按4:1分配比例将数据集划分为:训练集8 000个样本,测试集2 000个样本。然后将训练集进一步划分为训练集和验证集,比例为3∶1,最终训练集6 000个样本,验证集2 000个样本,测试集2 000个样本。

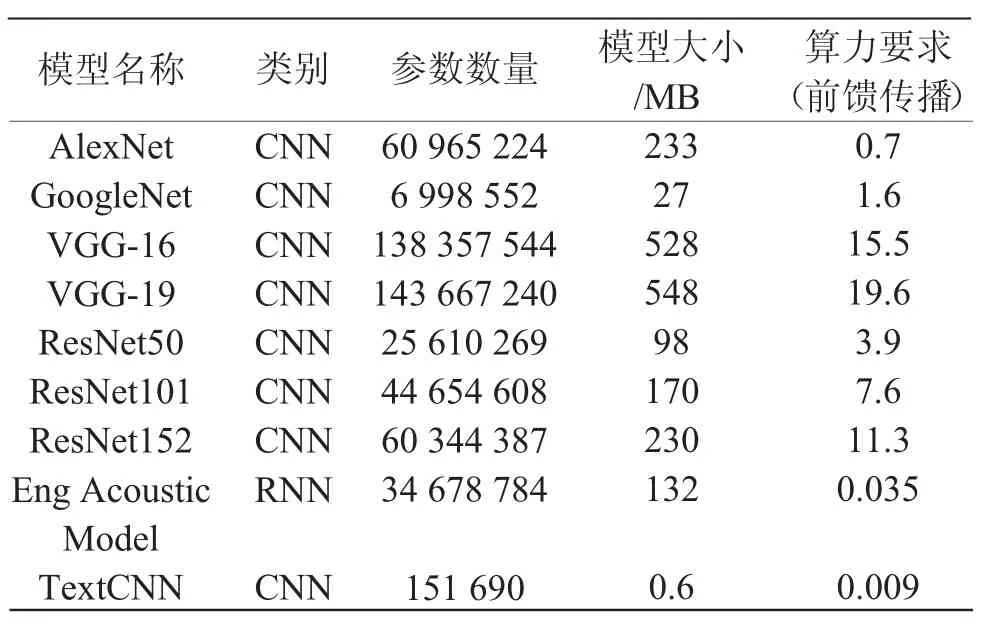

考虑到模型训练时间及算力的要求(如表1所示),本试验的机器学习模型选择了含有ResNet101残差网络的Faster R-CNN,本质上还是属于卷积神经网络。ResNet101残差网络作为图像的特征提取器,一般情况下要求的训练图像规格大小为224×224的分辨率。

表1 流行的深度学习模型的大小及算力要求

接下来进行训练样本的图像预处理工作,通过PyTorch框架下的AdaptiveAvgPool2d(二元自适应均值汇聚层)函数,将集成电路的6 000个训练集输入样本图像从分辨率为500×500转化到ResNet101网络需要的224×224的分辨率。然后对224×224的分辨率训练集图像进行归一化操作,每个通道分别减去训练集该通道平均值。

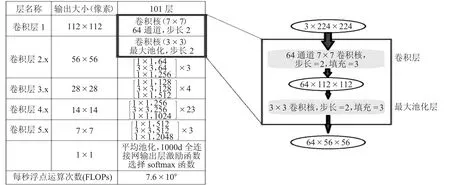

ResNet101残差网络的结构配置,如图7所示。

图7 ResNet101网络结构配置图

模型应用过程中,首先对训练集再ResNet101网络中进行微调,训练出新的网络层参数之后利用先用验证集进行模型训练评价,再通过测试集进行验证。由于模型训练的时间比较长,在7~8个小时,训练过程中的迭代次数本文选择了10,每次梯度下降的样本数(batch_size)设置为200,学习率设置为0.01。

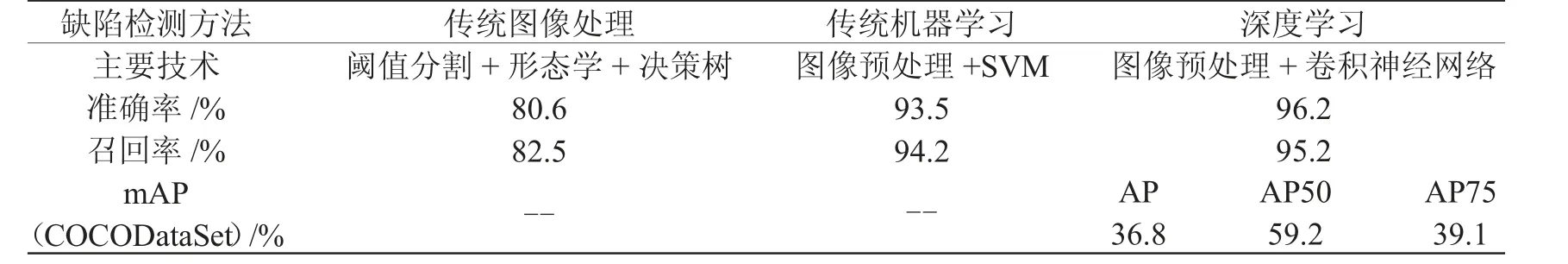

为了对比卷积神经网络的在集成电路芯片缺陷探测的准确率,另外选取了基于传统图像处理(图像阈值分割+形态学+决策树)的方法,基于传统机器学习的方法(图像预处理+支持向量机SVM)的方法作为对比如表2所示。

表2 缺陷检测方法性能对比

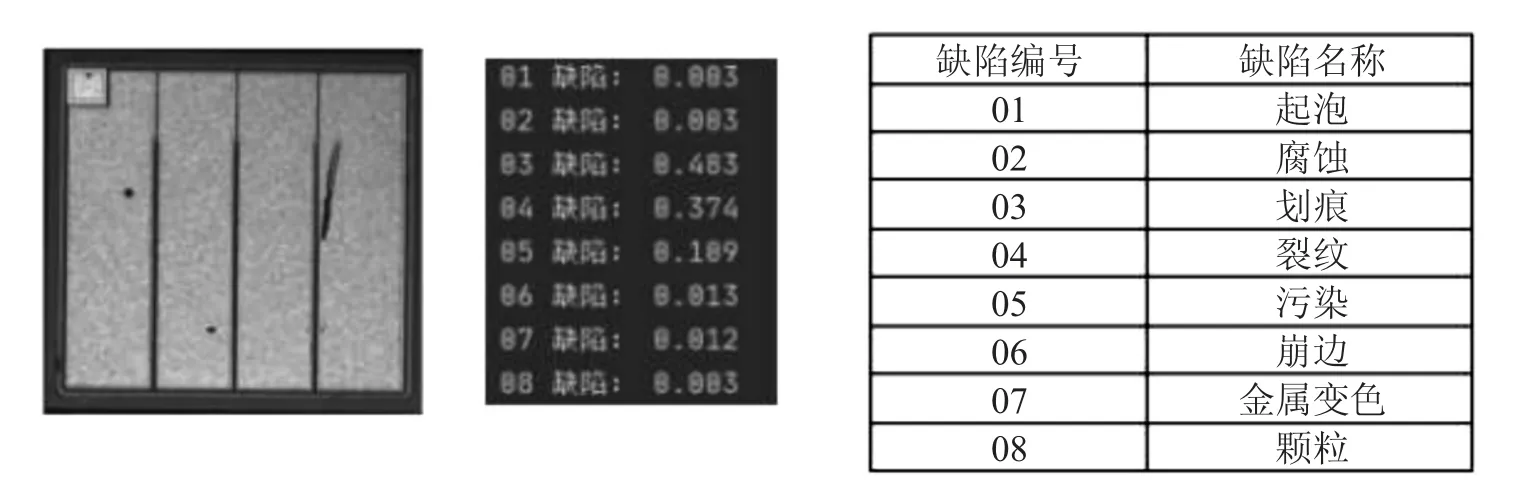

根据图8的测试结果显示:03缺陷划痕出现的概率最大,为0.483,因此判定该测试芯片缺陷为划痕。与人工判别的结果一致,而且缺陷的位置也通过bounding box标记了出来。

图8 测试结果

5 结束语

实验表明,基于卷积神经网络的方法对IC芯片图形缺陷进行识别是完全可行的,而且具有较高的识别准确率。它对缺陷类型的识别和区分,是通过人工智能的机器自动学习来实现的,符合当前智能装备技术发展应用的潮流和方向,因此具有先进的技术特征。该缺陷检测技术可以应用在实际的IC芯片缺陷识别的场景中,拥有较好的应用前景。

研究表明,含有残差网络设计的卷积神经网络可以应用到集成电路芯片缺陷检测领域,而且取得了较好的效果,但由于复杂工业条件下影响检测准确率、召回率的因素还有很多,该算法还有继续优化的空间。卷积神经网络等深度学习的检测方法正在逐步取代传统的人工目测法,成为元器件表面缺陷检测的重要方法,越来越受到产业界的重视。

通过卷积神经网络在集成电路芯片检测领域的研究,有助于进一步研发一种基于深度学习的裸芯片表面缺陷检测设备及其分析系统,对提升半导体芯片封装测试设备自主研发能力具有非常重要的意义。