一种HfOx阻变存储器的1T1R单元设计

2021-06-30北方工业大学黄传辉

北方工业大学 黄传辉 戴 澜

本文基于UMC 28nm工艺和HfOx体系的RRAM器件进行1T1R存储单元设计,采用低压NMOS控制,提高1T1R单元的集成度,降低操作电压,以突破传统非易失性存储器闪存所面临的设计瓶颈,并最终流片验证。设计和测试结果表明最小存储单元面积达0.053um2,操作电压控制在1.8V以内。

以闪存为基础的非易失性存储架构虽是目前的主流方案,但是伴随着工艺制程地进步,其在物理、工艺、成本等诸多方面上面临着难以突破的瓶颈。阻变存储器(resistor RAM,RRAM)作为一种新型存储器,可以有效的解决如今的困境,被认为是闪存的替代方案之一。由于RRAM与CMOS工艺优异的兼容性,以一个晶体管(Transistor)和一个阻变器件(RRAM)加在一起构成的存储单元结构被称为1T1R结构,其基础的想法就是利用晶体管的开关特性作为RRAM的整流器件来抑制串通电流,这样就能实现对每一位存储单元的随机控制。

本文基于在UMC 28nm HPC标准CMOS逻辑工艺中上集成的RRAM制程,完成对1T1R存储单元的设计。与之前成果相比,实现低压NMOS与RRAM集成并操作正常,以提高存储密度。

1 1T1R单元设计

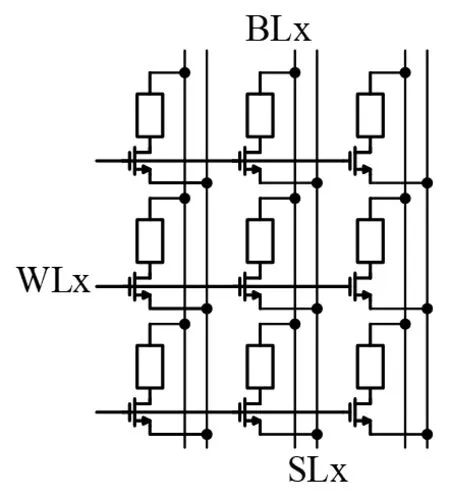

本文中使用的是基于HfOx体系的双极性RRAM,在TE上施加高电压为正向操作。图1中描述了RRAM器件结构,其制造于ME1和ME2之间,依靠中间的TMO层完成高阻态(存“0”)和低阻态(存“1”)的转换。存储单元的架构如图2所示,BL和SL平行分别接RRAM的上级和晶体管的源极;WL连接晶体管的栅极控制电流通路,与其他控制线垂直。对于存储的操作有Forming,Set,Reset,Read,分别实现数据的正常读写。但是因为RRAM的操作电压除read外一般高于CMOS逻辑电压0.9V,若采用高压器件则会大大增加存储单元的面积消耗。为了进一步提高集成度,本次设计采用UMC的HVT MOS,在不破坏器件的情况下适当地过驱动使用,以获得极高的存储密度。

图1 HfOx RRAM结构

图2 1T1R阵列架构

因为RRAM的写入时BL和SL间的电压超过了CMOS正常操作范围,所以在设计时需要重点考虑。在选择RRAM的高低阻值时,应注意需大于MOS的内阻,这样在操作时因为分压的关系,实际作用在MOS上的电压是可以控制在正常范围内的。对于没有选中的存储单元,高压作用与MOS的源漏极,发生可恢复的PN结击穿,这样会造成漏电增加,故需要严格控制存储阵列中每一个存储模块的规模。下面根据图3设计1T1R具体的操作方法。

图3 1T1R操作

Forming和Set操作的极性一致,只是电压的具体值不同,所以可以同时讨论,此种情况下VSL为0V,电压施加于BL和WL上。VBL需满足VHRS+VDS的阻变条件,通过VWL控制晶体管的电流ICC进而控制低阻态的阻值,将Set成功后的VDS在0.9V以内。Reset操作的极性于上述相反,需要在SL上施加高压,BL为0V。因为体效应的影响晶体管驱动能力减弱,所以Reset时需要更高的电压,也会有更大的风险。设计操作条件时,首先应满足VSL大于VDS+VLRS,以达到Reset条件。阻变过程中电流减小,电阻变大,需控制RRAM的BE电压始终满足VWL大于VGS+VHRS。最后以获取足够的驱动能力为目的,在不破坏晶体管的前提下,权衡VWL和晶体管的尺寸,因为栅极击穿时不可恢复的。

最后Read操作的电压范围在0.9V以内,通过比较流过RRAM的电流与参考电流之差分辨存储的数据。因为1T1R结果此时没有极性,所以从任何一段读取电流均可完成Read操作,因为RRAM阻值大于晶体管内阻,所以不会影响读取结果。

在完成上述设计分析后绘制1T1R单元版图,为了提高存储单元的集成度,将2bit单元共用一条BL和SL,并且共用一个晶体管源极,以减小面积消耗。存储单元使用两层金属,NMOS尺寸为170nm/40nm,实际尺寸为0.053um2,与之前的成果相比,该器件具有较小的单元尺寸面积和较大的存储密度。

图4 1T1R存储单元版图

2 测试结果与验证

本次流片基于UMC 28nm工艺加RRAM制程的方式完成流片,如图5所示,所有的1T1R结构放置在20个PAD的Testkey上,分别接出WL、BL、SL和BULK端,其中每条Testkey的WL和衬底共用。测试系统由MPITS3000半自动探针台和Tek4200A半导体测试仪组成,分别完成Forming、Set、Reset和Read等RRAM基本操作的验证。测试结果表明1T1R单元可以完成上述的各项操作,并实现数据的随机读写。图6表明RRAM可以在0.8V完成写“1”的Set操作,1.1V实现写“0”的Reset操作,高压均控制在一倍过驱动电压以内。

图5 1T1R Testkey照片

图6 1T1R测试结果

总结:文中介绍了一种1T1R电路结构的设计方法,基于USC 28nm工艺成功流片并验证。通过优化设计,可以使用低压的HVT NMOS作为选通器件,合理配置晶体管和RRAM的尺寸,提高1T1R结构的集成度,提升驱动效率,降低存储操作的电压和电路功耗。