FFT算法的便携式阻抗测试仪

2021-06-30大连交通大学电气信息工程学院高玺皓金思辰王佳睿关钧洋

大连交通大学电气信息工程学院 高玺皓 宋 智 金思辰 王佳睿 关钧洋 刘 野

针对传统阻抗测试仪体积较大、价格昂贵等问题,提出了基于FFT算法的便携式阻抗测试仪。该测试仪采用STM32单片机及FPGA作为处理器,双路高速A/D采样芯片采集电压信号,通过FFT算法对采集到的信号进行处理得到阻抗相位,同时将电压信号分解为虚部和实部发送至单片机,对电压实部和虚部信号进行矢量计算得到阻抗模值。经过实验研究,该测试仪性能稳定,测量精度高。

1 系统结构

本文提出了基于FFT算法实现便携式阻抗测量仪,将矢量伏安法作为系统阻抗测量方法,并将其与FFT算法相结合,弥补了矢量伏安法不易测量相位的缺点,能够在较宽的频率范围内使被测信号幅值、频率对测量仪性能影响较小,具有较高的测量精度。

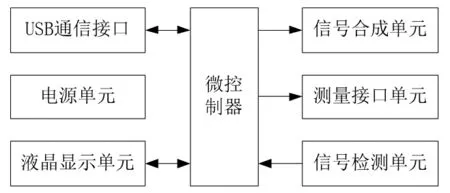

阻抗测试仪系统框图如图1所示,信号合成单元产生正弦电流信号,信号通过测量接口中的待测阻抗Zx和参考电阻Rx,信号检测单元对两者的电压进行采样。FPGA对采样信号进行FFT运算,得到两段电压的实部和虚部,并提取基波参数,实现相位测量。将FPGA处理得到的电压实部和虚部数据传送到单片机进行矢量伏安计算,最终将被测阻抗幅值及相位显示在液晶上。

图1 测量系统工作原理图

2 系统硬件设计

测试仪硬件可划分为系统控制模块、FPGA信号处理模块、采样模块、差分模块、信号发生模块等功能模块构成,硬件框图如图2所示。

图2 硬件框图

2.1 系统控制模块

选用STM32单片机作为控制芯片,对被测元件的阻抗值进行分析计算,根据测量值与初始设定的参数进行比较,将比较结果反馈到测量模块中选择合适R0达到最优测量状态。

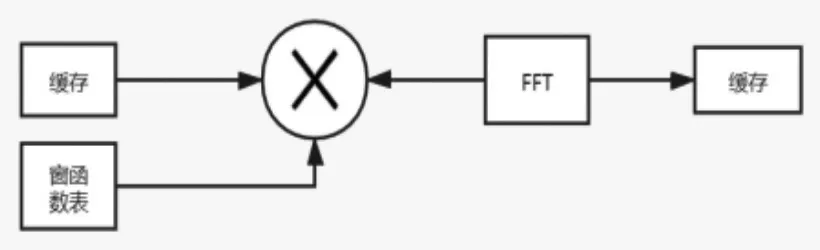

2.2 FPGA信号处理模块

FFT核转换数据长度选择512点,数据精度8bit,引擎结构选择单输出结构,引擎数为1,I/O数据流结构选择突发结构,采用两个双口RAM核,深度均为512,宽度均为8bit,分别存放FFT核的实部和虚部数据。该模块实现了信号数据的快速傅里叶变换,FFT算法流程图如图3所示。

图3 FFT流程图

2.3 差分采样模块

系统采用高速双通道A/D转换器AD9226作为采样芯片,采样时序通过FPGA产生。前级采用单端转差分芯片AD8138,其差分输出对平衡后级双通道ADC的差分输入起到重要作用。

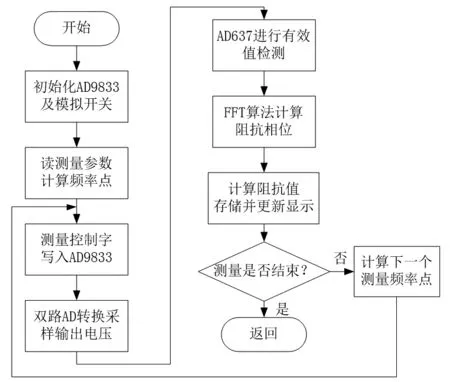

3 系统软件设计

软件流程图如图4所示,为防止单片机复位,单片机首先要关闭看门狗,然后进行时钟初始化以及各个子模块初始化。测量阶段中,首先执行键盘扫描子程序,设置信号发生器输出频率,通过FPGA驱动A/D芯片对信号采集,对离散序列进行FFT运算,根据测量结果调整R0,对测量结果进行修正,最终由液晶显示测量结果。

图4 软件流程图

4 实验测试

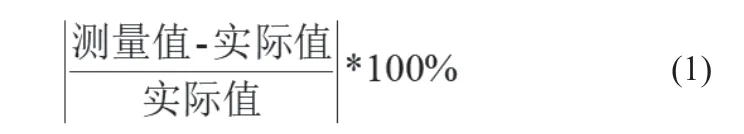

实验过程中正弦波信号频率设置为2kHz,幅度设置为2V,先对电阻进行测量,再对阻容串联进行测量,计算测量值与实际值之间的误差,并对误差进行分析。

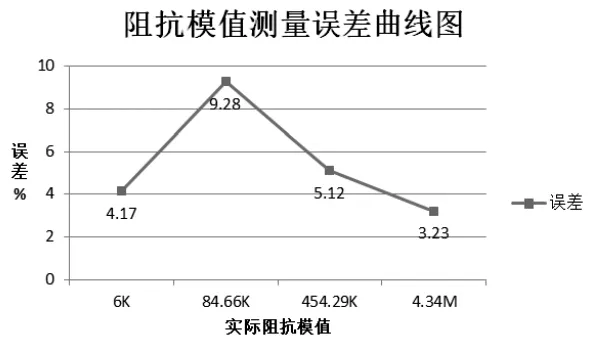

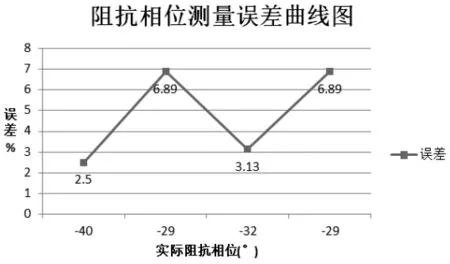

通过实验,测量结果如图5~图7所示。误差公式为式(1)所示:

图5 电阻测量结果

图6 电阻与电容串联模值测量结果

图7 电阻与电容串联相位测量结果

测量结果表明,电阻测量相对准确,大电阻测量精度小于1%,而在测量小电阻时,由于模拟开关的导通电阻相对较大,故小电阻的测量结果误差也相对较大。另外,元件的电阻值也会有一定的误差,尤其是电容的测量。结果表明,阻抗幅值误差小于10%,相位误差在2%~10%之间。

结论:以实现低成本、高性能、便携式阻抗测量仪为目的,采用高速A/D实现被测信号与参考信号的同步采样,提高测量速度;采用FFT算法,提取基波分量,实现精确的数字相位测量,能够在较宽的频率范围内使测试仪不受被测信号幅值和频率的影响,测量精度高。