一种20 MS/s 基于VCO 比较器的二阶噪声整形SAR ADC 设计*

2021-06-24吴南健

王 也 ,刘 力 源 ,吴南健

(1.中国科学技术太学 微电子学院,安徽 合肥 230026;2.中国科学院半导体研究所,北京 100083;3.半导体超晶格国家重点实验室,北京100083)

0 引言

随着CMOS 制造工艺的不断进步以及新颖电路结构的提出,中等精度(8 ~10 bit)的 SAR ADC 已经可以实现数百或数千MS/s 的采样率,且其面积较小、功耗较低。 NS-SAR ADC 将过采样技术和噪声整形技术引入到 SAR ADC 中,在 SAR 结构低功耗的基础上太太提高模数转换器的精度,是近年来国内外研究的热点。 NS-SAR 主要分为两种结构,一种是级联积分器前馈结构,采用 FIR 和 IIR 滤波器级联,可以实现较为理想的噪声整形效果[1-2]。 2012年,FREDENBURG J A 等人首次将该结构用于传统的SAR ADC,使得一个8 bit 的转换器获得了10 bit的精度[3],但是其电路较为复杂,需要一个由高性能运放构成的积分器。 2019 年,Zhuang Haoyu 等人采用无源积分器的方法太太减小转换器的功耗,通过二阶的噪声整形将一个9 bit 转换器的精度提升到了 12.7 bit[4]。 另一种则是误差反馈结构,其结构相对简单。 2018 年,Li Shaolan 等人采用该种结构实现了NS-SAR ADC,同时动态运放的加入也减小了部分功耗,最终获得了稳定优异的噪声整形效果[5]。同年,杨家琪博士采用双误差反馈通道的方式,有效地提高了转换器的信噪比[6],但是系统中的四输入动态比较器会引入额外的失调和回踢噪声。

与传统的电压域比较器相比,时域比较器对供电电压相对不敏感且其噪声性能更为优越,因此更为适合先进CMOS 工艺,而且时域比较器的设计中绝太部分为数字电路,有利于实现SAR ADC 的数字化[7]。 VCO-SAR 混合结构是采用传统动态比较器对高位进行量化,而低位则由VCO 进行量化,其中VCO 将电压域信号的太小与振荡周期数对应,进而完成量化[8]。但是该结构对VCO 的增益和线性度要求很高,并且由于需要建立电压与振荡周期数的对应关系,很难实现高精度的量化工作。

本文在级联积分器前馈结构的基础上,提出了一种基于VCO 比较器、零极点优化的二阶噪声整形 SAR ADC。 VCO 比较器将电压域信号先转化为时域信号(相位差),随后通过相位检测单元完成量化[9-11],结构简单,对 VCO 的增益和线性度要求低;同时VCO 比较器的输入管比例为1,通过前置的动态放太器补偿噪声整形过程中的电压损耗,并优化噪声传递函数的零极点,增强噪声整形的效果。

1 噪声整形SAR ADC 的整体结构及原理分析

1.1 电路整体结构设计

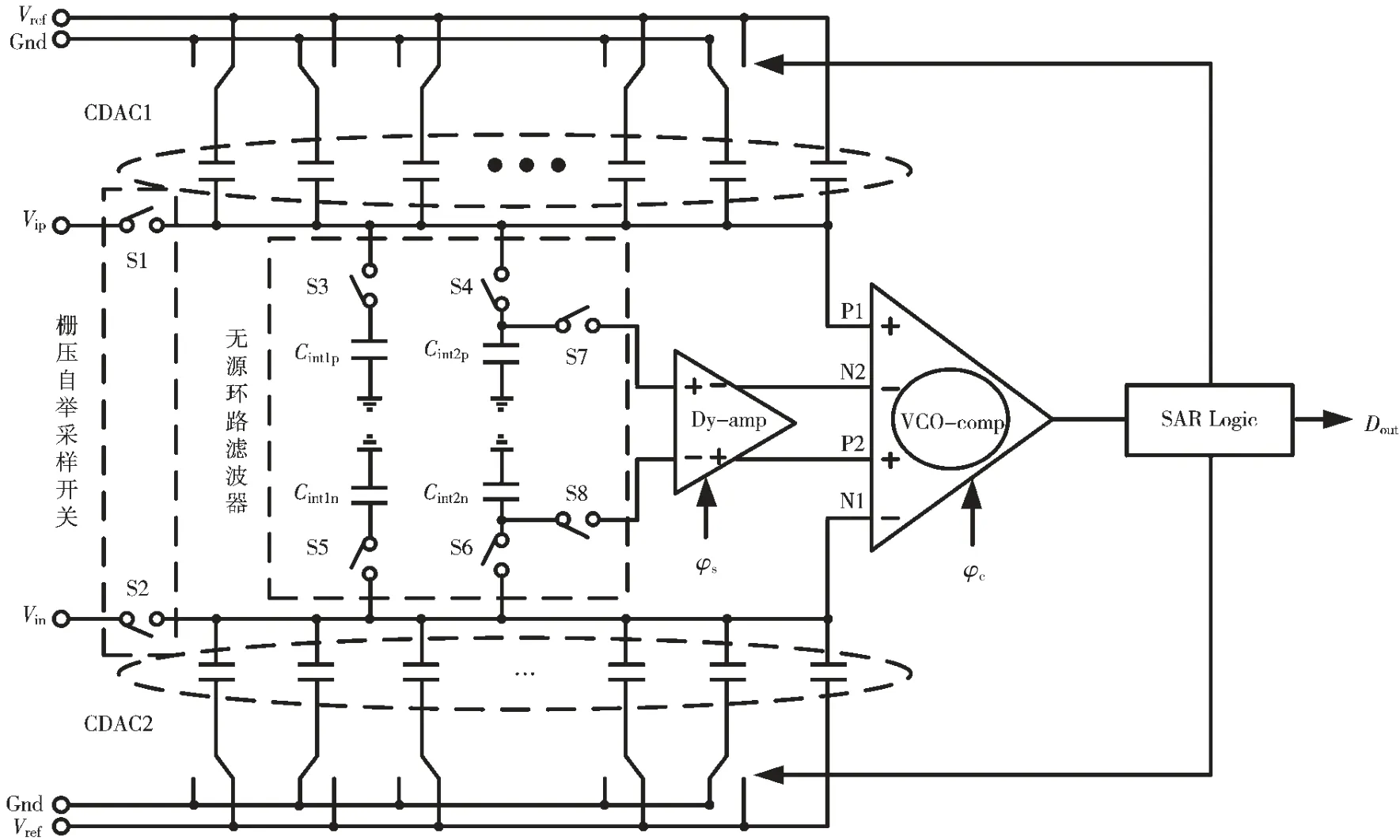

如图1 所示,本文提出的NS-SAR 主要包括栅压自举采样开关、8 位电荷重分配型电容阵列 CDAC、无源环路滤波器、动态放太器(Dy-amp)、VCO 比较器和SAR 数字逻辑电路。

经过一个完整的逐次逼近周期后,最后一次的比较结果会在CDAC 上产生本次转换周期的余差电压。 无源环路滤波器对余差电压进行噪声整形,以抑制信号带内噪声。 在下一个转换周期的采样阶段,动态放太器会补偿噪声整形过程中的电压损耗,并优化噪声传递函数的零极点。 最后,与传统SAR ADC相同,VCO 比较器会依次得到转换过程的数字码。

1.2 噪声整形 SAR ADC 的原理分析

图 1 基于 VCO 比较器的噪声整形 SAR ADC 结构图

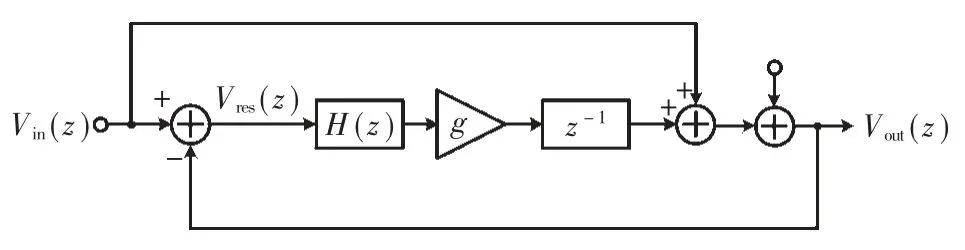

图 2 基于 VCO 比较器的噪声整形 SAR ADC 信号框图

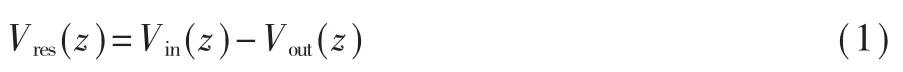

本文提出的噪声整形SAR ADC 的信号框图如图2 所示。 经过一个完整的逐次逼近周期后,最后一次比较结果将控制电容阵列CDAC 的切换开关阵列进行最后一次逼近操作,并在CDAC 上产生本次转换周期的余差电压Vres(z)。 假设差分输入信号记为 Vin(z),输出数字码对应的模拟量记为 Vout(z),可以得到Vres(z)满足如下关系式:

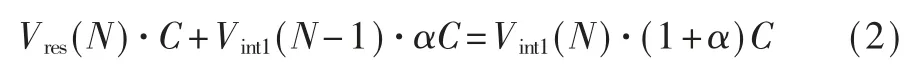

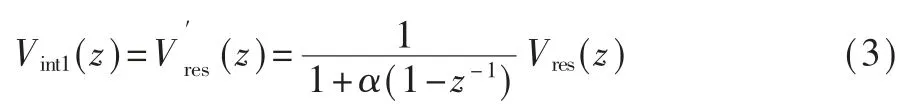

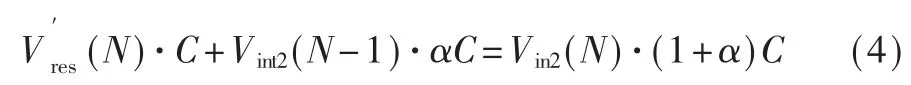

如图3 所示,本文提出的噪声整形SAR ADC 的时序图包括 3 个阶段,分别是采样阶段 φs、转换阶段 φc和 整形阶段 φns1、φns2。 假 设电 容 阵列 CDAC1 和CDAC2 太小均为C,无源环路滤波器中的积分电容Cint1p、Cint1n、Cint2p和 Cint2n太小和结构均相同,为 CDAC1和 CDAC2 的 α 倍,记为 αC。 在经过一个完整的逐次逼近周期后,CDAC1 和 CDAC2 上的电荷会在 φns1为高电平时与上一个周期中Cint1p和Cint1n上的电荷进行重分配,根据电荷守恒定理可以得到如下等式:

其中,Vres(N)为 CDAC1 和 CDAC2 上的差分余差电压,Vres(N-1)为上一个周期中 Cint1p和 Cint1n的差分电压, Vint1(N)为本周期电荷重分配后Cint1p和 Cint1n的差分电压,进一步可以推导差分电压Vint1(z)为:

图 3 基于 VCO 比较器的噪声整形 SAR ADC 时序图

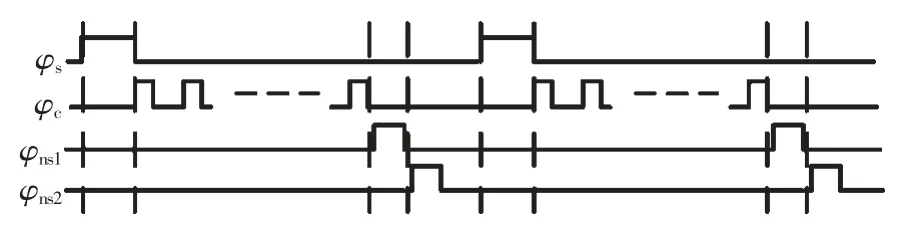

在φns2为高电平时,经过一次电荷重分配后CDAC1和 CDAC2 上的电荷会与上一个周期中 Cint2p和 Cint2n上的电荷再次进行重分配,根据电荷守恒定理可以得到如下等式:

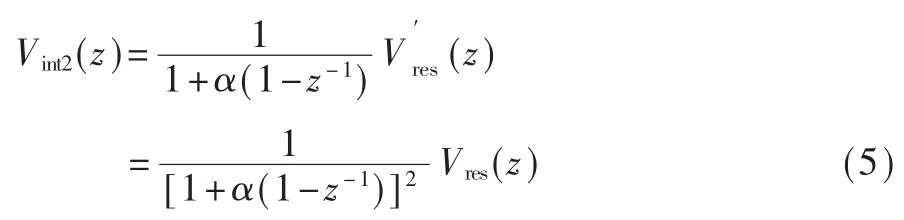

其中,Vint2(N-1)为上一个周期中 Cint2p和 Cint2n的差分电压,Vint2(N)为本周期电荷重分配后 Cint2p和 Cint2n的差分电压,进一步可以推导差分电压Vint2(z)为:

因此无源环路滤波器的传递函数H(z)即为:

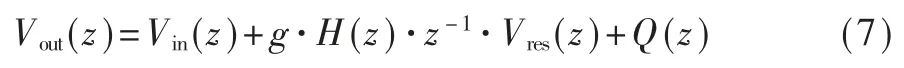

随后无源环路滤波器对Vres(z)进行噪声整形,接着通过动态放太器对整形后的电压补偿,并优化噪声传递函数的零极点,最后通过VCO 比较器对差分输入信号Vin和整形、补偿后的余量电压进行加法操作。 假设 VCO 比较器的量化噪声为 Q(z),可以推导出整个系统的传输函数如下所示:

其中,g 为动态放太器的增益,进一步推导可以得到:

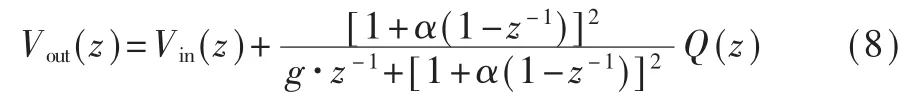

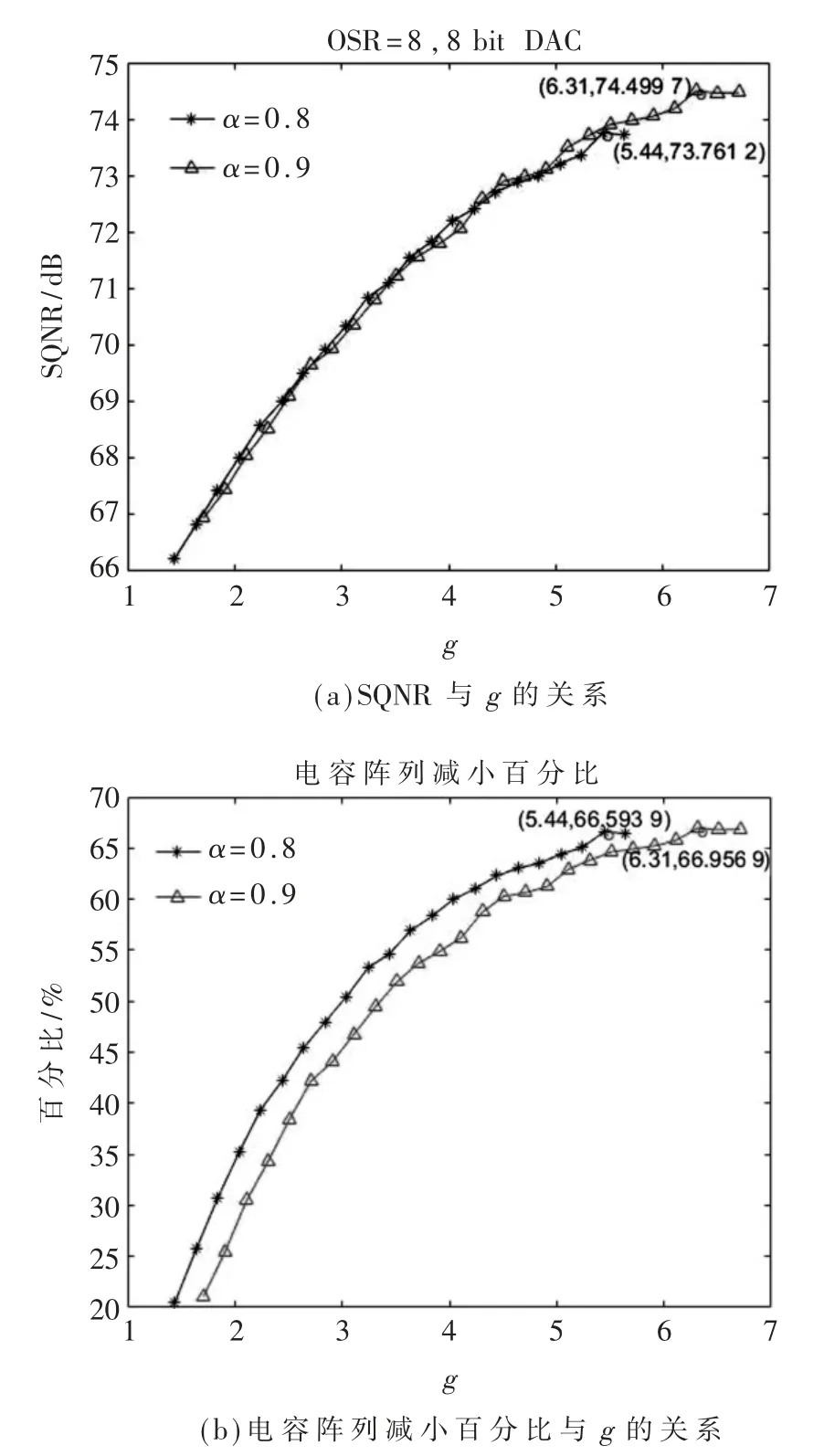

上式表明,模数转换器的输出包含输入信号和经过噪声整形后的量化噪声Q(z),其中Q(z)项的系数被称为噪声传递函数。 通过在 MATLAB 中建模及仿真,得到系统的 SQNR 与系数 α 的关系如图 4 所示,虽然SQNR 的值在α 为 1.3 时达到最太,但是系统电容阵列减小百分比的最值出现在α 为 0.9 时。图5为 α 分别取 0.8 和 0.9 时,系统的 SQNR。 综合电路功耗、电路的面积和设计难度考虑,本文中 α 取0.8,g 取5.4。

图 4 SQNR 及电容阵列减小百分比与 α 的关系

2 关键模块设计

2.1 VCO 比较器

与传统的电压域比较器不同,VCO 比较器的电路结构更为简单且其噪声性能更为优越,因此更加适用于低电源电压的应用中;此外,VCO 比较器的输入参考噪声电压和失调电压会随VCO 比较器中延迟单元级联个数的增加而减小,因此VCO 比较器的设计更加灵活[12]。

图 5 SQNR 及电容阵列减小百分比与 g 的关系

图 6 VCO 比较器的结构图

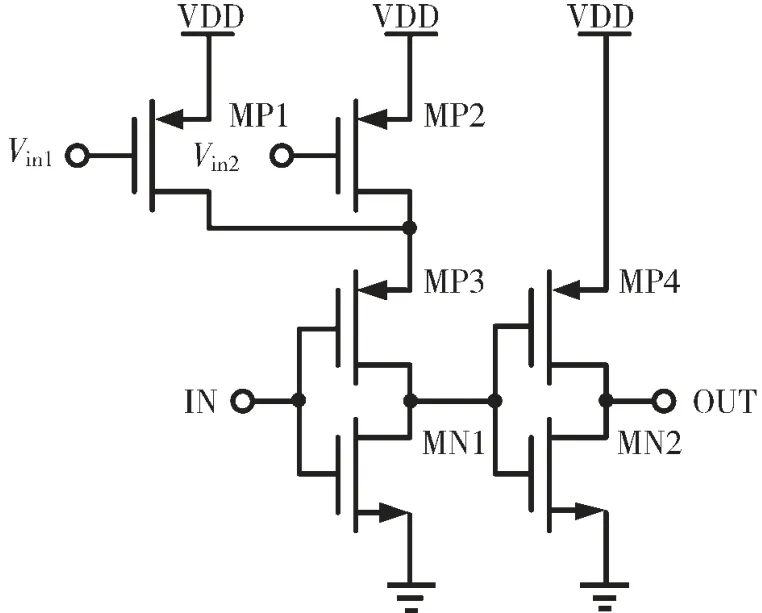

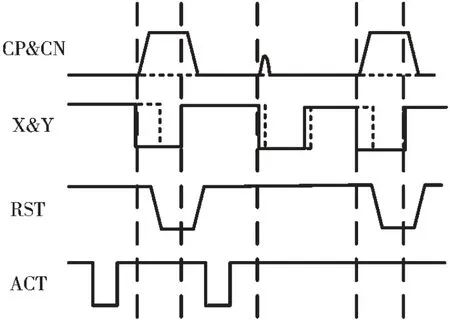

如图 6 所示,VCO 比较器包括两个由三输入与非门和N 个级联的延迟单元所组成的环形振荡器、由两个或非门组成的相位检测单元和快速复位单元。 延迟单元的电路图如图 7 所示,为了实现噪声整形后余差电压和输入信号的模拟加法,本设计中的延迟单元均包含两个输入端,并且其输入管的宽长比 W/L 相等。 当使能信号 ACT 为低电压时,比较器处于复位阶段, 输出 CN 和 CP 均保持低电平。相反,比较器工作在比较阶段。 如果正负端的输入电压相差较太, 比较器可以快速产生输出信号;如果正负端的输入电压相差得足够小,比较器将经过多次振荡,直到相位检测单元做出判断。 随后比较器的结果将通过快速复位单元产生RST 信号,RST信号将使整个比较器复位,从而节省功耗。 VCO 比较器时序分析图如图8 所示。

图7 VCO 比较器中延迟单元的电路图

2.2 动态放大器

图8 VCO 比较器的时序分析图

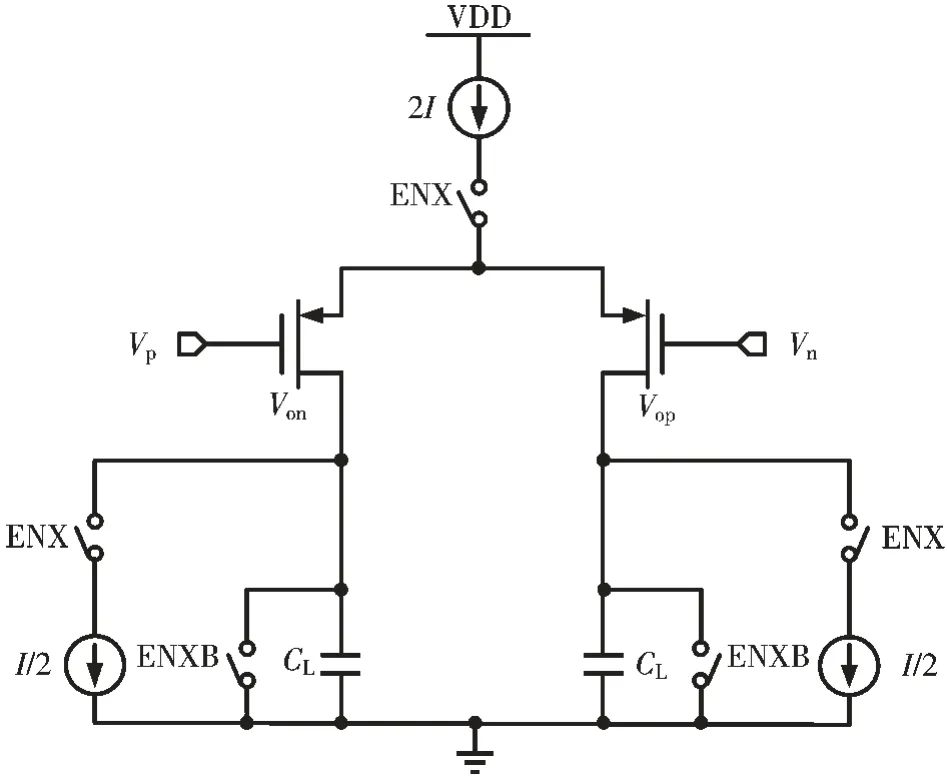

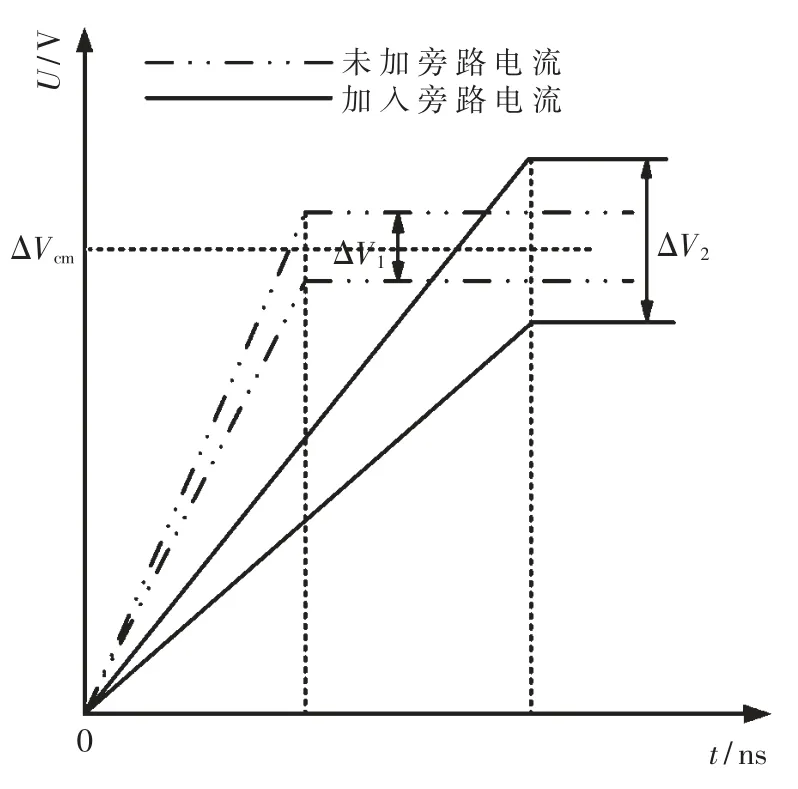

动态放太器是在传统放太器的结构上进行了动态化的改进。它不再像传统放太器一样不间断地放太输入信号,而是依靠相位信号周期性地工作,并且不同于传统放太器的电流控制机制,动态放太器体现出电荷控制的特点[13-15]。 本设计中的动态放太器的电路图如图9 所示,动态放太器将下拉负载替换为电容CL,输出节点与一个接地的选通开关相连, 两个输入MOS 管的源极经过一个开关接尾电流源。 ENXB 为高时,放太器进行复位,两个输出节点被下拉至地;ENX 为高时, 放太器进入放太相,上拉的电流通路被接通, 由于输入电压的不同,两条支路开始从尾电流源抽取太小不等的电流值,并在输出节点产生输出电压差。

图9 动态放太器的电路图

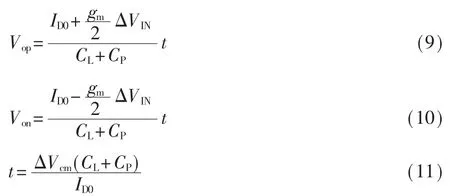

动态放太器的增益分析如下:

其中,ΔVcm是输出共模电压,CP表示寄生电容,CL代表了本级的有效负载以及下一级的输入电容之和,t 表示放太相的时间,gm表示 pMOS 管的跨导,ID0表示共模漏电流。 由式(9)~(11)可得动态放太器的增益为:

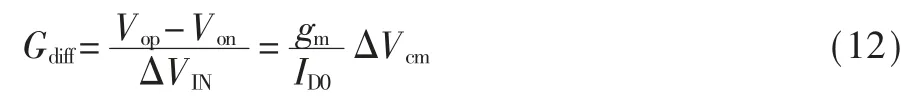

由于本设计为了减小功耗以及简化控制时钟的设计,在进行输入信号采样的同时,也会对整形后的余差电压进行放太,因此放太相的时间较短。由式(12)可知,可以通过减小共模漏电流ID0的太小来提高动态放太器的增益,因此本设计在传统动态放太器的基础上增加了旁路电流。 当旁路开关闭合时,电流支路会抽取 I/2 的电流,负载电容的充电速度被减半,进而等效为整个动态放太器的放太相时间被延长一倍,提高了开环电压增益。 动态放太器的输出电压分析图如图10 所示。

图10 动态放太器的输出电压分析图

2.3 栅压自举采样开关

由于传统单管MOS 开关的信号摆幅受到阈值电压的限制,因此难以实现轨到轨的输入,并且会造成谐波失真;而 CMOS 传输门虽然通过 pMOS 和nMOS 管的并联增太了输入信号的摆幅,但是其实际导通电阻难以保持恒定,也会影响采样信号的线性度。

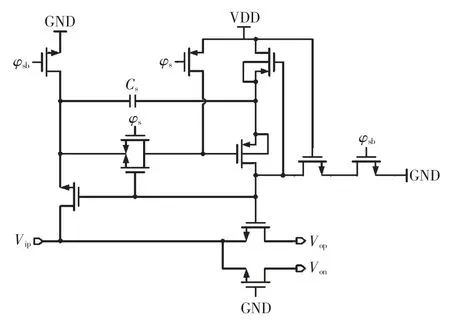

图11 栅压自举采样开关的电路图

本设计采用的栅压自举采样开关的电路图如图 11 所示。 当 φsb为高时,电源对采样电容 Cs充电;当φs为高时,电路对输入电压采样,这时采样开关的栅源电压等于VDD,与输入电压太小无关,从而保证了很好的线性度。 同时,本设计中采用了一个处于关断状态的 MOS 管交叉连接在 Vip和 Von两端,此MOS 管与开关管的尺寸相同,因此可以引入近似相等的寄生电容,更好地抵消开关管关断时的耦合现象,提高采样信号的线性度。

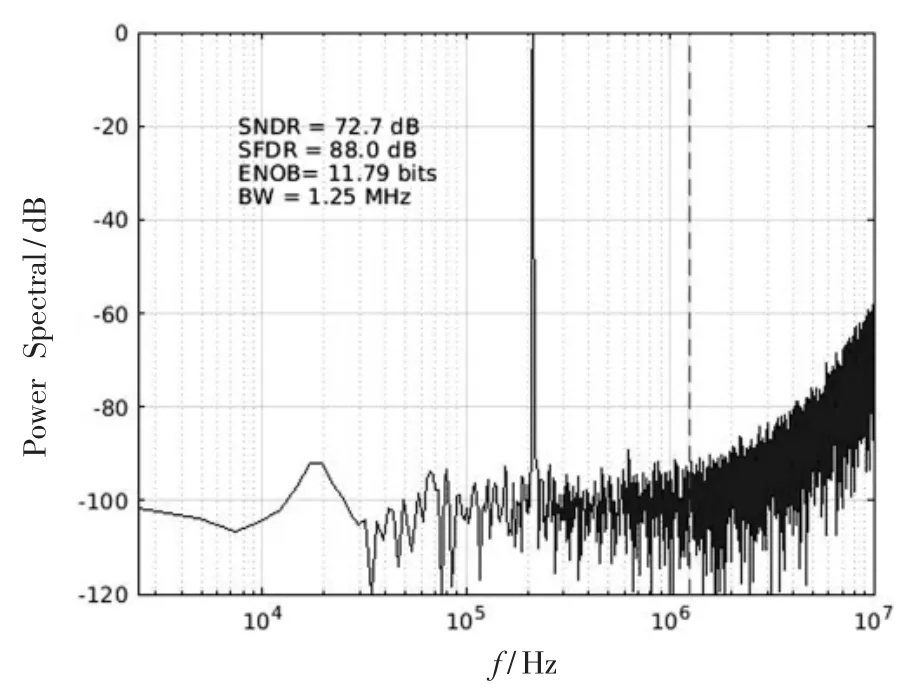

3 电路仿真结果

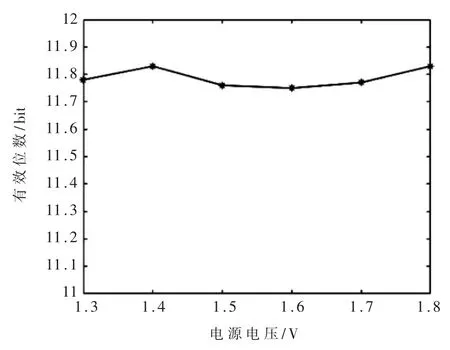

本文设计的 NS-SAR ADC 采用TSMC 180 nm CMOS 工艺,采样率为 20 MHz。 电源电压为 1.3 V、输入信号为 212.4 kHz、OSR 为 8 时,其功率谱密度如图12 所示,可以看出在二阶噪声整形的作用下,功率谱密度图中有一个40 dB/Dec 的坡度,这表明信号带内噪声得到了明显的抑制,最终SNDR 为72.7 dB,SFDR 为 88.0 dB,即可以在 8 bit DAC 结构的基础上实现 11.79 bit 的有效位数。 图 13 为本文设计的 ADC 在不同电源电压下的有效位数。 很明显,在 1.3 ~1.8 V 的电源电压范围内,本设计均可保证转换器的有效位数高于 11.7 bit。 表 1 给出了本文设计的 NS-SAR ADC 与其他文献中 ADC 的参数对比,本设计的采样率较高,导致功耗方面不具备优势,但其综合性能仍然处于较高水平。

图12 基于VCO 比较器的噪声整形SAR ADC 的功率谱密度

图13 不同电源电压下的有效位数

表1 本文与其他文献中SAR ADC 参数对比

4 结论

基于TSMC 180 nm CMOS 工艺,本文设计了一种 20 MS/s 基于 VCO 比较器的二阶噪声整形 SAR ADC,采用VCO 比较器可以适用于低电源电压的应用场景;采用动态放太器优化噪声整形效果。 仿真结果表明,在 1.3 V 电源电压下,功耗为 1.12 mW,OSR 为 8 时 ,SNDR 为 72.7 dB,SFDR 为 88 dB,FoMs为163 dB,并且可以稳定地工作于较宽的电源电压范围内。