基于FPGA的出租车计费系统设计

2021-06-17徐晶晶杨涛指导教师

徐晶晶,杨涛(指导教师)

(电子科技大学电子科学与工程学院,四川成都,611731)

0 引言

FPGA(Field Programmable Gate Array)是在PAL、GAL等可编程器件的基础上进一步发展的产物。FPGA由可编程逻辑功能块、片内互联线、输入输出块构成,通过修改布线实现可编程。可使用框图或者Verilog HDL来设计FPGA,Verilog HDL 推出已经有 20 多年,拥有广泛的设计群体,成熟的资源比 VHDL丰富,因此本次设计采用Verilog HDL 语言。而出租车是日常出行中必不可少的交通工具,基于出租车的附属品市场前景也是十分广阔。本文基于FPGA设计模拟了一款出租车计费系统,具有开发周期短,设计灵活等优势[1]。

1 FPGA 片内逻辑总体结构设计

■1.1 开发工具

本次设计中 FPGA 型号为 Xilinx公司的 spartan-6 系列的 xc6slx-2ftg256 型号。设计开发工具选用 ISE14.7,针对FPGA 设计的功能和时序仿真,选择 Mentor 公司的Modelsim 仿真工具。

■1.2 总体架构

出租车计费系统的实现框图如图1(a)所示[2],RTL顶层原理图如图1(b)所示,上位机发送指令模拟汽车启动、停止、行驶公里数、等待时间的操作,通过串口将指令发送至设计的出租车计费系统,而后再通过串口将总计费用返回至上位机。

■1.3 系统规范

(1) 上位机实现模拟功能:汽车启动、停止、公里计数、等待时间计数。

(2) 具体计费方式:

里程<3公里:费用=6元;3公里<里程≤19公里:费用=6+(里程-3)*2+等候时间*等候单价1;里程>19公里:费用=里程*里程单价(2)+等候时间*等候单价1。

(3) 费用能够通过上位机显示[3]。

2 模块具体划分

出租车计费系统分为五个模块,分别为串口接收模块uart_rx、里程计数模块mileage_counter、等待时间计数模块wait_time、计费模块charge、串口发送模块uart_tx。

图1

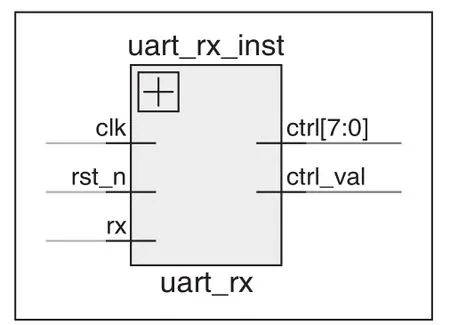

■2.1 串口接收模块uart_rx

串口接收模块负责接收上位机传送的控制指令[4],其RTL原理图如图2所示。表1给出了串口接收模块输入输出端口定义。

图2

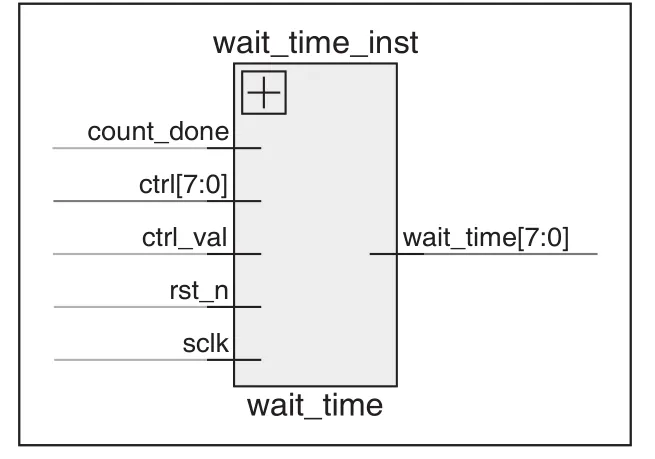

表1 串口接收模块输入输出端口定义

串口接收模块的仿真结果如图3所示。

图3

通过串口接收模块仿真波形可以看出uart_rx模块接受控制命令ctrl(0:启动;1:停止;2公里数;3:等待时间数)传送至其他模块。本次模拟的为行驶5公里,等待2个时间单位。

■2.2 里程计数模块mileage_counter

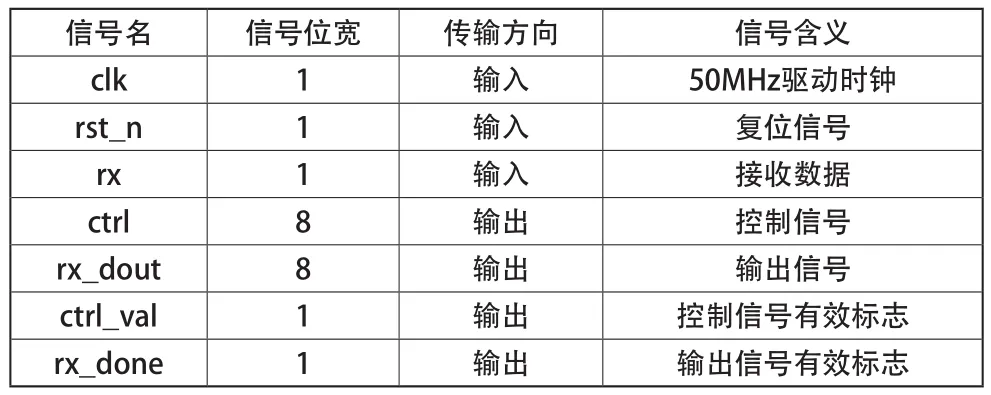

里程计数模块负责计算行驶里程数,其RTL原理图如图4所示。表2给出了里程计数模块输入输出端口定义。

图4

表2 里程计数模块输入输出端口定义

里程计数模块仿真波形如图5所示。

图5

通过里程计数模块仿真波形,可以看出在计费时间内(count_en=1),最终的里程数(kilo_out)为5公里。

■2.3 等待时间计数模块wait_time

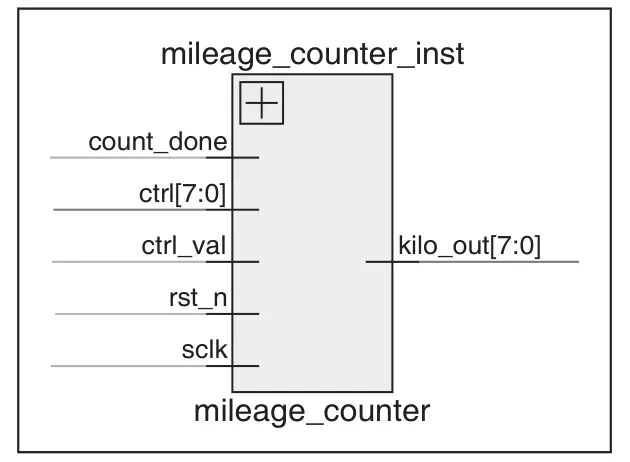

等待时间计数模块负责计算等待时长,其RTL原理图如图6所示。表3给出了等待时间计数模块输入输出端口定义。

图6

表3 等待时间计数模块输入输出端口定义

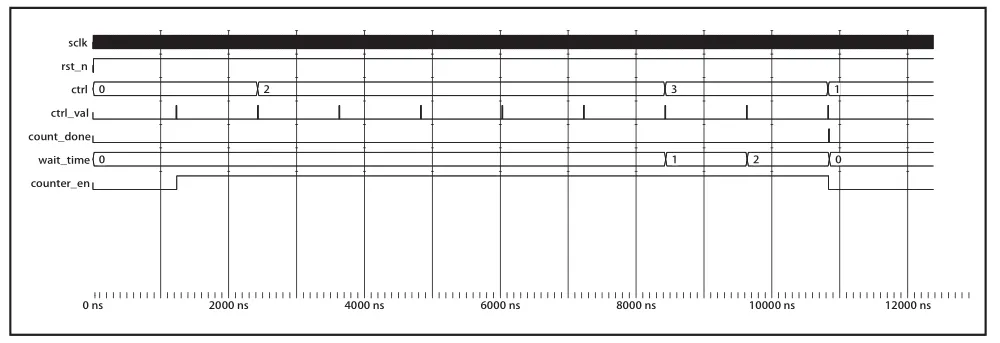

等待时间计数模块仿真波形如图7所示。

图7

通过等待时间计数模块仿真波形,可以看出在计费时间内(count_en=1),最终的等待时间(wait_time)为2。

■2.4 计费模块charge

计费模块负责计算总体开销[5],其RTL原理图如图8所示。表4给出了计费模块输入输出端口定义。

图8

表4 计费模块输入输出端口定义

计费模块仿真波形如图9所示。

图9

通过计费模块仿真波形可以看到总公里数(kilo_out)、等待时间数(wait_time)、产生费用(cost)。通过仿真结果可以看到计费截止时(count_done信号为1),产生的总费用为12元。

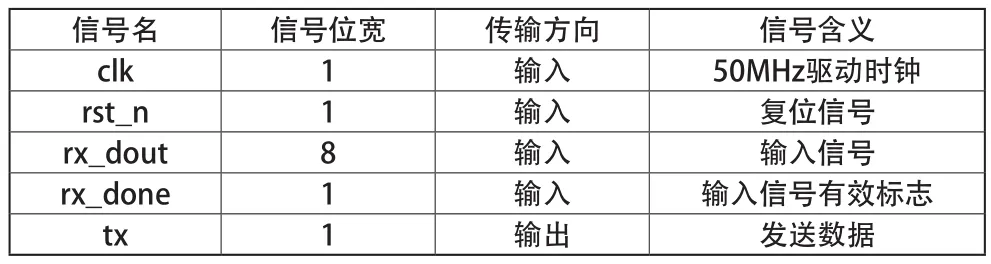

■2.5 串口发送模块uart_tx

串口发送模块负责将计费模块计算出的总体开销返回给上位机,其RTL原理图如图10所示。表5给出了串口发送模块输入输出端口定义。

图10

表5 串口发送模块输入输出端口定义

串口发送模块仿真波形如图11所示。

图11

通过串口发送模块的仿真波形可以看出uart_tx模块将产生的总费用(rx_dout_reg)传送回上位机。

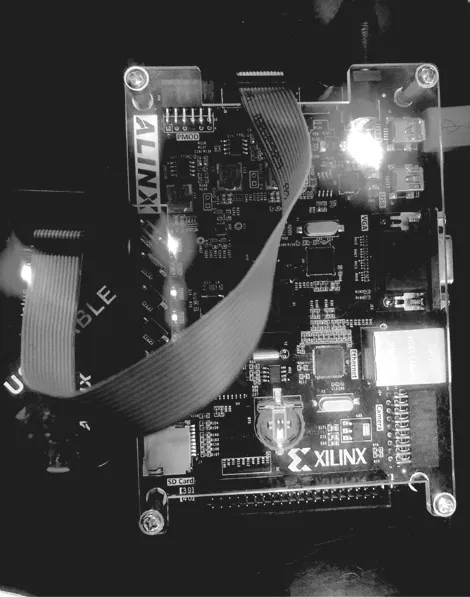

3 验证试验

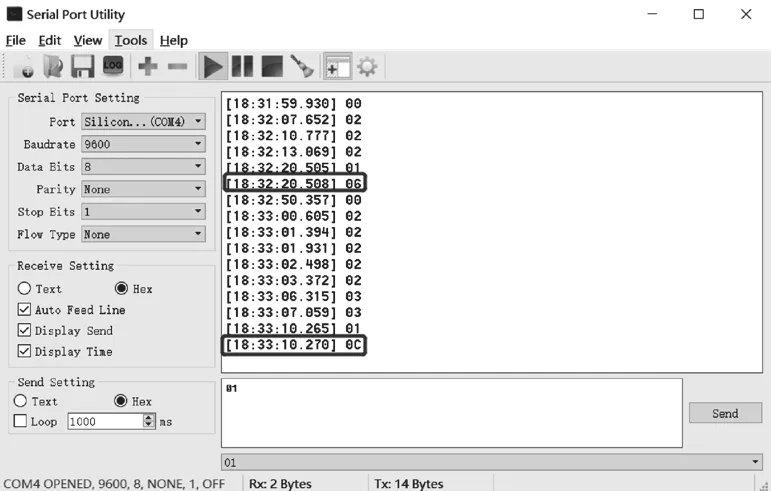

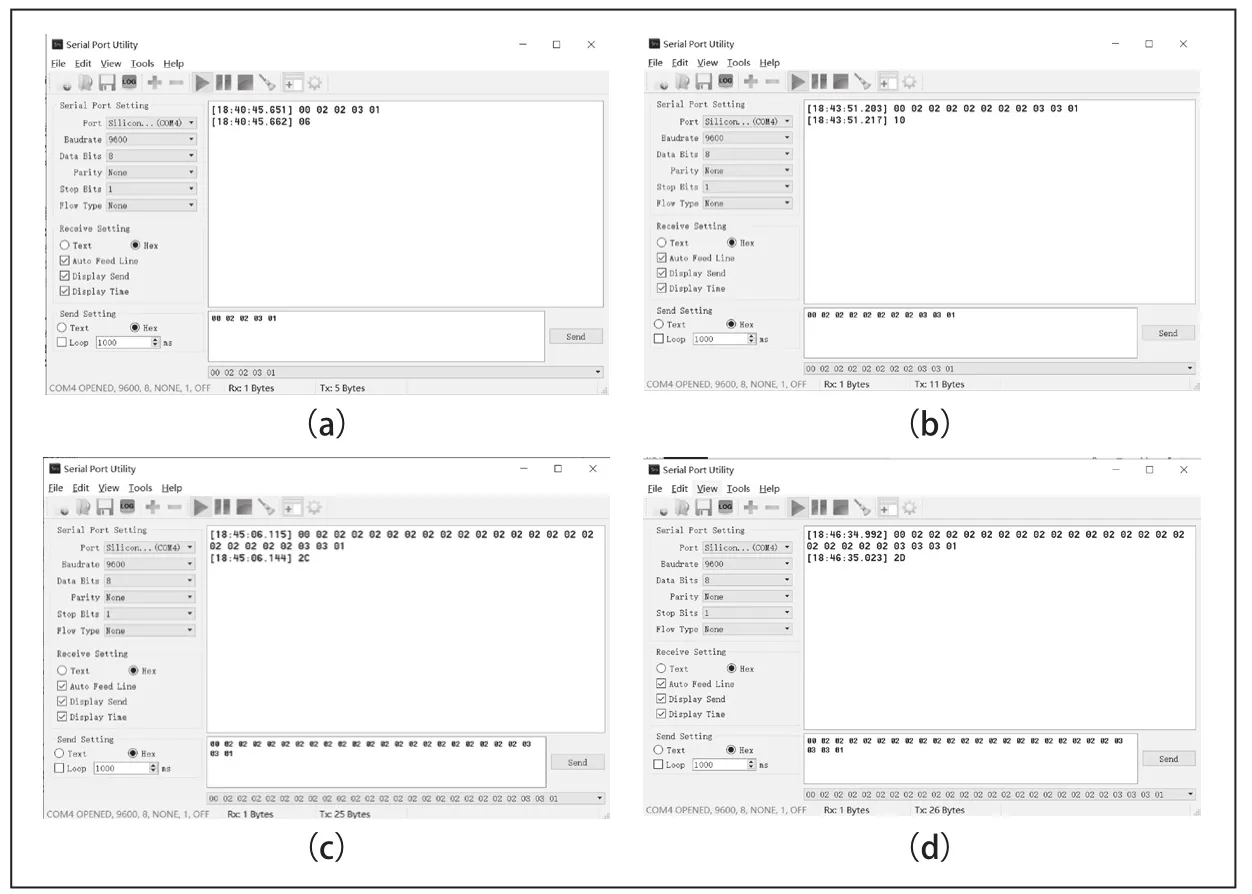

我们连接好开发板如图12所示,将bit文件下载至开发板,而后将USB数据线连接至USB转串口芯片。打开上位机软件(友善串口助手),通过上位机发送控制信号(0:启动;1:停止;2公里数;3:等待时间数),可以通过上位机软件看到返回的产生费用。

如:行驶3公里(控制信号为:00 02 02 02 01)返回的数据为06,表示产生费用为6元;行驶5公里,等待时间为2,(控制信号为:00 02 02 02 02 02 03 03 01),返回的数据为0C,表示产生费用为12元。验证结果如图13所示。

图13

此外本文还验证了一些其他数据,验证结果如图14所示。

图14

4 结论

出租车计费器在日常出行中不可缺少,本文利用FPGA实现了出租车计费系统。出租车计费系统利用Verilog语言设计出来的出租车计费器系统实现了串口接收模块uart_rx、里程计数模块mileage_counter、等待时间计数模块wait_time、计费模块charge、串口发送模块uart_tx。完成了通过控制信号模拟汽车启动、停止、里程计数与等待时间计数,最终将总计费用通过上位机显示了出来。通过FPGA来开发数字电路,缩短了设计时间,减少了PCB面积,具有很强的灵活性,因此具有很大的应用前景。