基于电流舵的高精度低功耗13-bits DAC设计

2021-06-16谢雪丹张文芳刘佳庆

谢雪丹 张文芳 刘佳庆

(山西能源学院 山西省晋中市 030600)

数模转换器(Digital-to-Analog Converter,简称DAC),顾名思义,是集成电路领域中连接数字电路和模拟电路的桥梁,亦是数字电路系统与外部模拟信号世界间交换信息的主要渠道。利用DAC,可以将离散的数字信号转化为连续的模拟信号,其在现代5G 通信、高速雷达探测、医疗通信系统及物联网等信号处理过程中扮演着不可或缺的角色,重要性不言而喻。

目前,随着集成电路技术的飞速发展,各电子技术应用领域对DAC 的指标性能也提出了更加苛刻的要求,研究和设计低功耗、宽范围、高精度、高速率的数模转换器具有十分重要的实践意义。传统的DAC 结构有权电阻结构、R-2R 结构、电荷分布结构等;一般地,电压型DAC 多用于低速转换器内,且电阻结构中电阻的数量会随着转换位数的增加而带来版图面积的消耗。因此,在高速、高精度的应用需求下,设计一款性能优越的电流舵型DAC 将对通信领域起到推动型的作用。

1 电流舵DAC整体架构

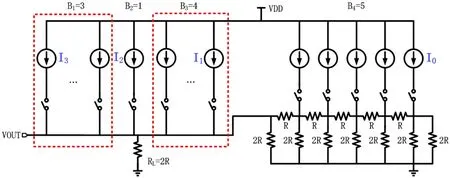

高分辨率的DAC 通常采用多变量、多段位、多模式的组合结构。本文所设计的13-bits 电流舵DAC 采用改良后的电流模分段式控制方法,选择四个子模块互联构成,子模块间的电流满足权重关系,段内各支路电流源大小相等。分配四段位的段内位数分别为5bit,1bit,3bit,4bit,最低位单位电流源在输出电阻上产生的调节电压为0.15mV,满量程电压调节范围为0~1.2V。电路整体架构包含基准-偏置电路、电流源阵列、开关驱动电路、温度计译码电路等。

13-bits DAC 电路结构简图如图1 所示。

2 电路设计

2.1 低段位5-bits DAC

本次DAC 设计中单位电流支路采用压控电流源方案,产生的两路偏置电压分别加在MOS 管栅极产生相应的设计电流。低五位DAC 采用R-2R 结构,其中R 为基本的单位电阻参数。

当开关全部断开时,在VOUT端到地等效为3 个2R 电阻并联,此时流过最左端R 电阻的电流为零。当D0为1 时,最低位支路中的电流I0将在R-2R 电阻网络中进行分配,最低位支路节点处流过的电流为I0/3,之后R-2R 网络对该级电流逐级1/2 衰减。因此,低位的I0/3 电流首先在第一个横向电阻R 上流过,当经过第二个横向电阻R 时,电流开始逐级递减1/2,经过四级横向电阻1/2 分流后到达输出端,最终的输出电流为

2.2 段间电流模块

整个DAC 系统为线性系统,输出电压为多个激励信号作用的线性叠加,即可分开计算,并统一作线性求和处理。

段间关系示意图如图2 所示。

设R-2R 相邻段(4bits)的单位电流为I1,则产生的输出电压为:

当外部电流源输入全部为0,仅R-2R 产生激励作用,则此时的等效电阻为根据段间权电流的匹配关系,可知当且仅当R-2R 的最高位电流开关打开时,产生的输出电压应为邻近段位电流单独激励时产生输出电压的一半,即满足:

由此可得段间子模块的单位电流大小关系为:

图1:13-bits DAC 电路结构简图

图2:段间关系示意图

图3:偏置电路原理图

图4:开关驱动电路原理图

图5:单位温度计译码模块

图6:仿真电路图

图7:13-bits DAC 动态仿真输出波形

在此结构中,提高电流源精度和段间电流的匹配度对DAC 的整体性能十分重要。

单位电流源参数如表1 所示。

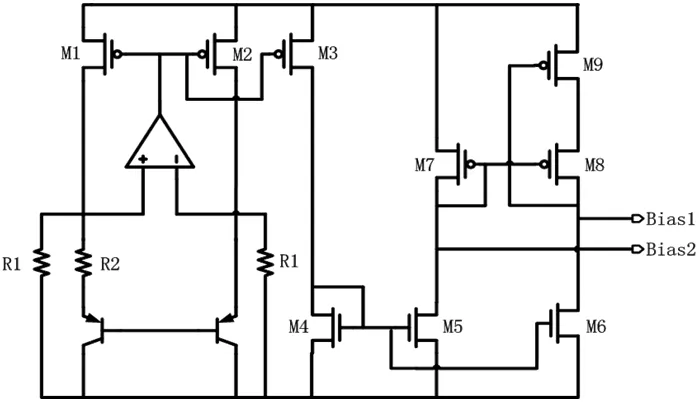

2.3 基本偏置电路

偏置电路中的电压主要为单位电流元中的压控管产生偏置电压,以提供精准的电流,本次设计基准电路温漂系数约为10ppm,之后通过电流转电压结构以及宽摆幅的电压偏置结构产生偏压Bias1 与Bias2,为后续DAC 基本电流单元支路提供稳定偏置电压。

表1:单位电流源参数

表2:DAC 各权位静态仿真值

图8:高段位波形动态性能对比

偏置电路原理图如图3 所示。

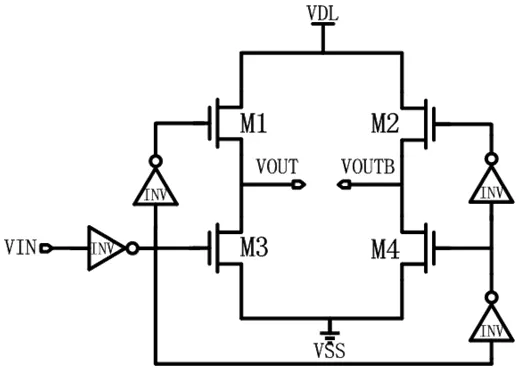

2.4 开关驱动电路

本文中采用的开关管电路通过合理设置开关控制信号的交叉点电压可以有效减小毛刺的发生,使电路更加稳定。输入信号通过反相器整形控制NMOS 管,同之前原理相同,对OUT 端与OUTB 端保持充放电时间不一致,于是可将两管同时导通时交叉点的电压下调,保证两个差分管在同一时刻保持全部导通或截止状态,避免一开一闭的情况引起随机大电流,影响DAC 性能。

开关驱动电路原理图如图4 所示。

2.5 温度计译码电路

在分段式电流舵DAC 设计中,高位输入码一般不直接控制电流源阵列,而是通过温度计译码电路转换成相应的温度计码,每个温度计码再通过开关驱动电路控制单独的电流源支路。

单位温度计译码模块如图5 所示。

3 仿真结果

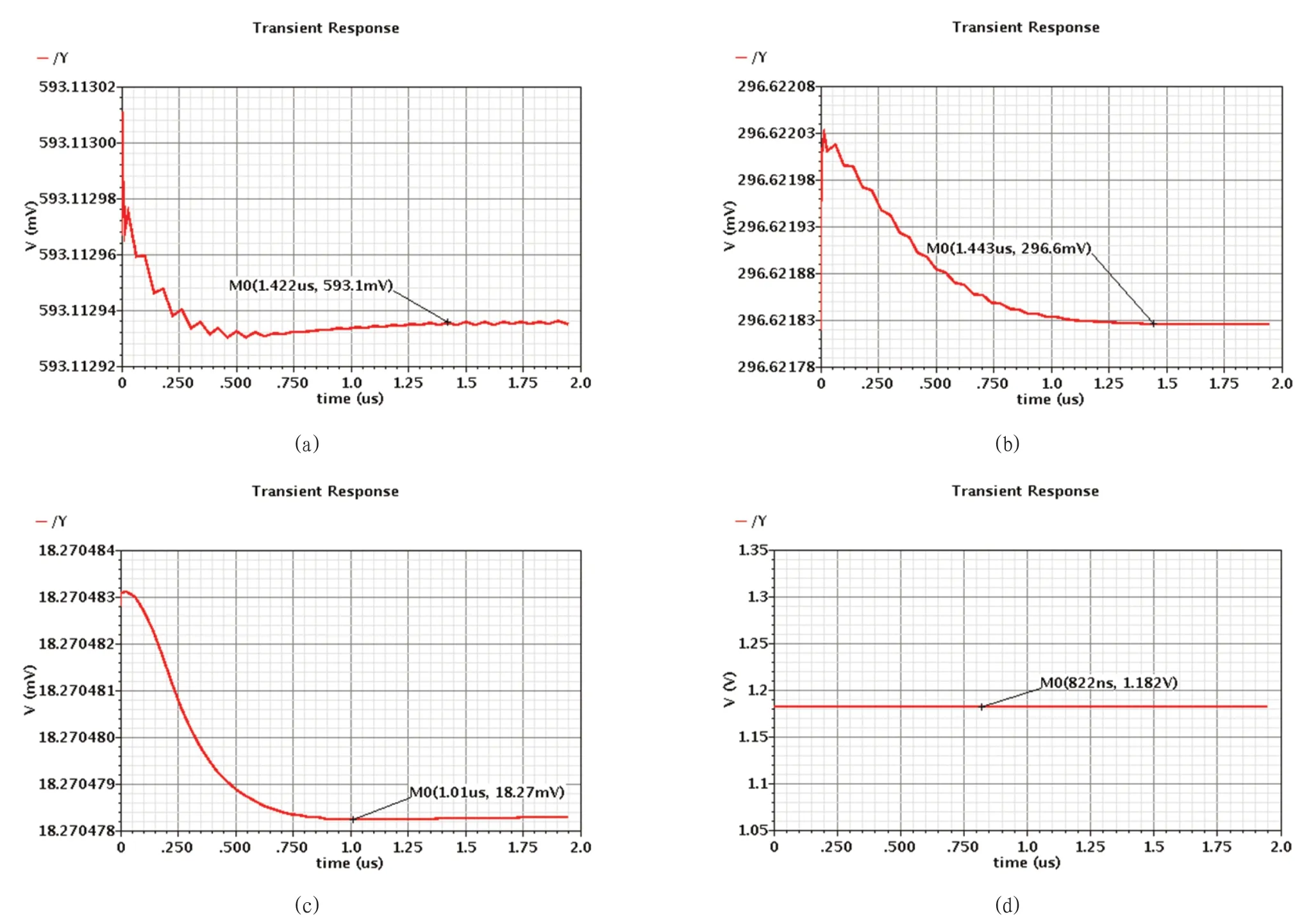

将所设计的具体电路在Cadence 软件中进行搭建,得到的电路原理图如图6 所示。电路整体分为基准-偏置电路、温度计码模块电路、开关电压整形电路、四部分单位电流元电路,其中各部分单位电流元采用同尺寸MOS 管成比例扩大,输入数字信号为D0-D12,输出模拟信号为Y。

图9:DAC 静态输出波形图

基于电流舵的13-bits DAC 动态性能仿真结果如图7 所示,满量程波形如图7 所示,蓝色线条为理想状态下的数模转换器模型输出波形,对应红色线条为本文涉及的13-bit DAC 的输出波形,可看到两条波形整体拟合度较高,但红色波形产生的毛刺较多。

由各段位波形放大后观察,本次设计的DAC 步长变化较为均匀,阶梯状变化比较明显;将各段位放大进行对比分析,对于高段位而言,以上情况并不太理想,出现实际波形与理想波形稍有偏差的现象,接近满量程时,这个差值显得更为明显。高段位波形动态性能对比如图8 所示。

完成DAC 动态性能仿真后,为了再次验证其基本功能,对电路进行了静态性能的仿真。静态性能下不考虑毛刺的产生,输入信号直接由直流电平进行控制,测试输出信号电压值,当每次仅打开一位信号时,其输出的电压值满足权位比重,符合要求。

DAC 各权位静态仿真值如表2 所示。

输出的静态波形主要有以下几种情况,图9(a)-(c)为输出均为有抖动的情况,输出的电压会有上下的波动,约为10 个uV,总体比较输出电压较稳定,符合要求;图9(d)为满量程时的静态输出电压,由图可见为1.182V,同动态性能输出一致。

4 结论

本文采用了电流舵段间组合的方法完成了一种数字模拟转换器的电路设计,所设计的DAC 共有13 位数字输入端,输出的模拟电压量程为0~1.18V,可对特定需求的电路进行偏置电压的调节,调节步长约为0.133mV,电路总功耗为2.34mW。此外,可以通过改变电路中R-2R 结构中的单位电阻大小,完成输出电压范围的调节,具有一定的实用性。通过对所设计的DAC 进行前仿验证,其静态性能和动态性能均较为理想,满足设计要求。