VHDL 硬件描述语言在数字电路设计中的应用研究

2021-06-16张东莹

张东莹

(南京技师学院,江苏南京,210023)

在数字电子技术应用进程中,数字电路逐渐以集成电路为主要表现形式,对电路设计提供了较高要求。在逻辑器具有编程能力时,数字电路设计形式以硬件为运行环境,以计算机软件为电路设计的开发主体,有效提升了电子设计发展能力,使其具备自动化设计效果。在仿真设计方面,对硬件描述语言的应用,给予了较大认可,旨在缩短电子电路设计消耗时间,提升电路系统设计的应用性能。

1 VHDL 硬件描述语言应用特点

■1.1 基本结构

(1)库。在此项语言结构中,完成数据定义、语言应用说明、存储数据程序包等。

(2)实体。此项语言要素,针对电路外观给予语言描述,借助I/O 端口应用,不具备逻辑描述功能。

(3)结构体。此项语言要素,针对电路设计模块予以描述,描述的是模块所具备的逻辑功能,结构体应与实体形成关联体系,以此确定实体输入、信号输出之间形成的内在逻辑关系,便于电路设计实体能够兼容多组结构体。

■1.2 语言特点

(1)描述能力优异。VHDL 语言具有较强的描述能力,可描述的电路种类,具体包括门级、系统级。对其描述的同时,能够完成电路仿真设计,以此确定系统电路设计功能实现的可行性。

(2)较强的可移植性。在各类平台、仿真工具中,可使用相同的语言进行描述[1]。

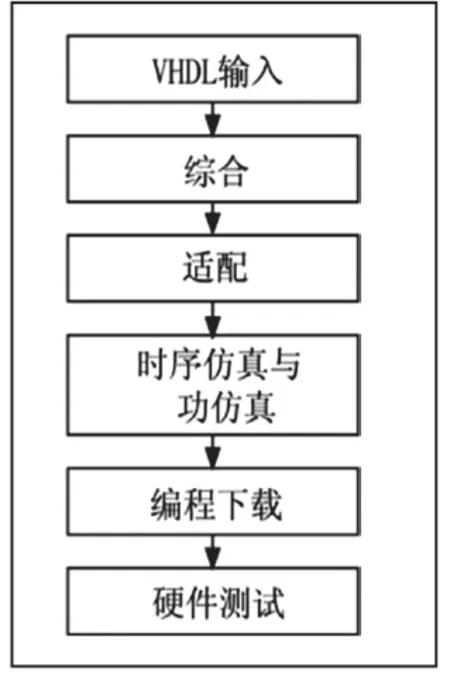

■1.3 设计流程

VHDL 语言电路设计期间,应以电子系统为设计出发点,在顶层完成功能设计,继而对各功能模块逐一开展仿真设计,具体流程如图1 所示。

图1 VHDL 语言应用程序示意图

2 在数字电路设计中融合VHDL 硬件描述语言的应用实践

■2.1 单片机仿真设计

2.1.1 设计单片机的定时器模块

在定时器模块开展设计期间,应结合原有的设计理念,完成功能有效划分,保障裁剪操作的正确性。VHDL 语言借助寄存器的独特应用功能,比如控制管理进程、跟踪运行状态等,在信息传输作用下,达成远程控制的设计效果。控制项目、远程操作等功能设计,依托于定时器设计思想。语言融合在功能模块中,在信号输入时,能够重新配置定时器的各项数据,转化原有信号传输形式,使其形成具有标准性格式的信号,以此达成远程控制目标。

VHDL 语言设计期间,主要设计方向有三个:其一设计模块,在信号输出完成时,对信号采取转换措施,同时完成信号的完整存储;其二设计模块,有效采集脉冲输入模块的各项信息,便于生成控制信号,比如计数器、定时器;其三设计模块,让VHDL 语句作为控制信号的主要组成,借助两个控制信号,提升控制信息的运作能力,以信号差异性为主体,形成系统性定时器控制程序。

“生态移情”实质上更深刻、系统地表达了一种整体论的移情与认同思想。在这种意义上,“生态移情”能够能动地引导人们去设身处地的爱护动物,自觉地保护生物多样性,从而实现人与自然界其他物种的和谐相处。

2.1.2 设计单片机的UART 串口

(1)RAM 存储器,作为单片机数据存储的关键单元,同时能够依据程序堆栈区的实际情况,完成数据有效分类。在信息存储容量视角观之,CPU 与RAM 两个单元在设计期间,并未表现出较大差异。因此,保持RAM 存储单元与单片机接口处于有效连接状态,完成模块设计。

(2)ROM 单元功能是完成单片机参数固定控制,针对单片机存储数据加以分析。与RAM 相比时,此单元设计的关键表现在信息存储功能方面。ROM 单元在系统有序运行期间,能够调整信息存储位置、信息存储数量。一般情况下,如若存储信息不小于16 位,单片机将会以自动跳转形式完成存储。

(3)FIFO 单元设计,能够提升逻辑电路设计的精准性。FIFO 单元在设计期间,常用的设计形式为直接调取例化库元件形式,增强库元件电路设计能力,借助VHDL 语言完成相应调节,与功能模块形成联合体系,形成系统性语言设计效果。单片机系统中完成FIFO 单元连接,其逻辑电路、语言应用等设计,将会获得更高的应用灵活性,具备多样性应用性能。

2.1.3 设计单片机的数据转换器

数据转换器在单片机系统中具有较高应用频率,作为信息处理集中单元,能够有效整合各项数字化语言,使其形成多样化组合的信息模拟量。单片机系统中的分立元件,在应用与功能方面表现出优异的独立性。因此,在设计单片机系统中的数据转换器时,应强化功能独立应用特性,最大化发挥单片机的应用优势。转换器在设计期间,应在信息处理终端程序中完成信号输送,继而借助复位处理形式完成数据高效数据,将数据信息划分为两类,一类为工作信息,另一类为控制信息。工作与控制两类信息,在经由滤波器时,能够对信息应用性能加以判断,在确定数据真实性的基础上,系统将信息传输至CPU 管理程序中[2]。

■2.2 数字时钟仿真设计

数字电子时钟的电路设计,应用的是典型时序逻辑电路,在日常生活中获得了广泛应用。以VHDL 语言为基础,开展数字电子时钟的电路设计,设计成果具有较强的可移植优势,在共享与复用等方面具有较高应用便利。

数字时钟在仿真设计期间,应确定其功能模块,具体包括分频、计时、报时、显示四个单元。在设计仿真完成时,将会生成相应的模拟元件,模拟元件将会以底层文件形式,完成文件存储。借助元件例化语言,完成数字时钟整体程序的电路设计与编写。

(1)分频模块

针对输出信号开展分频处理,以此获取1Hz 输入信号。以分频器为基础,开展电路设计,是以计数器电路为主要设计形式,借助多级二进制计数器完成电路设计。分频倍数设定为100,开展至少三次分频操作,将会获得秒级时钟信号。

(2)计时模块

计时模块含有三个组成要素,分别为秒级计时单元、分钟计时单元、小时计时单元。秒与分两个计时单元,在对其设计计数器时,使用六十进制设计形式。小时计时器在电路设计期间,使用的算法为二十四进制。将三级计数器分别从输入逻辑电路中,形成秒、分钟、小时三个等级的计数形式,达成计时功能电路设计效果。秒级脉冲信号,传输至计数器时,将会获取秒、分钟、小时各级参数,包括个位、十位。

(3)报时模块

报时模块的作用在于,当时间为整点时,模块输入信号设定为min,其中min1、2 的取值均设定为00,alarm 报时时间输入形式为高电平,报时持续周期为1 分钟,alarm报时设定为整点时,将会在设定时间发出高电平,报时周期持续至min 值超过0,即报时时间将会持续一分钟。

(4)显示模块

使用数码管显示时间计数结果。

(5)系统整体设计

在各模块设计的文件,以底层文件形式完成存储,同时使用例化语句完成顶层程序设计,使用PORT MAP 语句,有序连接各模块引脚。

■2.3 时间控制器的仿真设计

软件环境选择为Quartus,编程语言确定为VHDL。在不改变原有时钟电路形态的同时,对其开展功能完善,以此达成各类作息时间的时钟提醒功能。

(1)设计理念

结合实际人群的作息习惯,设定个性化时间提示的作息控制器。在此程序设计中,提示功能、模式设计作为关键环节。借助VHDL 语言的编程优势,开展模块化程序编写设计,模块包括分频、时间优化、计数、显示。

(2)时间优化的模块设计

此模块主要完成计时功能的前期设定,以手动形式完成信号输入,在计时初期,调整计时器的最初状态。计时器具有固定式最大计时功能,即相比24 小时少1 秒。与此同时,能够手动完成时钟分秒级误差校准。如图2 所示,为优化电路设计示意图。此模块在设计期间,其单元组成包括非门、或门,或门为二选一。非门设计应用为:将低电压输入值以高电压形式完成输出。二选一或门的设计应用,旨在标准化电路运行状态中,完成时钟电路的手动操作[3]。

图2 时钟电路控制示意图

(3)显示模块设计

此模块在设计期间,其功能用于显示计数器输出信号的处理成果,借助各类编码在LED 数码管位置上,准确显示计时结果,以此提升计时结果显示的直观性。在显示模块中,设定引脚d[3..0]的功能为:有效接收计时器模块的传输信号。显示模块与计时器传输信号形成一一对应的关系,便于传输信号的准确接收。设定引脚h[6..0]的功能为:处理传输信号予以显示,将接收的计时器信号,编译成时间显示格式,显示在数码管区域,以此完成时钟显示模块设计。

3 结论

综上所述,VHDL 语言的有效应用,提升了数字电路设计效果,以较强的系统描述能力,在多级层次完成了数字系统电路设计,提升了电路设计系统的应用灵活性,缩短了电路设计所消耗的时候,增强了电路设计的应用能力。VHDL语言以系统应用为全局视角,具备较强的逻辑编辑能力,适用于电子工业行业,为数字电路设计行业发展奠定技术基础。