基于FPGA 的出租车计价系统设计

2021-06-08吕兆承余钱坤

李 营,吕兆承,陈 帅,余钱坤

(淮南师范学院 电子工程学院,安徽 淮南 232038)

1 引言

出租车是人们日常出行的重要工具,其载客出行均需计费, 市面上常用的计费器大多由单片机控制实现计费。单片机虽然价格低廉,但精度差且可扩展性弱。而FPGA 具有编程灵活性高、功能易拓展等特点。 故本文采用层次化建模方法, 利用Verilog HDL 基于FPGA 设计实现出租车计价器系统并进行仿真,仿真结果表明该系统功能稳定,计价准确。

2 出租车计价器系统设计

2.1 出租车计费系统技术指标

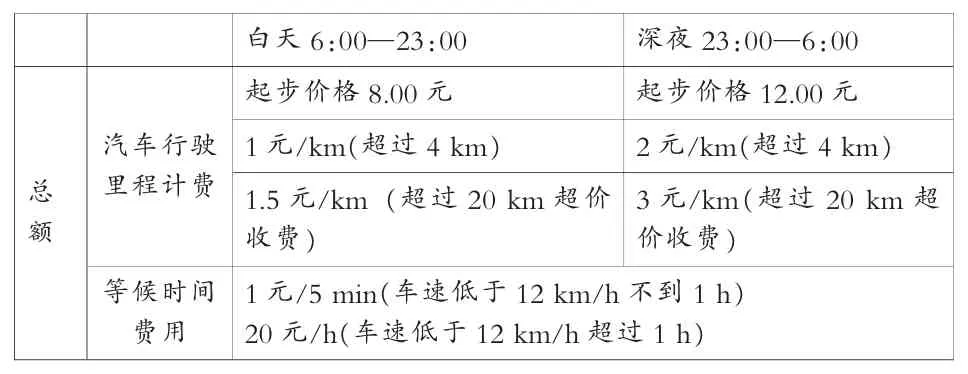

以FPGA 为主体设计出租车计费系统,其计费标准如表1 所示。

表1 出租车计费标准

根据表中的相关技术指标,系统设计要求如下。

(1)设置加减档功能:白天行驶超过4 km,每公里加1.00 元。 夜晚行驶超过4 km, 每公里加2.00 元。 单程行驶超过20 km,每公里加收50%的车费,收费累加。

(2)将时间、里程及计费结果以小数的形式显示在液晶屏上。

(3)费用的计算:当行驶里程小于3 km 时,按起价计算费用;当里程大于3 km 时,按下式计算费用:

费用=里程×里程单价+等候时间×等候单价

2.2 系统设计原理

本系统硬件采用的主控FPGA 芯片是Cyclone EP4CE6E22C8, 设计通过按键模拟汽车行驶过程中的速度状态和模式的变化,故需开始、停止、拨码开关控制车辆运行的开始和停止,需要空档、加速、减速等3 个按键控制速度,通过模式按键模拟白天与夜间。 LCD 显示器应当显示行驶公里、时间、计费情况以及车辆的档位等。 白天与夜间的变化用LED 灯的亮或者灭来表示,当时为白天,LED 灯不亮,夜间模式时LED 灯开启。

2.3 LCD1602 显示原理

LCD1602 是一种工业字符型液晶显示屏,它能显示字母、数字、符号,并且同时显示16×2 个字符。 利用了液晶的物理性质,一般通过电压对其32个显示区域进行控制。 LCD 驱动初始化的流程图如图1 所示。

图1 LCD 显示模块驱动初始化流程图

3 出租车计价器系统功能实现

3.1 软件设计总体方案

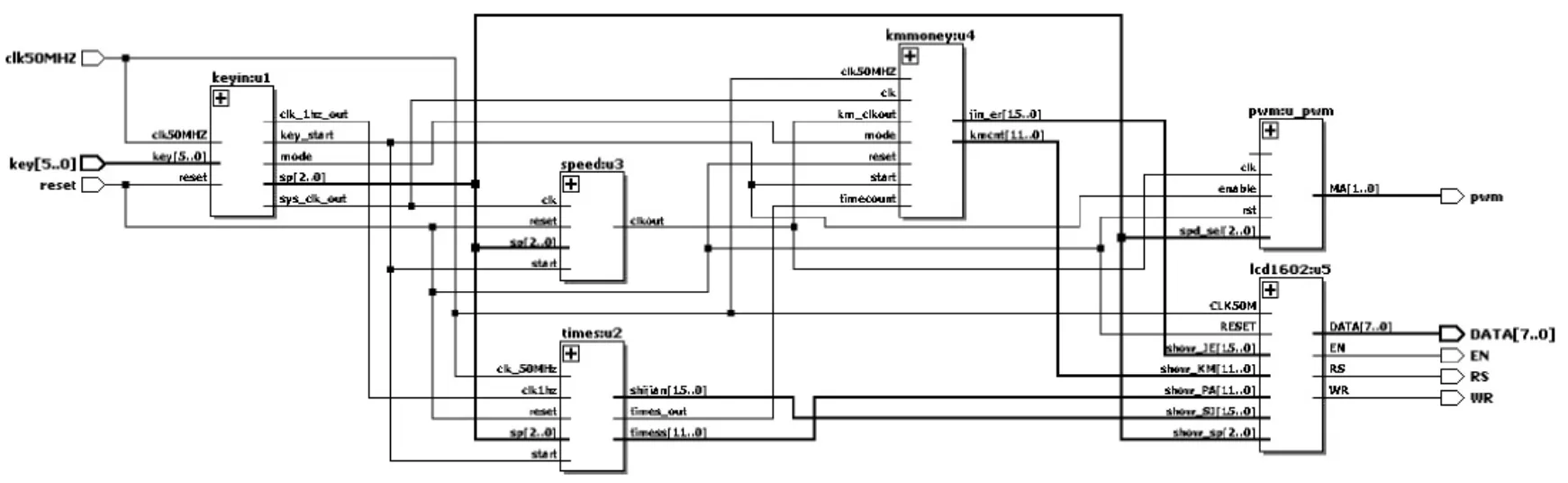

根据上述硬件要求,可将系统划分为分频与按键控制模块、速度控制模块、直流电机PWM 控制模块、时间设置模块、计费模块以及LCD 驱动显示模块,总体软件设计框图如图2 所示。

图2 总体软件设计框图

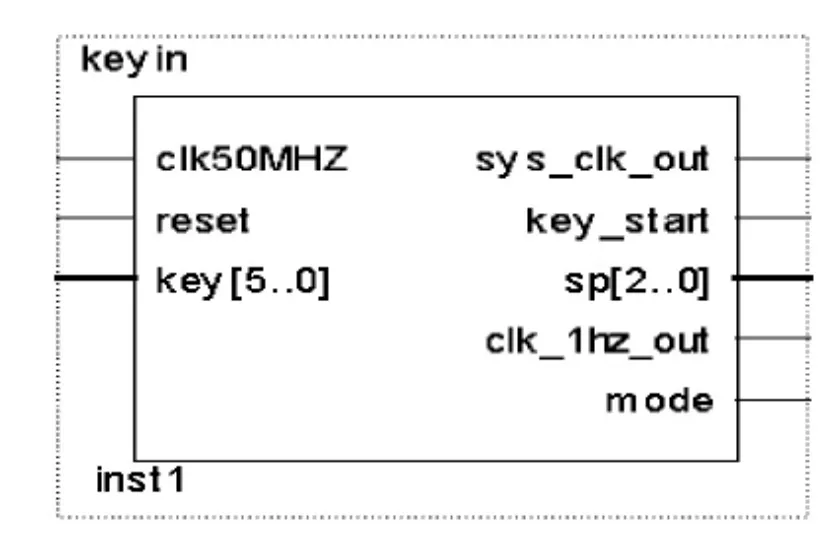

3.2 分频与按键控制模块设计

该模块的功能是将50 MHz 分频为1 Hz 和16.6 Hz,并对开始、停止、空档、加档、减档、模式等输入按键进行功能设计, 其功能接口框图如图3 所示。

图3 分频及按键控制模块框图

由图3 可知该模块的输入有:50 M 的时钟脉冲clk50M,复位端口reset,6 个按键的输入如图中key[5..0];输出端 sys_clk_out 对应 16.6 Hz 时钟输出,clk1Hz_1hz_out 对应 1 Hz 时钟输出,mode 对应白天黑夜的模式选择输出,key_start 代表系统启动输出,sp[2:0]代表速度档位变化输出。

3.3 直流电机PWM 控制模块设计

该模块的功能是实现直流电能和机械能互相转换,接收分频与按键控制模块的控制按键,从而控制电机旋转。 该模块的接口框图如图4 所示,各端口的含义如下,输入端口均连接分频及按键控制模块各端口,enable 是控制开关接key_start 信号,clk 和rst 接系统时钟和系统复位信号;Dir 是控制转动方向代表前进后退,默认1,代表前进;spd_sel接sp[2:0]信号,代表调节电机转动速度;输出端口MA 接系统输出直流电机。

图4 直流电机PWM 控制模块框图

图5 速度设置模块框图

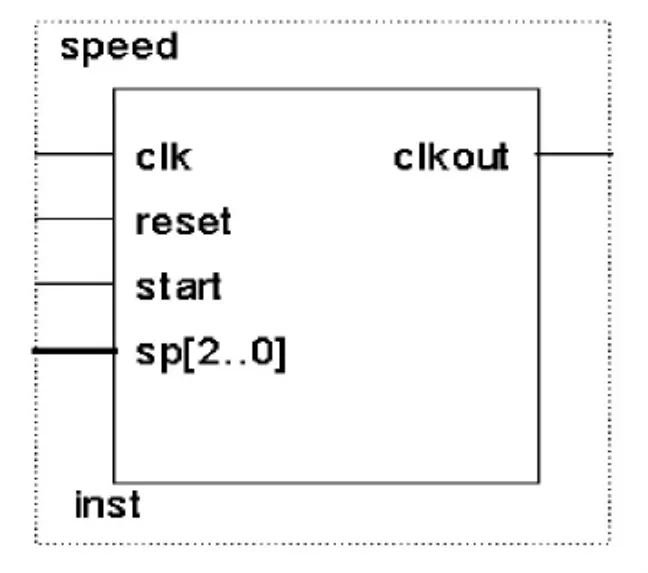

3.4 速度设置模块设计

速度设置模块的功能是对汽车行驶过程中的6 个速度档位进行设计,模拟实际出租车行驶换挡变速。 通过输入的系统脉冲控制产生6 种不同频率的时钟翻转, 从而切换0 至5 挡不同的6 种速度变换。

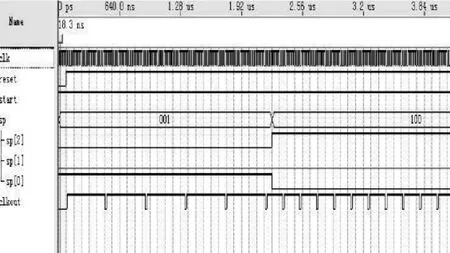

该模块的功能接口框图如图5 所示。图5 中各端口的含义是:clk 是 16.6 Hz 时钟输入、reset 是复位输入、start 和sp[2:0]端口分别连接按键控制模块的key_start 端口和sp[2:0]端口,分别代表开始信号和档位输入。 clkout 表示汽车模拟行驶的公里脉冲输出, 该模块的仿真波形如图6 所示。 由图 6 可知,档位 sp 由 001 变为 100 的时候,输出clkout 有明显的变化,时钟跳变加快,说明汽车速度的加快。

图6 速度设置模块仿真波形

3.5 计时模块设计

该模块完成两大功能:其一是对空档时汽车的等待时间计时,其二是对汽车行驶时间(包括等价和汽车的行驶计时)计时。 该模块的接口框图如图7 所示,各输入端口的含义与速度设置模块含义相同,输出端口time_out 含义是用于等待的计费时间(即空档等待的时间),输出端口timess[11..0]指等待计时时间,shijian[15..0]指总的时间输出。

图7 计时模块接口框图

图8 计费模块接口框图

3.6 计费模块设计

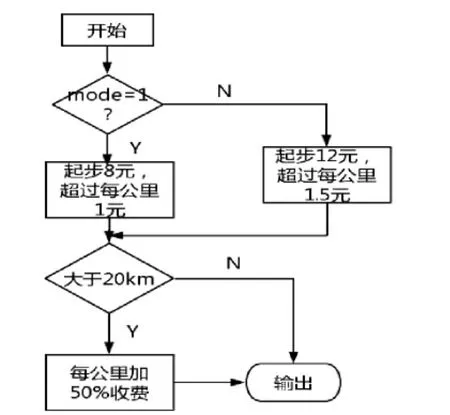

该模块的功能是根据白天与黑夜模式下计费方法的不同分别计费。根据行驶公里数及等待时间长短,针对不同模式分别计费。 模块接口框图如图8 所示,该模块的算法流程图如图9 所示。

图9 程序流程图

出租车总的计费金额需用整数和小数表示出来。 该模块的仿真波形如图10 所示, 当start=1,mode=1 及km_clkout 变化时,即白天开始计时,汽车行驶后, 行驶距离km_cnt 由0001 跳变为0010,即由1 km 到2 km,此时计费值jin_er 变为10 000 000,即高4 位整数位,低4 位为小数位,共8 元,与设计要求4 km 内起步8 元一致。

图10 白天模式计费模块仿真波形

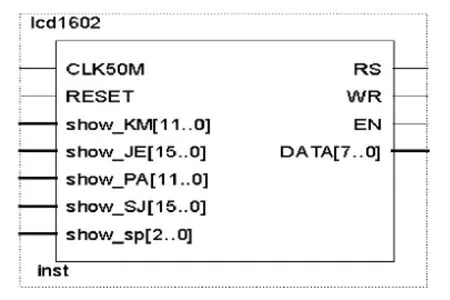

3.7 显示模块设计

采用LCD1602 字符型显示器显示行驶信息,采用英文字母显示提示。相关显示内容与其字符分别为:行驶里程(KM)、计费(JE)、汽车档位(数值)、等待时间(A)以及等待时间和行驶时间之和驾驶总时间(T)。 根据1602 的驱动指令表驱动编写此模块[3]。

本模块的接口框图如图11 所示,WR 端是读写端,EN 是使能端,DATA[7..0]为双向的输出数据段。 Show_KM[11..0]是 12 位的行驶公里的显示数据输入,show_JE[15..0]是显示计费的16 位数据输入,show_PA[11..0]是 12 位的显示等待时间数据输入,show_SJ[15..0]为16 位总的时间显示数据输入, show_sp[2..0]为 3 位档位的输入。

图11 显示模块接口框图

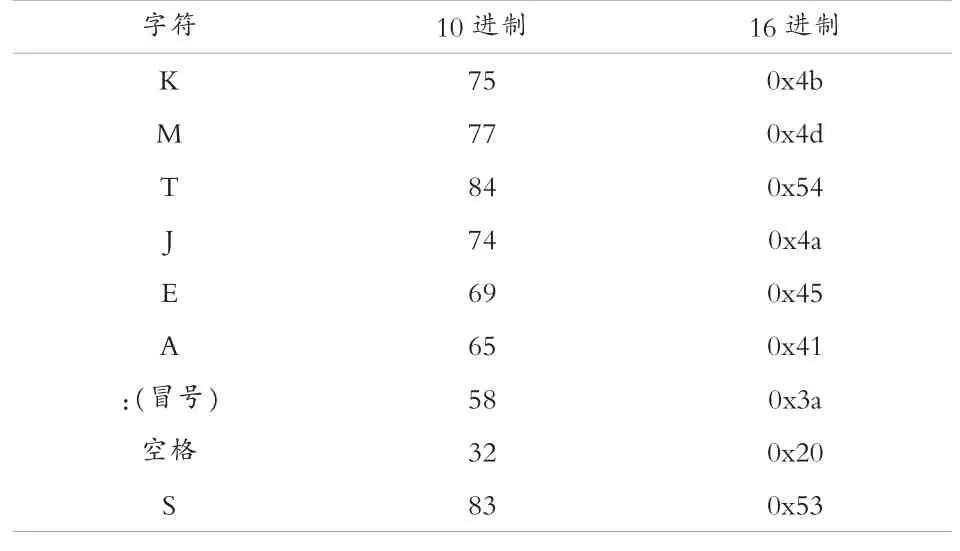

表2 ASCII 码

图12 系统设计RTL 图

本系统用到的字母相应的ASCII 对照码如表2 所示,显示时各信息间通过空格间隔。

3.8 顶层设计

顶层模块的作用是调用连接上述5 个底层模块,系统 RTL 图如图11 所示。 图11 中,顶层模块的时钟输入端clk50MHZ 对应图2 的clk50M,模块keyin 对应分频及按键处理模块,speed 对应速度设置,times 对应计时模块,kmmony 对应计费模块,lcd1602 对应显示模块,由此可见,系统完成的功能与图12 系统总体软件设计框图一致。

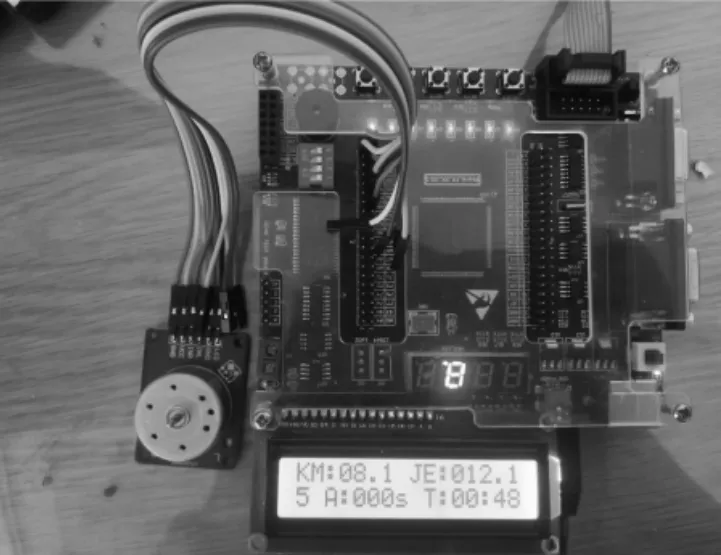

图13 系统硬件设计

4 系统仿真测试

系统完成后的测试效果如图13 所示, 当按开始键之后显示,当白天行驶8.1 km,等待时间为0 s时, 费用为12.1 元符合功能设计中设置的白天的计费原则,所以白天模式下出租车计费程序设计无误;同理,若模式调为黑夜,计费结果也无误,由于篇幅所限,此处不再列图。

5 结语

市面上现有的出租车计价器的精度不高, 系统的功耗大,使用寿命短,并且系统升级扩展的空间小。文章采用了FPGA 芯片Cyclone IV EP4CE6E22C8设计并实现了出租车计价系统, 系统功能完整,且鉴于FPGA 的并行计算和可编程特性, 灵敏度高,后期功能易拓展,为传统出租车计价提供了一种新的设计思路。