一种高效的时序转换电路设计与实现

2021-06-03何嘉文刘承禹

杜 斐,何嘉文,刘承禹,张 骏,田 泽

(航空工业西安航空计算技术研究所,陕西 西安 710068)

0 引 言

嵌入式处理器是目前片上系统中常用的处理器引擎,包括处理器、PLB总线系统、软件驱动等部分,其性能高、功耗低、使用灵活,且能够通过PLB总线和其他IP相连接,在片上系统芯片中应用广泛[1-2]。

由于PLB总线结构复杂,时序多样,且其接口时序与常用的寄存器接口访问时序差距较大,不利于迅速建立成熟IP和PLB总线连接。为解决此问题,首先深入研究嵌入式处理器内部PLB总线协议和PLB总线各个接口的结构及机制,然后在理解PLB总线系统时序以及内部各子模块的功能与工作机制的基础上,提出一种高效时序转换电路解决方案,以满足PLB端单拍传输、Line传输和Burst传输,从设备端同步、异步时序传输的通信需求。通过功能仿真和工程实践表明,该时序转换电路工作稳定,性能良好,具有配置灵活、使用方便、数据传输效率高等优点,较好地满足了应用需求[3-5]。

1 PLB总线概述

PLB总线是嵌入式处理器内部的主要总线,主要特性如下:

性能高:支持读操作和写操作的重叠传输,支持两种操作在同一周期发出,以最大程度提高总线效率;数据总线和地址总线不耦合,以提高系统带宽;地址流水线可扩展,支持数据重叠传输,总线的延迟减少;支持总线请求/仲裁重叠,支持同步总线。

灵活性高:最多支持16主16从设备,且为每个主设备分配多个优先级以方便根据主从设备的重要度仲裁;支持原子操作;支持指令预取和数据预取;支持4字节到32字节的各种长度的DMA传输[6-7]。

2 时序转换电路设计与实现关键技术

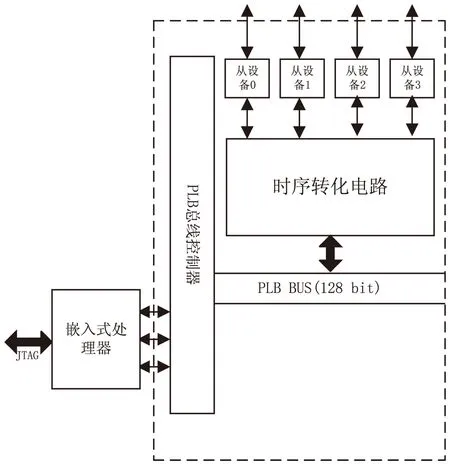

为实现片内PLB总线和从设备的连接,该文提出一种高效时序转换电路解决方案。其具体功能为,PLB端支持四字、双字、字、半字以及字节单拍传输,4字Line、8字Line、16字Line传输和四字Burst传输。从设备端支持同步时序、异步时序,其中,可根据需要编程异步时序的时钟周期数,每个片选空间可分别独立编程,且能提供4个片选空间,每个片选空间大小固定为32 MB,其地址空间分配固定,PLB4总线上的单次访问不能跨越片选空间分配的32 MB地址边界[8-9]。时序转换电路系统应用框图如图1所示。

图1 时序转换电路系统应用框图

该文设计开发的时序转换电路具有以下特点:

(1)配置灵活:为适应各种从设备接口,本时序转换电路支持异步接口和同步接口,异步接口的时序分为3个阶段,具体包括建立阶段/选通阶段/保持阶段,使用者可依据需要对3个阶段的周期数进行编程。同步时序每周期一次访问,访问长度用户可配置,且可以根据用户需要编程延迟1周期或者2周期。

(2)使用方便:基于用户的使用需求,本时序转换电路在PLB总线端主要支持单拍操作、8字Line操作和4字Burst操作,用户进行小规模数据搬运(32位以下数据)时,可使用单拍操作,进行中等规模数据搬运(32~512位数据)时,可使用8字Line操作,进行大规模数据搬运(512位数据以上)时,可使用4字Burst操作。

(3)数据传输效率高:进行单拍操作,本时序转换电路从收到PLB一端输入的请求,到向从设备一端输出请求,仅需2个PLB_CLK时钟周期;进行4字Burst操作,本时序转换电路从收到PLB一端输入的请求,到向从设备一端输出请求,仅需8个PLB_CLK时钟周期[10-11]。

2.1 电路体系架构设计

时序转换电路体系架构框图如图2所示。状态机完成内部各个状态的转换与控制;时钟分频电路根据分频配置值完成对PLB时钟的分频,产生从设备使用的时钟;寄存器控制电路完成处理器对寄存器的配置;输出控制根据状态机和寄存器配置值产生到时序转换电路和回复PLB接口的控制信号及地址、数据总线。

图2 时序转换电路体系架构框图

时序转换电路作为片内PLB总线与从设备转接口,通过将PLB总线时序转换成从设备时序,实现对从设备的访问,其对从设备的访问支持8位、16位和32位读写访问。时序转换电路为从设备提供异步接口和同步接口,其中异步接口的时序分为3个阶段,具体包括建立阶段/选通阶段/保持阶段,使用者可依据需要对3个阶段的周期数进行编程。同步时序每周期一次访问,访问长度用户可配置,且可以根据用户需要编程延迟1周期或者2周期。

时序转换电路支持大量的PLB时序,包括单拍传输(128位/64位/32位/16位/8位)、Line传输(4字/8字/16字)以及4字Burst传输。

2.2 电路详细设计与实现

2.2.1 时钟分频

时钟分频电路如图3所示,作用为根据配置将PLB时钟分频为从设备使用的时钟,此电路可设置的分频比率包括2分频/4分频/8分频,分频器根据设置输出相应PLB时钟频率分之一的时钟。

图3 时钟分频电路

2.2.2 寄存器控制

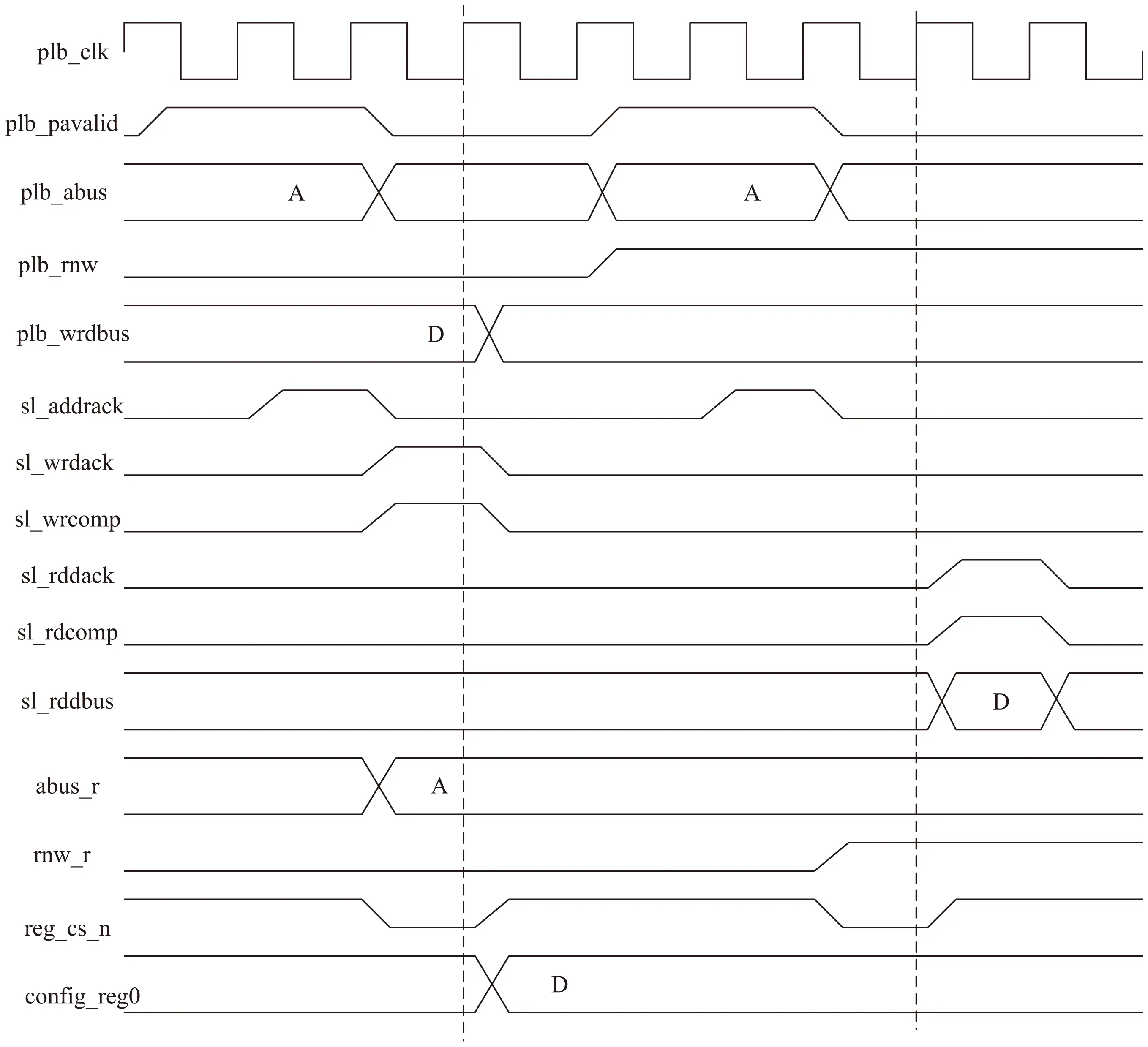

处理器通过PLB总线对时序转换电路寄存器的访问是通过寄存器控制模块实现的。

寄存器的读写操作的时序图如图4所示,当确认地址有效时,将sl_addrack信号拉高,向PLB总线表明当前地址已存储,同时在abus_r和rnw_r两个信号中存储plb地址和读写标志。之后,若此操作为寄存器读操作,将reg_cs_n拉低,根据abus_r的值将相应的返回值输出到PLB总线上。若此操作为寄存器写操作,将reg_cs_n拉低,将plb_wrdbus的值写入相应寄存器。

图4 寄存器读写时序图

本模块共实现5个寄存器,分为两组。第一组为全局控制寄存器,用于配置CLK_DIV分频比率,产生一分频、二分频、四分频、八分频,供时钟分频模块使用。第二组分为4个片选空间控制寄存器,分别控制4个从设备的同步/异步时序选择,异步写建立/选通/保持时间,异步读建立/选通/保持时间,供输出控制模块使用。

2.2.3 输出控制

输出控制根据状态机和寄存器配置值产生到时序转换电路和回复PLB接口的控制信号及地址、数据总线。下面以PLB总线上的单拍和Line读写操作为例,详细介绍其实现。

如图5所示,此操作为单拍读操作,数据位宽为64位,其从设备接口配置为32位。且设置主设备的PLB时钟频率为从设备的slave_clk频率的2倍。当PLB_pavalid信号为高,且PLB_abus地址落在本模块的地址空间时,将sl_addrack信号拉高,并将信号plb_abus、plb_be、plb_size、plb_rnw存储在内部信号abus_r、be_r、size_r、rnw_r。存储后在从设备时钟slave_clk的T0周期,根据rnw_r判断操作的读和写,size_r判断读写长度、be_r判断操作类型,可知此操作为64位单拍读操作。此时在从设备接口根据寄存的数据输出(由于主设备接口为64位,从设备接口为32位,故从设备需要2拍才能完成一次主设备操作),因此,在T1到T2的周期,接口输出片选slave_cs_n和读信号slave_rd_n。之后按照存储的地址信号abus_r输出信号slave_addr,之后输出信号slave_addr将在片选和写信号有效时按32位递增。从设备接口的读数据总线slave_data_out在T2以及T3周期返回数据W0、W1,接口需要存储T2周期的数据W0,之后在T3周期将W0和W1合并为64位数据后在sl_rddbus信号输出到PLB总线,在T4周期,将读数据响应信号sl_rddack和读访问完成信号sl_rdcomp置为1表明当前操作完成。

图5 PLB总线64位单拍读时序

图6 PLB总线8字Line写时序

图6是PLB总线8字Line写访问,在从设备时钟slave_clk频率和PLB时钟plb_clk频率一致时的时序图。当PLB_Pavalid信号为高,且PLB_abus地址落在本模块的地址空间时,将信号plb_abus、plb_be、plb_size、plb_rnw存储在内部信号abus_r、be_r、size_r、rnw_r中,存储后,在slave_clk的T0周期,根据rnw_r判断操作的读和写,size_r判断读写长度、be_r判断操作类型,可知此操作为8位Line写操作。将从设备接口设置为32位的同步接口,因此,完成8字Line操作需要8个周期,如图6所示即T1到T8周期,输出写信号slave_wr_n和片选信号slave_cs_n为0,并将PLB数据总线plb_wrdbus的数据寄存的输出到slave_data_in,地址slave_addr的初始值采用存储在内部信号abus_r,随后写信号有效递增,在T4和T8周期,输出PLB总线写数据响应信号sl_wrdack为1,在T8周期后将写访问完成信号sl_wrcomp写为1[12-13]。

2.3 虚拟仿真验证

时序转换电路设计完成后,基于此模块的需求,搭建验证平台,对模块的功能进行验证。验证过程包括验证平台开发、验证项策划以及仿真验证结果三个部分。下面分别对此三部分进行介绍。

2.3.1 验证平台搭建

为保证验证环境与实际使用环境尽可能一致,该文基于嵌入式处理器系统来开发验证平台。在成熟的嵌入式处理器系统自带的PLB总线上,挂接自主开发的时序转换电路,然后在时序转换电路后面挂接4个从设备模型。验证平台的激励由C语言开发,使用嵌入式处理器系统自带的编译器编译为指令文件后,直接写入处理器系统的外部ram中,等待处理器复位完成后,将自动从外部ram中读取指令,并通过PLB总线向时序转换电路下达四字、双字、字、半字以及字节单拍传输,4字Line、8字Line、16字Line传输,四字Burst传输指令。时序转换电路根据指令内容选择是配置内部寄存器,还是配置从设备。为保证测试结果正确性,在时序转换电路外部开发同步/异步接口从设备模型,用于响应时序转换电路的请求,并检测时序转换电路输出的同步、异步时序访问是否与期望值一致[14-15]。虚拟仿真验证平台框图如图7所示。

图7 时序转换电路虚拟仿真验证平台框图

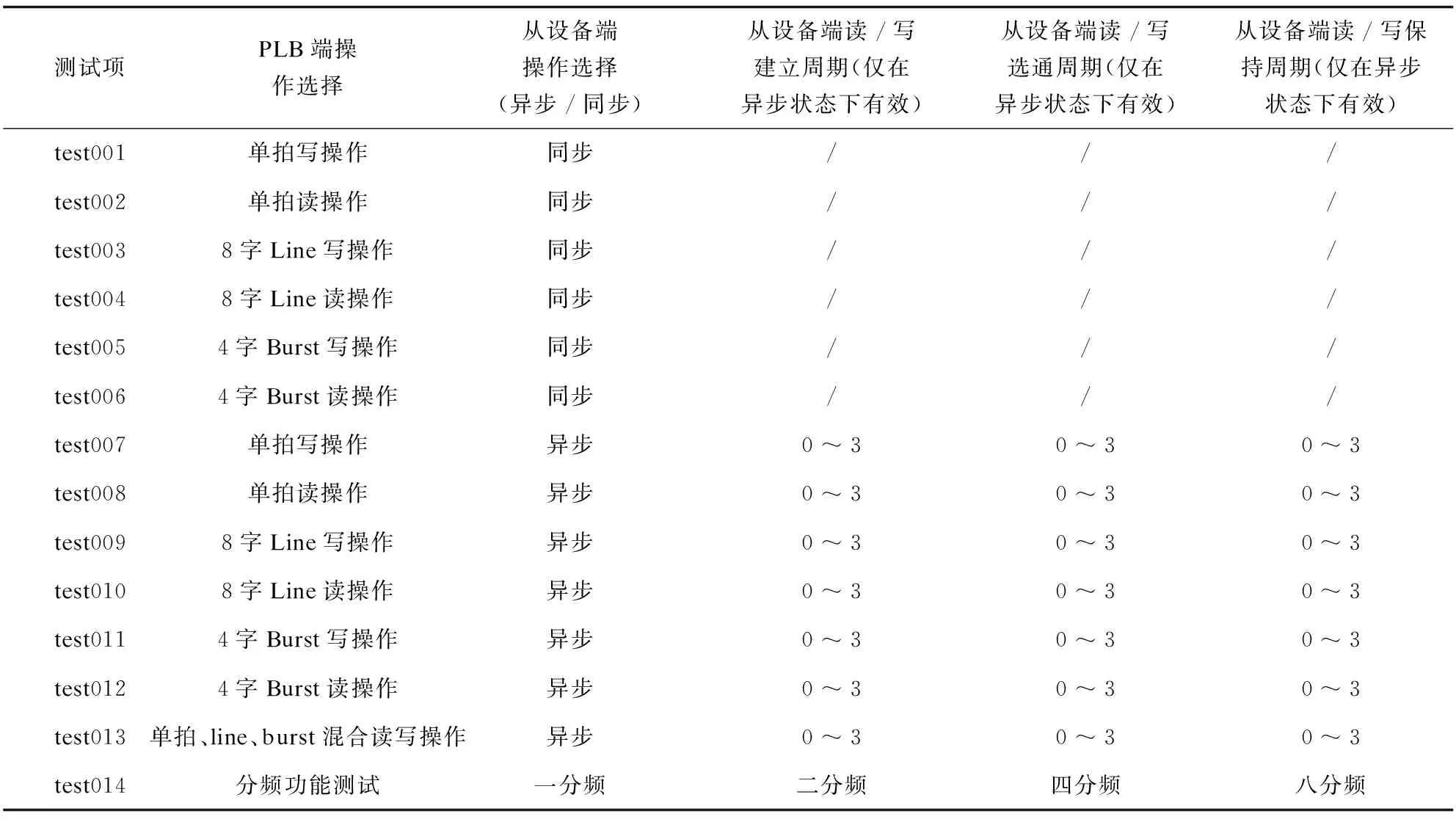

2.3.2 验证策划

为进行全面验证,针对时序转换电路需求及设计核心要点,涵盖所有PLB总线端和从设备端支持的模式,策划出以下验证项,具体如表1所示。

表1 验证项策划表

2.3.3 仿真验证结果

在上文搭建的验证平台上,按照策划的验证项对时序转换电路进行测试,测试结果表明,此时序转换电路功能和性能达到了设计要求,能够高效、灵活地在PLB总线和从设备间进行数据传递。

根据测试后的代码覆盖率的统计结果可知,被测时序转换电路的总语句覆盖率(stmt graph)为100%,分支覆盖率(branch graph)为100%。由于default语句很难覆盖到,所以其内部部分子模块的覆盖率并未达到100%。综上所述,上述代码覆盖率百分比的情况可以认为满足了目标覆盖率要求。

3 结束语

基于嵌入式处理器,给出了一种时序转换电路,能够在PLB总线和从设备间高效、灵活地进行数据传递,并进行了必要的功能仿真和工程实践。结果表明,该转换电路工作稳定、性能良好,较好地满足了应用需求,且对其他类似接口转换设计具有一定的借鉴意义。