一种用于压电式喷墨打印头的梯形波脉冲信号源设计

2021-05-14汪邵华朱建晓包建东

汪邵华, 朱建晓, 包建东, 程 伟

(1.南京理工大学 机械工程学院,江苏 南京 210094; 2.苏州康尼格电子科技股份有限公司,江苏 常熟 215562)

随着数字化和信息化的快速发展以及其在印刷行业的应用,数字印刷已经慢慢替代传统印刷成为未来印刷行业的风向标[1]。压电式喷墨打印技术是数字技术的主流技术之一,具有喷射频率高、控制精确等优点[2]。

压电陶瓷驱动电源是压电式喷墨打印设备的关键部分,驱动电源输出激励脉冲电压的大小决定着压电陶瓷片的形变量,激励脉冲的频率会影响陶瓷片的形变速度,从而决定喷墨打印产品的质量[3-4]。通常选用梯形波作为压电式喷墨头的激励脉冲波形[5]。激励脉冲的幅值越大,喷出的墨滴质量越大;并且在一定范围内,脉冲宽度越大,墨滴质量越大;发送激励脉冲的频率越大,墨滴喷射速度越快。通过调制激励脉冲幅值、脉宽和发送频率,可以控制喷射出的墨滴的大小和速度。所以调制分辨率小且精确可控的激励脉冲信号的幅值、脉宽和频率,可保证印刷品的质量[6-7]。

DDS(Direct Digital Synthesizer,直接数字频率合成技术)是把一系列数字信号通过DAC转换为模拟信号的合成技术,可实现快速精准的频率、相位和幅值全数字化调制[8]。目前,部分相关研究人员采用DDS芯片方案来实现DDS信号源的设计,该方案是通过芯片生产商将电路集成到一块DDS芯片上,将不同的波形控制字和频率控制字发送给DDS芯片,然后产生相应波形的信号。由于DDS芯片的ROM里一般都存储正弦波,需要通过一些外围电路产生其他波形,产生波形的速度和频率带宽受到很大的限制,因此其使用不够灵活[9-10]。

本文采用基于FPGA的DDS原理实现信号源设计的方案,在FPGA芯片上实现梯形波激励脉冲信号的产生和控制。通过使用FPGA程序实现DDS信号发生器的方法,可以实现产生频率和波形可调的梯形波激励脉冲信号,且输出频率带宽较宽,完全满足压电式喷墨打印喷头工作要求。该方案电路简单、性能稳定、控制简单、使用方便,可为压电式喷墨打印喷头提供一个精确、稳定的激励脉冲信号。

1 DDS系统介绍

1.1 DDS理论原理

无论是想输出正弦波、方波、三角波、锯齿波还是梯形波,只需在ROM查找表中储存对应数据,就可输出相对应的波形[11]。本节以正弦波为例对DDS原理进行介绍。输出其他波形信号的DDS原理与正弦波相似。

正弦波信号的表达式为

F=Asinθ=Asin(2πft)

(1)

式中,A为正弦波信号的幅值;f为正弦波信号的频率;θ为正弦波信号的相位。因为式(1)中的时间t是连续的,FPGA系统使用的是系统时钟,对式(1)用基准时钟clk进行抽样。

因此,在一个基准时钟clk周期Tclk内(其对应频率为fclk),其相位θ的增量Δθ为

Δθ=2πfTclk=2πf/fclk

(2)

对Δθ进行数字量化,N位二进制数一共具有2N个样值,在式(2)中把2π分成2N等份,则输出信号的频率为

f=Δθ×fclk/2N

(3)

在一定的时钟频率fclk下,相位增量Δθ决定了合成信号的频率,所以Δθ被称为频率控制字,习惯用K表示。因此合成信号的频率为

f=K×fclk/2N

(4)

根据式(4)可知,改变频率控制字K即可改变DDS的输出信号频率。

1.2 DDS结构介绍

DDS的主要由系统时钟、相位累加器、相位调制器、波形存储器(ROM)、 数模转换器(DAC)和低通滤波器(LPF)组成[12],如图1所示。

图1 DDS的结构组成图

① 系统时钟:在FPGA平台上采用的是频率50 MHz晶振作为系统基准时钟,不需要使用锁相环(PLL)。

② 相位累加器:由加法器、同步寄存器和累加寄存器组成。首先,输入的频率控制字K使累加寄存器在每一个时钟增加K;累加寄存器将加法器在上一个时钟产生的新相位数据反馈到加法器继续进行累加。当相位累加器加满时就会产生一次溢出。该溢出频率就是DDS输出信号的频率[13]。

③ 相位调制器:累加寄存器的输出与相位控制字进行线性相位相加和相位调制,作为波形ROM表的输入地址。

④ 波形存储器(ROM):将一个完整周期的信号离散成具有2N个数字波形序列进行存储。由相位累加器生成N位相位量化序列的波形选择地址,由该地址选择出D位幅值量化序列;即对产生的波形进行相位-幅值转换[14]。

⑤ 数模转换器(DAC):从波形存储器中生成的激励信号的幅值量化序列,经过数模转换器(DAC)之后输出相对应的模拟电压值。

⑥ 低通滤波器:由于DDS自身的结构特点,其输出频谱中存在的杂散噪声。在DAC输出端加低通滤波器可滤除输出信号具有大量的谐波分量和系统时钟的高频噪声干扰[15]。

2 梯形波脉冲信号源系统的设计

在Quartus Ⅱ软件环境下对FPGA进行编程与仿真,编程语言为Verilog HDL,通过 Verilog HDL语言生成功能模块。软件部分包括:波形ROM表、相位累加器模块、相位调制器模块;外部电路部分包括:DAC(数模转换)电路和低通滤波电路。下面分别对该系统主要模块设计进行介绍。

2.1 波形ROM表

压电式喷墨打印头驱动电压激励脉冲信号的一个完整周期[16]如图2所示,其值为T=T1+2T2+T3。其中,T3为激励信号的有效信号梯形波的一个完整周期;T2为缓冲时间,防止输出激励信号频率过大时有效信号梯形波被下一个时钟周期的梯形波损坏;T1为间隔时间,通过调整该时间间隔,可以实现改变输出激励信号的频率。

图2 激励脉冲信号的完整周期

T3期间内的梯形波包括的参数有:激励脉冲幅值、上升时间、下降时间、激励脉冲宽度(上升时间的起点到下降时间的起点)。

由喷墨头工作要求可知[17],上升时间、下降时间这两个参数对喷墨头性能的影响比较小,上升时间关系只要满足斜率小于35~40 V/μs,就可以满足压电陶瓷完全充电。功率放大后的激励脉冲电压幅值最大为180 V,在这一极限条件下设置上升时间、下降时间为6 μs。则在正常工作时激励脉冲电压的条件下,该时间间隔满足压电陶瓷完全充电。根据喷墨头工作要求,整个T3不超过30 μs,则设置脉宽最大值为24 μs。根据以上分析可设置上升时间和脉宽的比值为1:4的梯形波波形作为激励脉冲的波形。若要设置完整周期T的波形数据,还需要设置T1和T2时间的低电平。可将T1、T2合并为TL,即TL=T1+T2,表示在整个激励脉冲信号中低电平的时间,TL需满足大于2 μs;令TB为有效信号梯形波的波形所占的时间,TZ为整个激励脉冲信号的周期,即TZ=TL+TB,则输出完整激励脉冲信号的频率为1/TZ。

储存在ROM里面的波形数据的MIF文件可通过mif_maker程序得到,如图3所示,一个周期的离散梯形波数据为210=1024个。

图3 MIF文件中的波形

梯形波的ROM表在Quartus Ⅱ软件环境下生成,创建梯形波产生模块Txing_rom,把生成的MIF文件加载到内ROM中,实现波形的存储。考虑到输出波形质量,设置地址线的二进制位数为10位,则一个周期的离散梯形波数据为210=1024个;将数据线位宽设置为8位。可将波形ROM表的地址线rom_addr[9:0]作为ROM的输入,输出梯形波数据q[7:0]作为ROM的输出。

2.2 相位累加器模块

由式(4)可得:当频率控制字K=1,N=20时,DDS输出最低频率,即频率分辨率为:fclk/2N=5×107/220=47.68 Hz。本文所设计信号源输出信号频率为0~30 kHz时,则47.68 Hz可作为频率分辨率。可设置N=20作为相位累加器的数据位宽度,设置累加寄存器Fcnt[19:0]。

由上文可知,在输出激励信号的完整周期中,TL和TB各为激励信号的周期TZ的1/2。要使输出的激励信号频率和输出的梯形波波形是可变的,那么TB周期和TL周期就要对应不同的频率控制字K。用K_1表示TB内的频率控制字,K_2表示TL内的频率控制字。设置TB内的频率控制字Fword_1[19:0]、TL内的频率控制字Fword_2[19:0]和频率控制字寄存器r_Fword[19:0],将频率控制字寄存器r_Fword[19:0]与累加寄存器Fcnt[19:0]相加,和为Fcnt[19:0]。设置一个二选一多路选择器,每当波形ROM表的地址rom_addr[9:0]的值<511时,r_Fword[19:0]=Fword_1[19:0];否则,r_Fword[19:0]=Fword_2[19:0]。由DDS原理可知,TL和TB的相位角都为π,则根据式(4)以及T=1/f可得:

TB=220/2×50MHz×K_1

(5)

TL=220/2×50MHz×K_2

(6)

输出激励脉冲信号频率f的计算公式为

f=1/TB+TL

(7)

改变K_1的值即可改变TB的值,进而改变梯形波的时间。整个TB不超过30 μs,那么频率控制字K_1≥220/(2×50 MHz×30 μs)=350。正常工作时TB一般为12~30 μs,则得出正常工作时频率控制字K_1范围为350~824;改变K_2的值即可改变TL的值,进而改变整个输出激励脉冲信号的频率。正常工作时,输出激励脉冲的频率不大于20 kHz,则TL≥20 μs,可得出正常工作时频率控制字K_2范围为1~524。

2.3 相位调制器模块

相位调制器中需要一个同步寄存器,用于寄存输入的相位控制字并将该寄存器的值作为初相位。该设计中波形ROM表的地址线是10位,可设置相位控制字Pword[9:0]和相位控制字寄存器r_Pword[9:0],因此高10位累加寄存器数字Fcnt[19:10]作为累加寄存器的输出,再与相位控制字寄存器r_Pword[9:0]相加,最后的和为波形ROM表的地址rom_addr[9:0]。本文设计的Pword[9:0]可以在0~1023之间,但一般情况下默认Pword[9:0]为0。

2.4 幅值调制模块

由ROM输出的梯形波数据DA_data幅值为二进制数11111111,该数值是存储在ROM表的初始值。要实现输出信号幅值可调,将输出梯形波数据DA_data乘于一个变化的系数,就可以得到变化可调的电压幅值输出。可设幅值控制字Change[3:0],设置乘法寄存器数字DA_data0[11:0]作为ROM输出q和Change相乘结果的输出,再使DA_data [7:0]= DA_data0[11:4],取乘法寄存器输出的前8位,相当于输出除于16,则DA_data [7:0]输出值就为q×change/16。

2.5 DDS系统顶层模块

DDS模块为各个子模块的集合,原理图如图4所示。设计了ROM模块,用于波形数据的存储和输出,地址线rom_addr[9:0]作为ROM的输入,梯形波数据q[7:0]作为ROM的输出;设计了幅值调制模块,将ROM输出q与幅值控制字Change相乘后的值寄存于乘法寄存器中,再取该乘法寄存器输出的前8位,从而得到DA_data [7:0],作为DDS模块的输出;设计了3个寄存器:累加寄存器Fcnt[19:0]、频率控制字寄存器r_Fword[19:0]和相位控制字寄存器r_Pword[9:0];设计了相位调制器模块,用于调制初始相位,设置了一个加法器,Fcnt[19:10]与r_Pword[9:0]相加,其和作为波形ROM表的输入地址rom_addr[9:0];设计了相位累加器模块,为DDS模块的核心模块,相位累加器的溢出频率就是DDS系统输出信号的频率,设置了一个加法器,将频率控制字寄存器r_Fword[19:0]与该加法器的和累加寄存器Fcnt[19:0]相加,完成Fcnt[19:0]的累加;设置了一个二选一多路选择器:rom_addr[9:0]的值<511时,r_Fword[19:0]=Fword_1[19:0],否则r_Fword[19:0]=Fword_2[19:0]。将上述所有模块封装为一个DDS模块。

图4 DDS模块原理图

在DDS模块中,需要输入激励Fword_1[19:0]和Fword_2[19:0]来驱动该模块,可以使用In-System Sources and Probes Editor进行调试。它有一个对应的IP核逻辑模块,需要被例化到FPGA内部。可通过Sources端口来驱动FPGA内部信号,即工程输入;通过Probes功能来探测内部节点的逻辑值,即读出工程输出。调试者连接JTAG就可为FPGA 添加激励并观察响应。

创建In-System Sources and Probes Editor IP核,名为CtrlWordSource。在配置页面中,设置Probe为 0 bit,Source为20 bits。例化CtrlWordSource_K1、Ctrl-WordSource_K2和CtrlWordSource_C,分别将source连接到Fword_1、Fword_2和change。通过修改source值,驱动值通过JTAG写到FPGA中,即可完成DDS模块中频率控制字的输入和幅值的调制。该DDS顶层模块原理图如图5所示。CtrlWordSource_K1、CtrlWordSource_K2和CtrlWordSource_C 3个IP核分别连接DDS模块的Fword_1、Fword_2和change的输入,本设计Pword默认连接0,再将这3个IP核和DDS模块封装为一个DDS顶层模块。clk和reset_n为DDS顶层模块的输入, DA_data [7:0]为DDS顶层模块的输出,是激励脉冲信号的数字信号。

图5 DDS顶层模块原理图

2.6 外接电路设计

本文设计的外接电路包括DAC电路和低通滤波电路。FPGA中ROM的输出与DAC芯片的输入相连,DAC芯片还需连接到运算放大器上进行电流到电压的转换,最后才能输出所需波形的模拟信号。由于每次在ROM中输出数据的时间间隔为20 ns,ROM地址增加的时间间隔为40~100 ns,需要选择电流建立时间足够短的DAC芯片以及转换速率(SR)和带宽要足够大的高速运算放大器才能满足工作要求。所以DAC芯片选用了8位高速电流输出的DAC0800LCM芯片,该芯片采用SOP小外形封装,具有快速输出电流建立时间(100 ns)。高速运算放大器选用AD8056电压反馈运算放大器,AD8056芯片的转换速率(SR)为1400 V/μs,在40 MHz时只有0.1 dB衰减,-3 dB增益带宽最高可达300 MHz,电流建立时间只需20 ns,完全满足高速的工作要求。

本文设计的DDS时钟频率高达50 MHz,输出最大频率为30 kHz,因此采用无源的RC低通滤波器。根据信号完整性理论可知,信号的带宽BW和上升时间RT的关系为:BW=0.35/RT。由上文可知,上升时间RT为梯形波周期TB的1/5,正常工作时TB一般为12~30 μs,所以信号的上升时间RT最小值为2.4 μs。计算可得信号带宽BW为145.8 kHz,则设置的低通滤波器的截止频率应大于145.8 kHz。因此,在对信号完整性和梯形波谐波分量,以及DDS系统存在的杂散和干扰进行综合分析后可知,设计一个电阻为51 Ω、电容为10 nF、截止频率为312.2 kHz(大约为最大输出信号频率的10倍)的RC低通滤波器可满足需求。该RC低通滤波器可以使输出的低于30 kHz的梯形波信号以很低的衰减通过,可有效滤除DDS系统中存在的杂散和干扰,且信号完整性较好,输出的激励脉冲信号的梯形波不会出现较大的失真。

外接电路原理图如图6所示。DDS顶层模块输出的DA_data [7:0]接入DAC0800LCM芯片的8位数据输入;DAC引脚2的VREF+接入2.5 V参考电压,并且和引脚3都接入电阻值为510 Ω的RREF,引脚1、引脚7分别接入电源电压±5 V,并接入100 nF去耦电容;引脚8的IOUT作为DAC的电流输出,连接一个510 Ω电阻后接到高速运算放大器AD8056的反向输入端,则IOUT=DA_data×VREF+/256×RREF。高速运算放大器AD8056的反馈电阻RF与DAC参考电阻RREF相等,阻值为510 Ω,则运算放大器放大倍数为-1;引脚8、引脚4分别接入参考电压±5 V,并接入100 nF去耦电容。经过AD8056后电压信号流入低通滤波电路,连接51 Ω的电阻到负载,再连接10 nF的电容到GND,该低通滤波器的截止频率fc=312.2 kHz,图中负载为1 kΩ的电阻。

图6 DDS系统外接电路原理图

3 仿真验证

3.1 DDS模块的软件仿真验证

使用Quartus II中集成的Modelsim-Altela软件对Testbench文件的激励输入在上板运行前进行仿真。

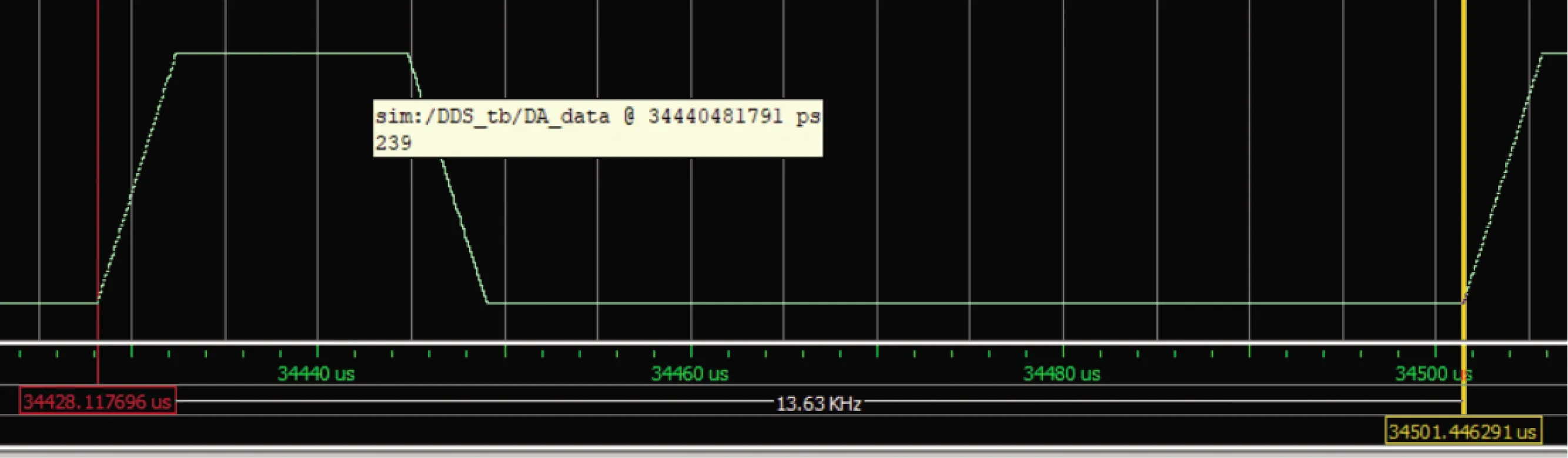

在Testbench文件中,初始化K_1为500,K_2为200,C为15,代入式(5)、式(6)和式(7)进行计算,可得:TB=20.97 μs,TL=52.43 μs,f=13.62 kHz,波形仿真结果如图7所示。输出激励脉冲信号的频率为13.66 kHz,幅值为239,与理论结果相符。

图7 DDS模块输出信号波形仿真结果

对DDS模块所实现的调节输出梯形波波形和输出激励脉冲信号频率功能进行验证:改变频率控制字K_1可改变TB的值,即可改变梯形波的波长;改变频率控制字K_2可改变TL的值,即可改变输出激励脉冲信号的频率;改变幅值控制字C可改变输出激励脉冲信号的幅值。在Testbench文件中,初始化K_1为400,K_2为100,C为8,代入式(5)、式(6)和式(7)进行计算,可得:TB=26.21 μs,TL=104.86 μs,f=7.63 kHz,波形仿真结果如图8所示。

图8 DDS模块输出信号波形仿真结果

由图8可知,输出激励脉冲信号的频率为7.63 kHz,幅值为127,与理论结果相符。验证了改变频率控制字K_1可改变梯形波的波形,改变频率控制字K_2可改变输出激励脉冲信号的频率,以及改变幅值控制字C可改变输出激励脉冲信号的幅值,由此验证了DDS模块设计功能的实现。

3.2 顶层模块板机验证

在上板运行时,输入的信号是无法提前获取进行仿真的实时信号,Modelsim-Altela仿真不能实现。所以,在上板运行时需要一个实时的信号分析工具SignalTap II,它可以获取FPGA内部的实时信号进行调试分析。SignalTap II将采样的经过修改的综合门电路信号存储到内部RAM中,通过JTAG传到PC机上,可以对FPGA的输入、输出管脚及任意内部信号进行逻辑分析。

使用In-System Sources and Probes Editor工具修改source值:K_1[19:0]=400,K_2[19:0]=300,C[19:0]=8。图9为DDS信号源输出的梯形波激励脉冲信号的SignalTap II实时数据采样波形图。

图9 SignalTap II实时数据采样输出波形图

由图9可知,输出的梯形波激励脉冲信号与所设计信号的波形和频率一致,验证了本文所设计DDS系统可实现在板机上运行且设计功能可以完全实现。

3.3 外接电路仿真

使用软件Multisim 14对数模转换(DAC)电路和低通滤波电路进行仿真,该外接电路如图10所示。

图10 在Multisim14上外接电路仿真图

XFG1模拟由DAC输出的2.5 V的30 kHz激励脉冲信号;XFG4为0.1 V的1 MHz的方波信号,模拟了DDS系统存在的杂散和干扰高频信号;通道A为通过DAC电路后输出的信号;通道B为通过RC低通滤波电路过滤后的信号。设定电容值为10 nF、电阻值为51 Ω,观察在Multisim 14仿真的通道A和通道B上输出的信号波形,结果如图11所示。

图11 输出仿真波形图

由图11所知:波形保持较好,输出信号毛刺干扰大部分被滤除,且输出的信号也不会出现较大变形。该激励脉冲的波形可较好地实现驱动压电喷墨头。

4 结束语

本文基于FPGA的DDS原理,为压电式喷墨打印喷头设计了一个梯形波激励脉冲信号源。在Quartus II软件上完成了梯形波脉冲信号源的逻辑设计、综合和仿真,并使用Multisim 14软件对硬件电路进行仿真。仿真结果证明:输出的梯形波脉冲信号的幅值、脉宽以及输出频率可调,并且实现了过滤高频杂散和干扰的功能。该系统使用Verilog HDL硬件编程语言的FPGA程序具有良好的可读性和可移植性,而且该系统硬件电路设计使用简单,控制方便。可输出电压幅值为0~2.5 V、梯形波脉宽为10~25 μs和输出信号频率为0~30 kHz的梯形波脉冲信号,可较好地匹配压电式喷墨打印喷头。该激励脉冲信号经过进一步调制放大后可作为压电式喷墨头的驱动电源,从而驱动压电式喷墨头使其正常工作。调整该设计中的参数也可以输出频率范围更大的信号,并可适用于其他领域。