一种900V 大功率MOSFET 的工艺仿真设计

2021-05-10刘好龙

刘好龙,周 博

(中国电子科技集团公司第四十七研究所,沈阳110000)

1 引 言

高压功率MOSFET 器件具有优异的性能,在武器装备的研制过程不可或缺,它为机载、舰载、星用、导弹、雷达、卫星等军工设备提供驱动,其市场占有率高,并将逐渐持续增高。欧美国家对高性能MOSFET 产品进行技术垄断并对关键产品实行禁运,国内军工单位面临断货风险,自主研制势在必行。高压功率MOSFET 的制造工艺对产品的成功研制起着关键作用,因此对工艺进行仿真具有重大现实意义。为得到高可靠的半导体器件,需要反复进行工艺试验,最后确定最优的工艺条件,这一过程需要大量时间与金钱的投入;利用仿真技术,就不再需要反复的实际的工艺试验,只要通过工艺模拟就可达到目的,极大节省成本。因此,工艺模拟已成为半导体器件工艺设计、优化的一种重要工具,得到了快速的发展[1]。

2 工艺模拟

半导体工艺模拟是利用计算机技术对半导体生产加工过程中的各工艺条件、工艺步骤进行仿真,可求解出半导体器件内部的杂质分布和结构特性。在此以某型大功率MOSFET 的使用需求为例设计工艺及电学仿真方案。该器件工作电压为900V。采用仿真软件为Silvaco 和Synopsys。

2.1 外延材料工艺模拟

对于功率VDMOS,每个MOS 结构都有八部分电阻组成。对于高压器件,外延层漂移区的电阻以及JFET 区电阻对导通电阻起主要作用[2]。为充分优化漂移区厚度及电阻率的设计,需进行工艺仿真。

外延层厚度及电阻率的选取可事先通过理论计算的方式初步得出结论。为使其更准确,需要通过工艺模拟细调。由于工艺条件,尤其是高温过程例如阱推进工步对击穿电压的影响很大,因此,在进行模拟前,要先确定阱推进工艺条件。经设计,此处选取P 阱注入能量80keV,注入剂量8×1013cm-2,阱推进温度1160℃,时间8 小时。

当外延层电阻率取25 Ω·cm 时,仿真结果如图1 所示。

图1 外延仿真结果(电阻率25Ω·cm)

由仿真结果来看,击穿电压达850V 左右,结深为5.5μm 左右。此时击穿电压偏低。

当外延层电阻率取27 Ω·cm 时,仿真结果如图2 所示。

图2 外延仿真结果(电阻率27Ω·cm)

由仿真结果来看,击穿电压达930 V 左右,结深为5μm 左右。此击穿电压已能满足要求。

同时,由注入形成的高浓度衬底经过阱推的热过程会向外延层反扩散。对反扩散的结深进行工艺模拟,结果如图3。此时反扩散结深在6μm 左右。基于仿真结果,结合理论分析,最终选取外延层电阻率为 27Ω·cm,厚度为 82.5μm。

图3 外延层反扩散结深仿真结果

2.2 掺杂区工艺模拟

在VDMOS 器件中,掺杂区主要是指P 阱区和N+有源区。P 阱区是器件经硼注入后高温推进得到的,其结深对器件的击穿电压有很大影响;同时P阱区的掺杂浓度对器件的沟道表面浓度、沟道长度有至关重要的影响,从而影响器件的开启电压。因此P 阱区的结深和掺杂浓度是非常重要的参数,需要通过工艺模拟得出最优的工艺条件[3]。

N+是VDMOS 器件的源区,主要是通过注入高浓度的N 型杂质,经过退火后形成的。N+区的两个重要工艺参数是注入剂量和结深,对VDMOS 器件的开启电压有很大的影响。N+区的剂量越大,其横向扩散就越大,在P 阱区结深和掺杂浓度不变的情况下,沟道的长度就会变短,进而影响器件的开启电压。所以N+的结深必须控制得恰当。

N+源区注入的杂质是磷或者砷,浓度非常大,这样可以减小N+与源金属之间的欧姆接触,从而减小源区接触导通电阻。由于砷的扩散系数比磷小很多,对于要形成N+的浅结工艺更易实现与控制,因此,在此采用注入砷形成N+区。

结合工艺条件,对源N+区域、P-阱区、中央P+区域进行掺杂浓度分布仿真。各掺杂区工艺条件如表1 所示。

表1 各掺杂区注入工艺条件

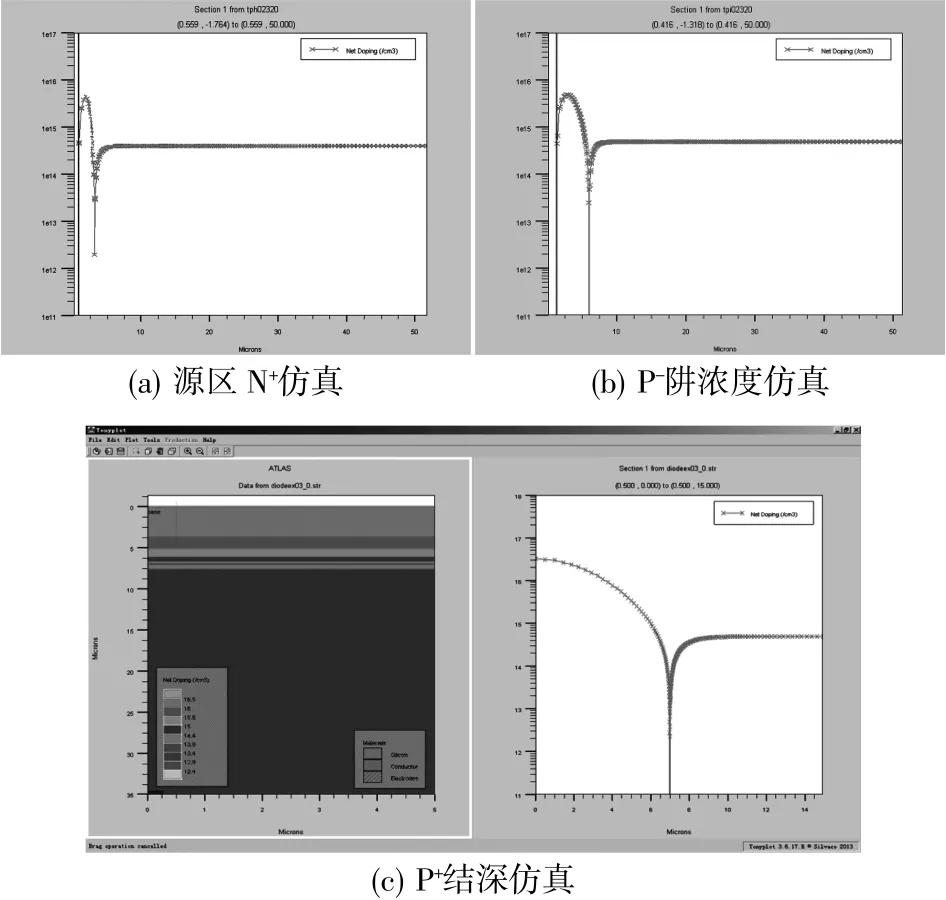

各掺杂区仿真结果如图4 中各图所示。从仿真结果可以看到,各区域的浓度分布基本上达到了预期效果,得到的各区域结深也符合预期。

图4 掺杂区工艺仿真结果图

2.3 器件模拟

半导体器件模拟是在给定器件结构模型及工艺条件后,通过模拟程序,在器件模型上施加指定的偏置,得到器件输出特性,通过不断对其加以分析优化改进,最终可获得符合要求的器件电学特性[4-5]。

先描述器件结构,模拟元胞模型,如图5 所示。

图5 元胞模型仿真结构图

然后对元胞模型进行器件特性模拟,模拟出器件的开启电压和输出特性曲线,如图6 所示。

由于理论计算的结果与实际参数要求反差很大,所以在器件模拟仿真过程中,要不断的调整器件相关尺寸、调整网络优化,直至得到理想器件输出特性参数为止[6-8]。

图6 元胞模型器件特性仿真结果

3 工艺验证

根据器件设计的结构参数,对比模拟和实验结果,根据流片总结经验,最终得出较为合理的工艺,具体流程如下:

备片→清洗→热氧化SiO2→光刻P+环区→腐蚀→清洗→预氧→硼注入→清洗→退火→光刻有源区→腐蚀→清洗→栅氧化→淀积多晶硅→多晶掺磷→光刻多晶→腐蚀→硼注入→腐蚀→阱推进→光刻N+区→磷注入→清洗→LP/PESiO2→增密→光刻引线孔→腐蚀→清洗→溅射Al→光刻Al→腐蚀→LP/PE SiO2/Si3N4→刻钝化→腐蚀→清洗→合金→背面减薄→金属化→测试。

为了验证由仿真确定的总体的工艺流程和结构参数的合理性,进行批次性流片验证,结果电参数满足要求且一致性较好,说明了仿真设计的合理性和结构实现的正确性。

表2 测试结果

封装完成后,需要对器件进行末测,测试在STS8103A 分立器件测试系统、LX9600 动态参数测试系统上完成,测试包括静态和动态参数的测试。经测试,参数满足设计要求,具体测试结果见表2。

4 结 束 语

设计仿真方案并利用Silvaco 和Synopsys 对外延层材料、重要工步、器件的电学特性等进行模拟仿真,最终确定了各相关设计参数及工艺条件。经实际流片及测试,工艺实现及电学性能达到了预期,证明对该类器件的仿真设计思路及方法确实具有可行性,对大功率MOSFET 产品研制有所助益。