半导体器件早期失效筛选方法

2021-04-25张莉萍

张莉萍

【摘 要】为了获得更高的产品质量和可靠性,降低产品早期失效率,老化筛选一直是半导体生产测试的常规流程。但是器件老化非常耗时,而且会带来高昂的成本。论文讨论在何种条件下可以减少和取消器件老化,并提出了既能保证可靠性又能经济地筛选早期失效的有效方法——高电压应力和IDDQ测试方法。

【Abstract】In order to obtain higher product quality and reliability, reduce the early failure rate of products, aging screening has always been the routine process of semiconductor production testing. However, device aging is time consuming, and it will bring high costs. The paper discusses the conditions under which device aging can be reduced and eliminated, and proposes effective methods that can ensure reliability and economically screen early failure, namely high voltage stress and IDDQ testing methods.

【关键词】早期失效;老化;高电压应力;IDDQ测试

【Keywords】early failure; aging; high voltage stress; IDDQ testing

【中图分类号】TN303 【文獻标志码】A 【文章编号】1673-1069(2021)03-0137-03

1 引言

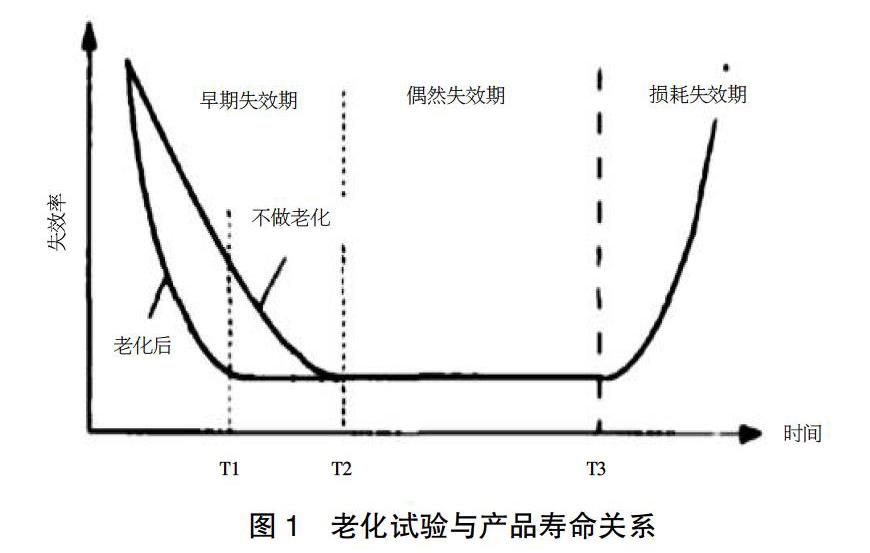

典型的半导体器件产品生命周期的可靠性通常用称为“浴盆曲线”的失效率曲线来表示,失效率随时间变化可以分为三个阶段:早期失效期(Infant Mortality Region)、偶然失效期和耗损失效期。

在第一个阶段早期失效期,半导体器件的失效率开始比较高,随着时间的推移快速下降。随后半导体器件进入第二个阶段的偶然失效期,在这个阶段中半导体器件长时间保持很低的、稳定的失效率,这个阶段的失效往往是由于施加了过大应力造成。最后半导体器件进入耗损失效期,在这个阶段失效率开始快速上升,造成失效的原因是产品长期使用所造成的材料和结构老化和疲劳。

在目前的产品和工艺中,由于工艺开发过程中采用了晶圆级可靠性或内置可靠性(BIR,Build in Reliability)技术,以及在产品设计过程中使用可靠性相关的设计规则和可靠性建模技术,因此,在使用寿命期间的耗损失效实际上已经不存在了,产品可靠性失效主要由存在潜在缺陷的早期失效所主导[1]。产生这些潜在缺陷的主要原因是在器件加工过程中,由于微小的异物、颗粒,以及制造设备引起的偏差和尺寸偏差等造成。

早期失效期一般为半年到一年时间,在这段时间当中器件存在较高的失效率,是影响使用可靠性的重要阶段。

2 早期失效的故障模式

随着集成电路集成度的不断提高,线宽、线间距越来越小,栅氧化层越来越薄,微小的残留物和颗粒对产品可靠性带来的影响越来越大。同时,芯片面积不断增大,相应芯片上栅氧总面积增大,存在缺陷的概率增加,栅氧化层可靠性问题逐渐成为器件早期失效的主要问题。

所以,栅氧化膜泄漏(Leakage)和金属异物引起的功能不良和泄漏不良是早期失效的主要故障模式。

3 早期失效的筛选方法

早期失效筛选就是要诱发潜在缺陷提早失效,让器件提前进入稳定状态,最终让产品以规定的失效率水平,在规定的使用寿命内工作。

常规应用最广泛的筛选方法就是老化,让半导体器件在高温、高电压条件下进行超负荷工作,从而使缺陷在短时间内出现。

如图1所示,不经过任何老化筛选措施,器件需要在T2时间后才能从早期失效期过渡到偶然失效期,经过老化筛选后,器件可以提前在T1时间进入失效率较低的偶然失效期[2]。

老化过程需要芯片工作,保证逻辑电路原则上达到80%以上的翻转率,通过这一过程筛选临界的、具有潜在缺陷的或者是存在制造偏差的器件。

老化筛选按照不同的产品应用要求,一般需要24~168h,某些军用及航空器件甚至需要长达几百小时的老化,因此,老化筛选消耗的时间有时高达整个产品测试时间的80%左右。

同时,老化还会带来高昂的硬件成本,由于每个老化板只能容纳有限数量的器件,产品面积越大,容纳数量越少。与此同时,每个老化炉只能放置规定数量的老化板,以144脚封装的产品为例,如果采用24h老化,老化成本占产品总成本的30%左右。

因此,从产品尽快上市和控制成本的角度来考虑,老化并不是筛选早期失效产品的经济有效的解决方法。

本文主要是讨论了IDDQ测试和高电压应力测试在筛选早期失效产品上的应用及其效果。

3.1 高电压应力测试

高电压应力测试是通过实施高压脉冲来筛选早期失效的方法,建议使用DFT测试模式,以获得较好的故障覆盖率。可以在40nm的flash IP的产品中采用SCAN和MBIST测试,实现故障覆盖率DC95%和AC80%。

台积电研究了一种0.25um逻辑技术6晶体管SRAM在FT(Final Test)环节的DVS筛选测试方法,并将改进后的DVS测试方法应用于台积电0.18um逻辑技术6晶体管SRAM的CP环节测试。结果表明,该方法在CP环节能有效地筛选出在应用中可能失效的产品。实验通过一组经过DVS筛选的样本,和另一组是正常的未经过DVS筛选的样本,然后将这两组芯片放入老化炉中进行48h的老化研究。与未经过DVS筛选的样本相比,经过DVS筛选的样品,老化后失效率降低了约60%[3]。

由于CP环节的DVS筛选可以节省不必要的封装成本和测试时间,在40nm的flash IP的产品方面,首选在CP测试环节应用DVS筛选方法,在1.4倍VDD下运行测试向量累积时间500ms,随后比较DVS前后standby电流的变化量,将超出控制限的芯片视为存在潜在缺陷的芯片。

试验选用三个样本批次,每个批次13989颗。试验结果表明,经过DVS测试的比未经DVS测试的批次多筛选出的不良品在0.22%左右(见表1)。

DVS筛选出来的失效样品,经PFA分析为金属颗粒和残留。

同时,在三个批次,每个批次抽取2000颗样品追加24h的验证老化,老化条件为高温125℃、Vcc(max)、24h,三个批次都没有继续产生失效。

但是需要注意的是,高电压应力筛选测试不适合带有内部稳压电路的器件。

3.2 IDDQ测试

传统的功能测试和扫描测试是基于逻辑电平的故障检测,与传统的测试不同,IDDQ测试的是CMOS集成电路中所有节点都处于静止状态时的电源电流,器件内的缺陷如氧化层短路、泄漏,无法通过常规的功能测试和扫描测试检测出来,但可以被IDDQ测试方法检测出来。

R. Kawahara[4]设计了一个对比试验来验证IDDQ的有效性,试验选择两批1.0um工艺的样品,第一组176459个样品作为对照样本,在老化前只进行常规的功能和参数测试,剔除不合格品后进行老化,老化结束后再进行一次常规的功能和参数测试。另一组31919个样品则在常规的功能和参数测试后添加一项IDDQ测试,剔除不合格样品后再进行老化,老化结束后也进行功能和参数测试。老化试验条件是125℃、VDD=7.0V、6h。经过试验发现,IDDQ测试筛选使得器件的早期失效率减小了二分之一。

40nm工艺产品由于工艺背景漏电流大,好坏器件之间的IDDQ差别小,常规的IDDQ测试的有效性受到影响。因此,采取在低温-40℃环境下测试以减少背景漏电流的方法,同时,采用Delta(min-max)IDDQ测试方法,通过同一芯片内连续20个测试向量下的IDDQ差分值来获得Delta值,将Delta的结果与设定的阈值比较,以此判断芯片的好坏,解决了IDDQ测试有效性问题,对缺陷芯片的筛选能力更强。

在测试过程中,考虑到IDDQ测试的有效性,样品首先进行DVS筛选,然后进行常规的功能和参数测试,再进行IDDQ筛选测试。

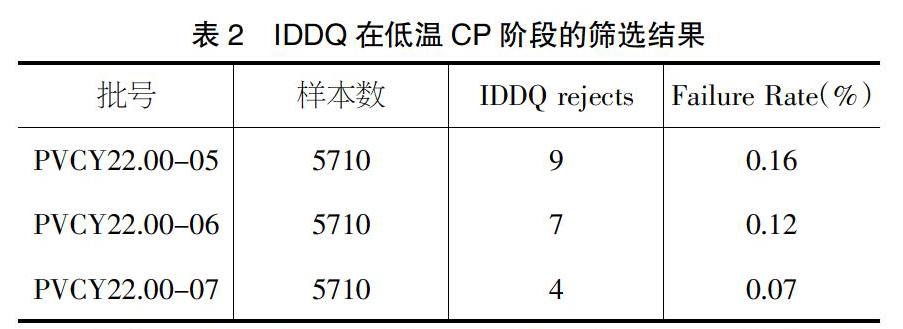

试验选择三个批次,每个批次5710个样品,通过了功能、参数及DVS测试合格的样品,在IDDQ测试中继续产生0.1%左右的失效(见表2)。

表2 IDDQ在低温CP阶段的筛选结果

收集通过了DVS筛选及常规的功能和参数测试但IDDQ测试失效样品进行分析,PFA分析主要表现为栅氧短路、针孔。

同时,从三批次中筛选出来的良品中各抽取3200颗样品进行老化验证,老化条件为Vcc(max)、125℃、48h,三个批次的样品都没有继续产生失效。

可见IDDQ测试技术,结合了高电压应力测试,可以筛选出器件中大部分栅氧缺陷和金属颗粒引起的主要故障,对于筛选存在潜在缺陷的早期失效是十分有效的。

4 结语

IDDQ和高电压应力测试可以有效地筛选存在潜在缺陷的早期失效的产品,同时,这个方法不需要额外的老化板和老化炉的投入,是一种既能保证可靠性又经济的方法,可以在一定程度上取代老化过程,但是对于军用、航空等产品应用,老化过程还是必不可少的,有效地篩选早期失效的方法还需要半导体制造商进行不断的学习和探讨。

【参考文献】

【1】J.A. Van der Pol,E.R. Ooms,T. Van 't Hof,et al.Impact of screening of latent defects at electrical test on the yield-reliability relation and application to burn-in elimination[C]//IEEE International Reliability Physics Symposium. IEEE,1998.

【2】王茉.军用集成电路老炼筛选技术研究[D].哈尔滨:哈尔滨工业大学,2012.

【3】Tsao C Y,Shiue R Y,Ting C C,et al.Applying dynamic voltage stressing to reduce early failure rate[C]//IEEE International Reliability Physics Symposium. IEEE,2001.

【4】Kawahara R,Nakayama O,Kurasawa T.The effectiveness of iddq and high voltage stress for burn-in elimination[C]//IDDQ Testing,1996.IEEE International Workshop on. IEEE,1996.