时间触发光纤通道节点设计与实现*

2021-04-24詹鹏,周新

詹 鹏,周 新

(1.中国西南电子技术研究所,成都 610036;2.空军装备部驻成都地区第三军事代表室,成都 610036)

0 引 言

航空电子系统的发展经历了分立式、联合式到综合化的发展过程,机载综合化电子系统变得越来越复杂。作为航电系统信息传输的通道,机载总线网络变得越来越重要,综合化航电系统对机载总线网络的传输速率、确定性、可靠性等都提出了较高要求。常用的控制器局域网(Controller Area Network,CAN)、以太网等总线网络采用了事件触发传输方式,数据传输时刻是随机的,当多个节点同时发起传输时可能发生冲突,在网络负荷较重时,数据传输的及时性无法得到保证。时间触发传输通过分时复用的方法,将整个信道的传输时间划分为若干时隙并分配给各个节点,可有效避免数据包争用物理链路,解决了网络可能存在的冲突、数据帧拥塞排队问题。时间触发传输通过全局时间同步实现无冲突的数据传输,数据传输的最大时延是可预知的。时间触发传输与事件触发传输相比,在传输确定性上有很大优势。采用时间触发传输机制的常用总线包括时间触发协议(Time-triggered Protocol,TTP)、时间触发CAN(Time-triggered CAN,TT-CAN)、时间触发以太网(Time-triggered Ethernet,TTE)[1]等,并受到了广泛的关注和应用。

光纤通道(Fiber Channel,FC)是美国国家标准委员会制定的高速串行传输协议。FC具备高带宽、高可靠性、高稳定性等优点,采用了光纤互连,抗电磁干扰能力强,业界在此基础上提出了光纤通道航空电子环境(Fibre Channel Avionics Environment,FC-AE)协议族。FC在F-35、“长弓阿帕奇”等项目中已得到了成功应用。FC采用了交换式全双工通信方式,不存在数据冲突问题,但交换机的存储转发机制同样使通信延迟具有不确定性(网络交换排队延迟)。普通的FC采用事件触发传输方式,由于传输速率较高,当网络负荷较低时数据传输时延较低,可满足常规应用需求,然而在网络负荷较重的场合,数据传输时延的影响就会凸显出来。借鉴时间触发传输思想,可在FC网络中引入时间触发传输机制,从而提高数据传输的时间确定性。

考虑到FC传输确定性问题,文献[2]提出了一种基于令牌桶的优先级和加权轮转相结合的调度算法,以提高FC的实时性。针对时间触发传输的时隙分配问题,文献[3]提出了基于稀疏模型的时间触发光纤网络调度方案,提高传输确定性。针对FC的协议实现问题,文献[4]基于FPGA设计实现了普通光纤通道数据收发系统;文献[5-6]采用FPGA设计实现了FC节点;文献[7]基于FPGA实现了FC协议CRC的并行高效算法,使消耗的FPGA逻辑资源更少;文献[8]基于FPGA设计实现了FC协议分析器,具备FC协议与以太网协议的转换功能。针对交换机设计实现问题,文献[9]设计实现了基于时间调度网络的光纤通道交换机,文献[10]基于FPGA实现了一种高性能、大容量的48口FC交换机。

当前介绍FC节点、交换机的设计与实现的文献较多,部分文献提出了时间触发传输概念、方案,但针对时间触发光纤通道从整体传输方案、网络同步、具体逻辑设计实现、到实物测试验证进行系统性描述的公开文献较少。本文基于时间触发传输思想,在普通FC总线的基础上对传输协议进行改进,增加时间触发传输功能,采用主从方式实现网络时间同步,仅需对网络节点终端进行协议改造的方法,提出了相应的设计方案,然后在FPGA上进行了逻辑实现,最后在实物平台上进行了测试验证。

1 时间触发传输设计与实现

1.1 总体方案设计

本文基于时间触发传输思想,在网络节点时间同步的基础上,将总线传输按周期进行划分,每个周期预先规划相应的时隙给各节点(即发送时间表),所有数据传输都由时间表来驱动。网络节点发送时间表的设计规划原则:在各个节点的发送时隙内独占链路资源,其他节点均不能使用该链路(对应的接收节点同一时刻仅接收来自唯一一个节点的数据,即不会出现同一时刻两个节点同时向同一节点发送数据)。在交换式FC网络中,交换机采用了空分交换结构,所以网络中存在多条传输链路可以互不影响地同时工作,采用手动方式设计发送时间表会较为复杂,可编写相应的时间调度算法程序来规划时隙。各个节点按照预先规划的时隙可以互不冲突地使用网络资源,在交换机中就不会存在数据缓冲、排队的现象,保证了数据传输的确定性。交换机仅需按照路由进行全速转发即可,对交换机也无特殊要求,采用普通FC交换机即可。此外,根据规划好的发送时间表,可以方便地得到各个节点的接收时间表(不同时隙接收来自不同节点的数据包)。节点在接收到数据包时,需根据接收时间表对数据来源进行验证,从而提供了一种对数据传输合规性的检测。

普通FC协议包括5层:FC-0定义了物理连接的特性、速率;FC-1定义了传输字的组成,传输信号的编解码方式以及错误控制;FC-2定义了帧、数据包的构成及传输方式;FC-3为通用服务层,作为预留扩展层;FC-4定义了不同的上层协议映射方式。本文提出的时间触发传输FC总线基于普通FC协议,总线协议分层如图1所示。

图1 时间触发光纤通道协议分层

所提出的时间触发光纤通道协议在原FC协议的基础上增加了一个时间触发控制管理层,用于实现时间触发传输功能,其他层次与普通FC相同,所以本文提出的时间触发光纤通道协议兼容于普通FC。时间触发控制管理层主要实现网络节点的时间同步,以及节点的时间触发数据传输,该层不会对收发的数据包内容作任何修改,仅通过网络时间同步后,实现对时间触发传输的控制,即控制数据包在允许的发送时间窗口将数据发送出去,而在非发送时段则对数据包进行缓存,并按照接收时间表对接收数据进行合规性检测。

基于普通FC总线协议,本文提出的时间触发传输节点的逻辑设计方案如图2所示。时间触发FC协议在FPGA逻辑上实现,主要包括处理器接口、发送缓存、时间触发传输控制、接收缓存、时间同步控制管理、配置参数、双冗余管理、FC链路收发等逻辑功能单元。

图2 节点整体设计方案框图

当有数据包需要发送时,通过处理器接口将数据写入到发送缓存中,在时间触发传输控制模块的管理下将发送缓存中的数据取出并送到双冗余管理模块中;双冗余管理模块根据配置实现对双路或者单路FC数据的输出,数据包经过FC收发逻辑和光电转换后输出到网络上。

当接收到数据包时,数据通过光电模块、FC链路收发逻辑后,双冗余管理模块根据节点冗余配置将数据送到接收逻辑中;时间同步控制管理模块对接收数据进行甄别,当检测到为同步帧时则取出数据包中的同步时间信息,并更新本地时钟;若为普通数据包则经过合规性检测后送入接收缓存中,对数据包进行缓存后通过处理器接口送给处理器。

其中时间触发传输控制、时间同步控制管理两个功能模块是实现时间触发传输的关键。采用本设计实现的时间触发光纤通道总线网络中的节点分为主节点和从节点两类(网络中主节点仅有一个,其他均为从节点),所以主/从节点在逻辑实现上存在一定的差异。

1.2 时间同步设计

为了实现时间触发传输,各个节点之间需要实现精确的时间同步,使网络中各节点的时间同步到一个统一的参考时间。时间同步通常可采用硬件和软件两种方式实现,硬件同步方法精度高,但额外的硬件增大了开销;软件同步方法采用算法实现,成本低且较灵活。

本文采用主从时间同步的软件实现方案,所有节点同步到主节点的时间,并采用软件进行时间偏移补偿,实现精确的时间同步。主从时间同步方案如图3所示,网络中设置一个主节点,其他节点为从节点,所有节点均以主节点的时间为基准,主节点采用分发同步帧(数据帧中包含时间信息)的方式实现整个网络的时间同步。

图3 时间同步示意图

为了维持各个节点时间的实时同步,主节点需要周期性地广播同步帧,同步帧的发送周期为总线周期,同步帧中包含了主节点的时间信息。在未收到同步帧的时间内,从节点靠本地时钟进行守时;当收到同步帧后,则用接收到的时间对本地时间进行更新。采用该方式可实现网络中所有节点的时间同步,且该时间同步方式无需对交换机进行修改,通用的FC交换机就可以满足应用要求,对网络硬件的改动较小。采用如上所述的分发同步帧的方式,整个网络的节点可实现时间的初同步,但同步时间精度不高,从节点与主节点之间存在一个相对固定的时间偏差,该时间偏差主要由数据包收/发时延、交换路由时延、线缆传输时延组成,偏差值通常为微秒级。

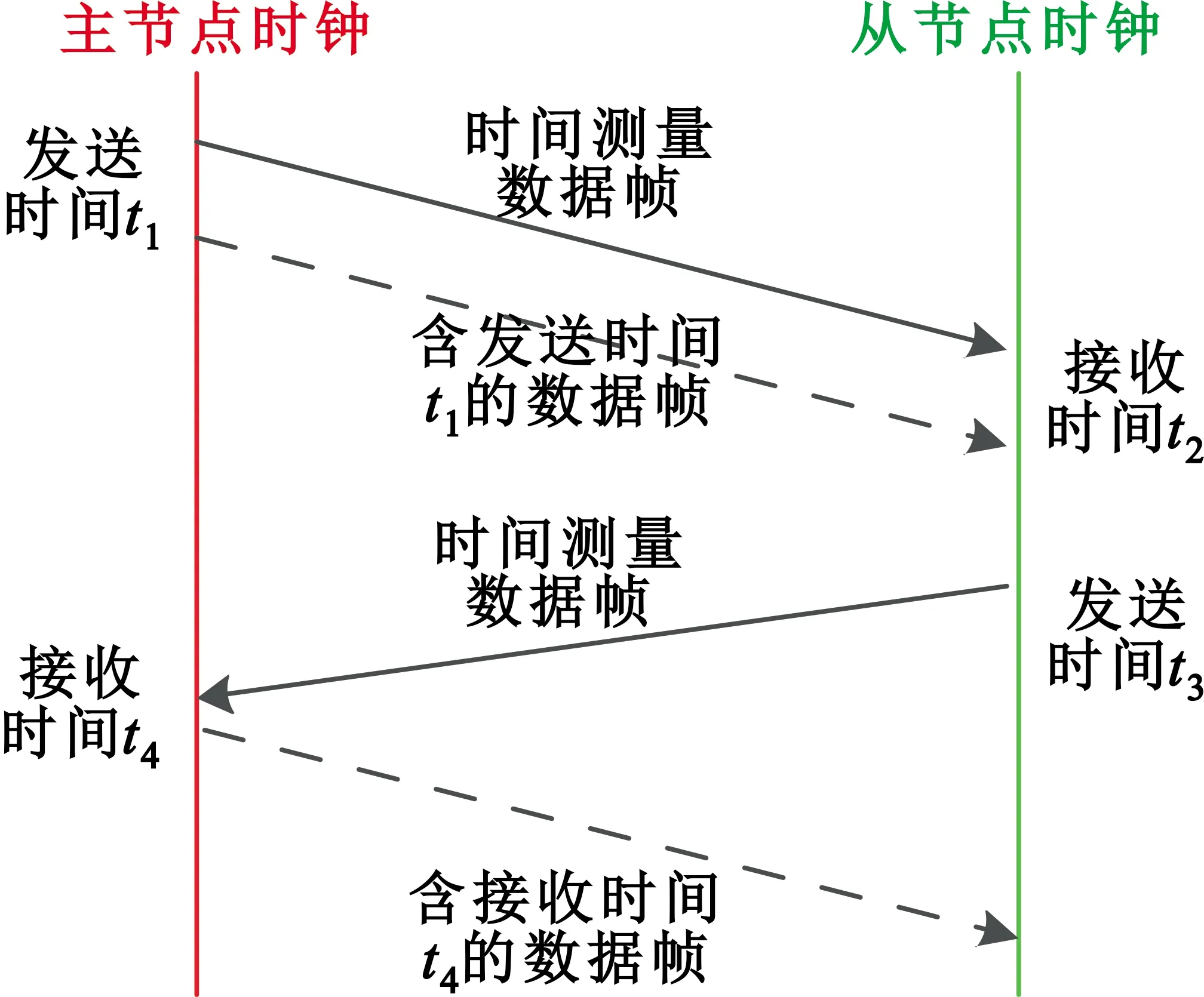

同步帧由主节点经过交换机后分发到各个从节点,由于各个从节点与主节点之间的传输路径不同,该时延也不相同。为了提高网络时间同步精度,需要对该传输时延进行测量和补偿。本设计采用与IEEE1588类似的方法对时间偏移进行测量[11],其测量原理如图4所示。

图4 时间偏移测量原理

时间偏移具体测量分两步:首先主节点向从节点发送一个数据包,主节点记录下发送时间t1,从节点记录下接收时间t2;然后从节点向主节点发送一个数据包,从节点记录下发送时间t3,主节点记录下接收时间t4。主节点通过发送数据帧的方式将记录的时间信息发送给从节点,通过式(1)计算后就可得到主从节点的时间偏差值Δt。

(1)

采用以上方法对每个从节点的时间偏移都进行独立的测量,然后在各从节点端分别进行补偿,从而提高时间同步精度。时间偏移测量过程中为了避免引入处理器软件产生的抖动,时间点记录均采用FPGA逻辑实现。此外,网络拓扑固定后,各从节点与主节点之间的时延也相对固定,所以可以仅测量一次时间偏移,并将补偿数据存储起来,后续在网络拓扑不变的情况下可直接使用。

网络节点时间同步传输的FPGA逻辑具体实现方案如图5所示。

图5 时间同步传输设计

时间同步控制管理主要完成本地守时、接收包的时间记录(用于时间补偿)、根据配置参数产生传输时隙控制信号。若节点为主节点,还需要送出总线周期信号,用于触发同步帧的产生;对于从节点而言,则应具有同步帧时间提取功能,可以从总线上接收的同步帧中提取出时间信息,结合时间补偿参数后对本地时间进行周期更新。

时间触发传输控制主要完成数据包发送时间记录(用于时间同步补偿)、时间触发传输控制,根据传输时隙使能信号控制数据发送,仅在配置的时隙内允许数据包的发送,其他时间则禁止发送,未发送的数据包则在发送缓存中等待传输时隙的开启;对于主节点而言,还具备同步帧产生的功能,根据送来的总线周期脉冲信号,周期性向网络上广播同步帧,将主节点的时间信息通过同步帧发送出去。

1.3 多缓存时间触发传输设计

时间触发传输机制通过分时复用的方法,解决了网络可能存在的冲突、数据帧拥塞排队问题,节点分时独占网络可以很好地解决网络数据传输的不确定性问题。由于FC为全双工交换网络,且采用了空分交换结构的交换机,当两个节点通过交换机传输数据时,通过交换机其他端口进行互连的多对节点之间仍可同时传输数据,且互不影响,即多个节点之间可以同时进行数据传输,数据包传输的目的地址均不相同。所以,基于空分交换结构的网络中,对于节点时隙的分配不应该是每个节点独占整个网络资源,而是独占某一条链路资源。因此,根据时隙规划,在一个总线周期内,某一节点发送到不同其他节点的传输时隙是不同的,在某个时隙仅允许传输到规定的节点。因此,若数据包发送仍然采用单发送缓存的方式则无法满足应用的需求,会存在排队阻塞的问题。为此,本文实现方案中采用了多缓存方式,以满足基于空分交换网络的时间触发传输,逻辑设计方案如图6所示。

图6 多缓存结构时间触发传输逻辑设计方案

网络中每个节点均配置多个发送缓冲区,缓冲区按照数据包发送的目的地址进行分类。在一个总线周期内,每个发送缓冲区允许输出的时隙不同,且互不重叠,允许输出的时隙通过预先离线规划进行配置。上层应用将待发送的数据按目的地址分流到不同的缓冲区进行缓存,时间触发传输控制根据节点时隙配置参数,分时取出不同缓冲区中的数据发送出去。

2 实验及结论

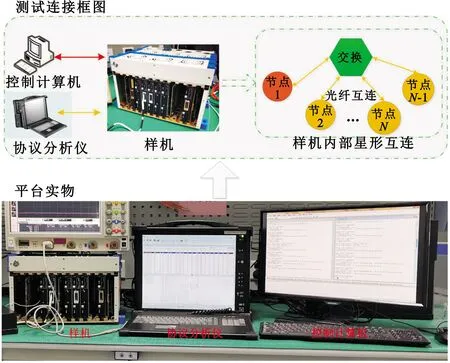

为验证文中提出的时间触发传输设计与实现方案的正确性和有效性,搭建了测试验证环境,如图7所示,主要包括样机、控制计算机和协议分析仪,选择样机中的节点进行测试验证,组建星形交换网络,由控制计算机给节点输入操作指令,使网络中的节点按照设定的时隙传输数据,使用协议分析仪可对网络上传输的数据包进行捕获、存储和分析。

图7 实物平台及测试连接框图

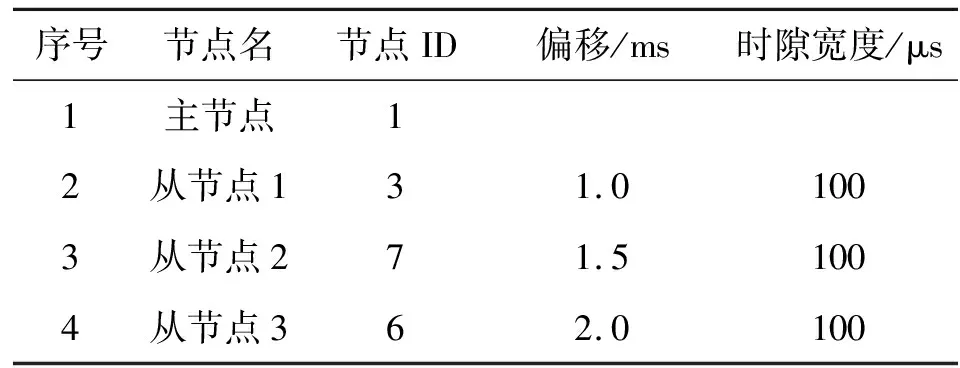

样机交换网络中选取4个节点,包括1个主节点和3个从节点,节点ID及时隙分配信息如表1所示。表中的偏移表示相对于同步帧的时间偏移,3个从节点每个周期发送一次数据给主节点,链路速率设置为2 Gb/s。

表1 节点配置表

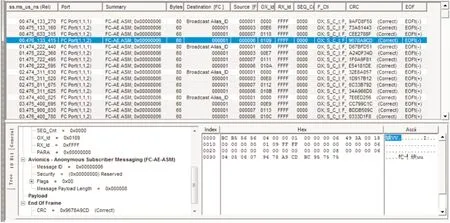

为便于操作和观察,总线周期设置为1 s,控制计算机通过串口命令控制从节点的数据发送,约1 s启动一次数据传输,通过协议分析仪对主节点的端口通信数据进行抓取。

图8为从节点不发送数据时主节点周期性广播同步帧的情况。从抓取的数据包可以看出,同步帧每1 s发送一次,周期的时间精度受主节点本地时钟影响(1 s误差接近100 μs,精度10-7),在工程应用中可以采用高精度时钟源,从而提高网络时间精度。

图8 同步帧传输截图

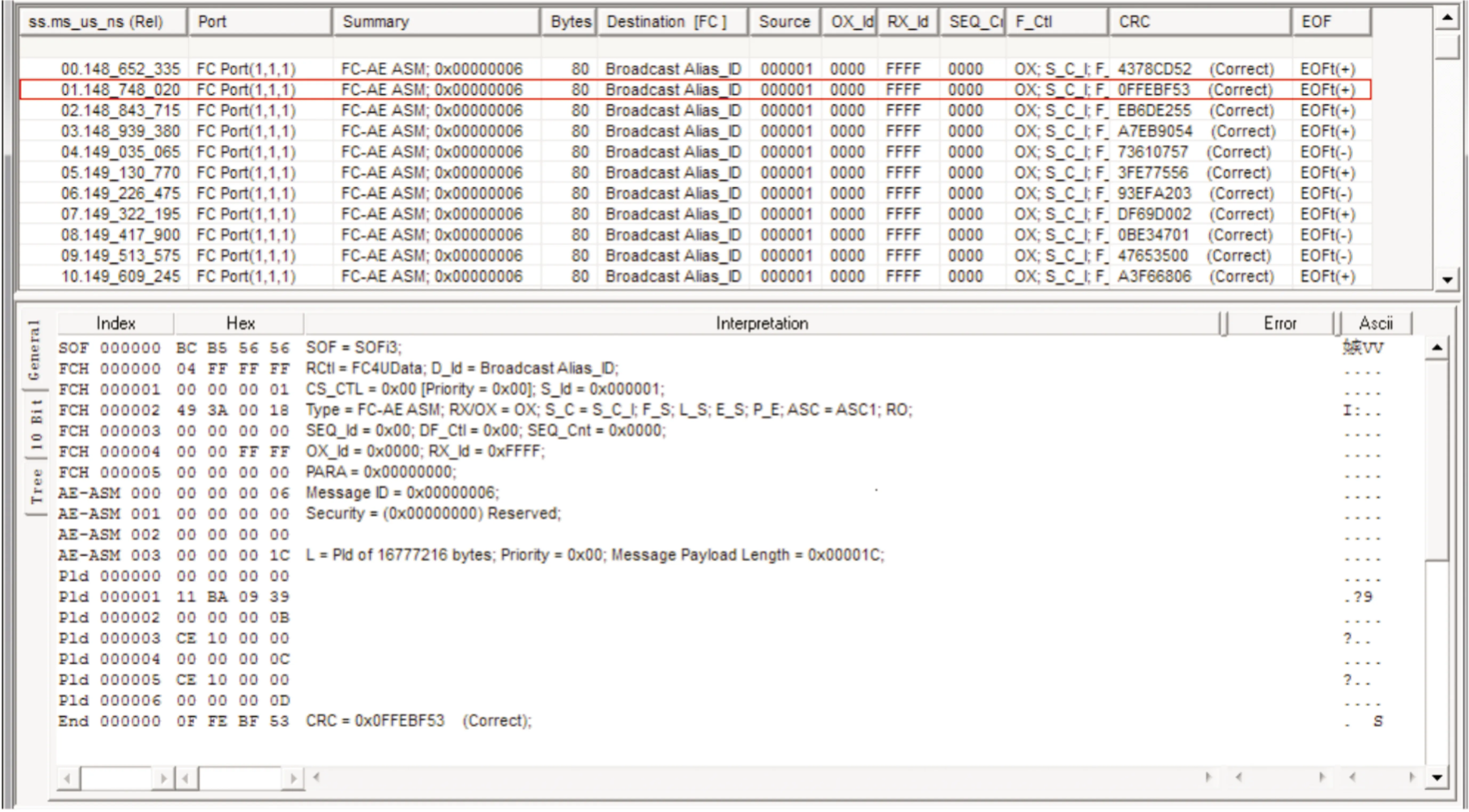

图9为3个从节点在时间触发控制下传输数据的情况。在主节点时间同步控制下,按照分配时隙,3个从节点的数据包在相对于同步帧分别偏移约1 ms、1.5 ms、2 ms的时隙完成数据传输,而在其他非规划时隙内则不发送数据包(从图中第一列的时间关系可以看出,受时间同步精度的影响,传输时间存在亚微秒级的误差),符合分配的节点传输时隙,验证了时间触发传输功能的正确性和可行性。

图9 时间触发传输测试截图

3 结 论

普通FC总线采用事件触发传输,存在数据传输时间确定性差的问题。时间触发传输能够有效避免链路争用导致的数据阻塞,保证了网络数据传输的确定性。本文提出了时间触发传输的FPGA逻辑设计与实现方案,并将实现的协议在样机平台上进行了实物测试验证,经测试满足设计要求。本文设计实现的光纤通道总线协议支持时间触发传输,且仅需要对节点协议进行修改,而交换机可以使用普通FC交换机,系统改造和升级的代价较低,实现的节点可以兼容普通的事件触发传输,在工程实际中具有一定的参考和实用价值。