基于某国产处理器的PCIE信号仿真设计

2021-04-20武天骄杭平平江保力

武天骄 杭平平 江保力

(中国电子科技集团公司第五十二研究所 浙江省杭州市 311100)

1 引言

当今世界数字技术飞速发展,无论是一位从事通信系统,计算机系统、雷达和卫星通信系统、或是高速半导体集成电路设计、高速光电收发模块、高速信号处理、高速互连器件(如高速接插件,高速数字传输电缆)等领域的研发及测试工程师都会面临信号完整性问题。

近年来,在国家集成电路国产化大背景下,国产核心器件的研发和产业化应用显得尤为关键。在工程实现中,科学有效的仿真手段和方法对解决高速接口的信号完整性问题十分重要。本文就国产某型号处理器高速PCIE 接口进行信号完整性仿真设计。

2 高速串行信号仿真设计概述

通常在PCB、电缆等互连结构中,当信号上升时间小于6 倍的信号传输延时,就需要考虑信号完整性问题,这时,这些无源结构需要用传输线的理论进行分析和设计。

高速信号的仿真设计可分为前仿真和后仿真;以及无源仿真和有源仿真。核心是分析整个链路的损耗大小,并对各个无源结构如PCB 互连通道、过孔、连接器、线缆等进行仿真优化设计,最终满足协议规范或器件的性能指标要求。

在图1 所示的系统无源链路示意图中,不同的互连结构要运用不同的模型进行表征:

(1)芯片的发送和接收:芯片的内部电路,使用AMI 模型;芯片的封装,使用SPICE 模型或S 参数模型。该部分模型通常由芯片制造厂商提供。

(2)PCB 上的过孔:为保证仿真精度,高速信号仿真中通常使用S 参数模型。该模型由信号完整性工程师使用三维电磁场仿真工具结合实际PCB 建模并仿真得到S 参数。

(3)PCB 上的传输线:通常对于参考层连续的传输线,使用传输线等效电路模型;参考层不连续的传输线,可通过三维电磁场仿真工具进行S 参数提取。

(4)连接器:使用S 参数模型或RLC 等效模型。通常,由连接器厂商提供,以S 参数模型居多。

接下来,就可以对整个无源链路进行系统级建模,按照协议或器件性能指标,把损耗预算分配到无源链路的各个互连结构中,来逐个进行仿真分析,找出优化空间和方法。如:优化PCB 布线和过孔、选用损耗更小的板材或连接器,甚至更换性能更好的芯片等等,最终的目的是使得整个系统链路的性能符合设计要求。

3 PCIE

PCI Express 简称PCIE,是一种通用的总线,是现代计算机系统内的主流总线传输接口。常用在板级互连、无源背板互连、或附加扩展接口。PCIE 链路由多条lane 组成,常见的有X1、X2、X4、X8、X16、X32,对应不同的总线带宽。

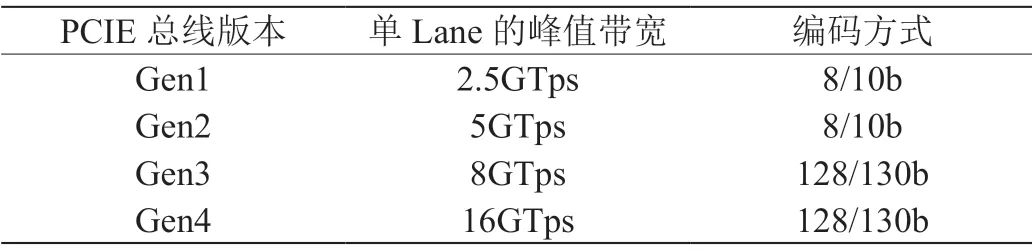

不同的PCIE 总线规范使用不同的总线频率,其使用的编码方式也不同,PCIE3.0 和4.0 版本上使用128/130b 的编码方式,较8/10b 编码效率上大大提高。如表1 所示。

表 1:PCIE 总线速率和编码方式

当前国产处理器中较常见的PCIE 还是3.0 版本,单通道最大传输速率为8Gbps,信号在输出、接收端均需满足PCIE3.0 协议的电气规范。

4 无源通道的仿真设计

4.1 耦合电容

图1:系统无源链路示意图

信号在传输的过程中,如果传输路径上的特征阻抗发生变化,信号就会在阻抗不连续的点产生反射。通常在PCB 上,传输线的阻抗往往会控制地很好,但大尺寸焊盘和信号过孔常常被忽略,这两者是易造成阻抗不连续的区域。比如:50 欧微带线上有大尺寸焊盘时,大尺寸焊盘相当于分布电容,破坏了微带线的固有的阻抗连续性。根据传输线理论,这时可加大微带线的介质厚度,使得微带线的线宽和大尺寸焊盘宽度尽量接近,该方法会造成微带线宽度较宽,在高密度板卡的设计中实现难度很大;另一种方法是微带线介质厚度、线宽不变,将大尺寸焊盘下方的地平面挖空,同样可以减小焊盘的分布电容,只不过,焊盘挖空的大小需要通过仿真来确定。这种方法,常常用在高速信号的耦合电容或芯片焊盘处。

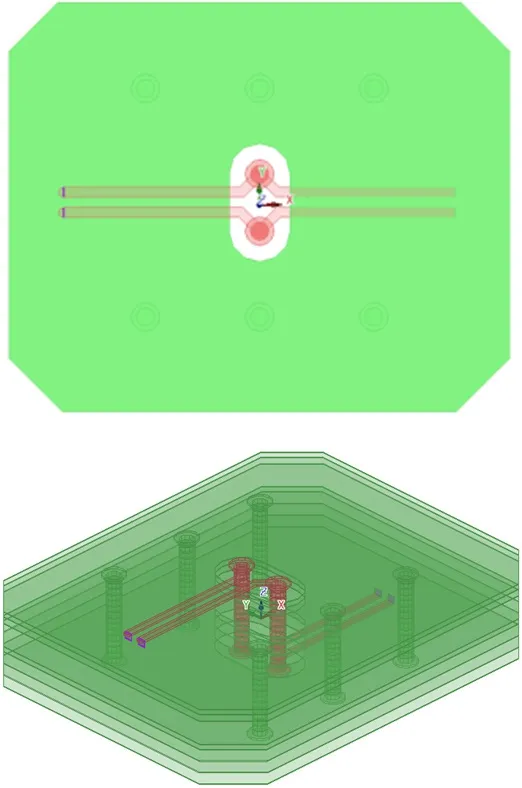

分别建立3 种不同挖空形式的仿真模型:

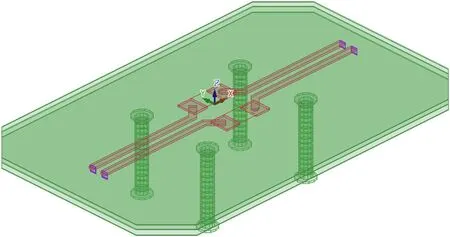

Case1(红色曲线):电容焊盘下方无挖空,参考第2 层地平面,如图2 所示。

图2

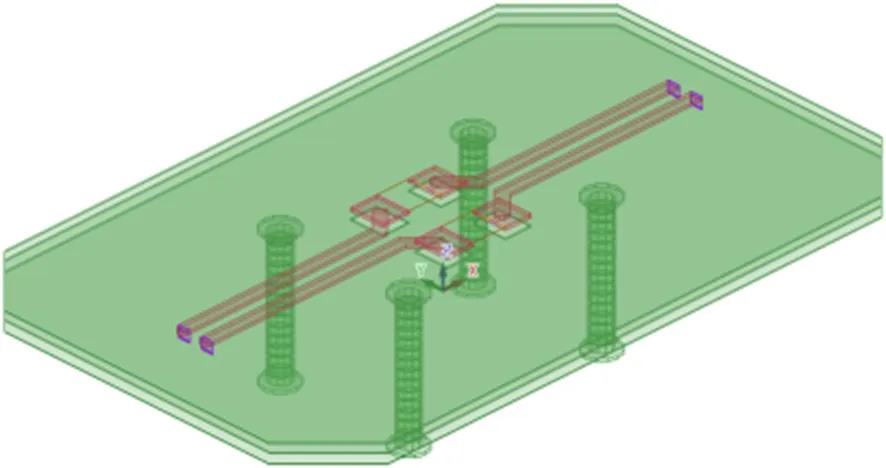

Case2(蓝色曲线):电容焊盘下方挖空第2 层,参考第3 层地平面,挖空尺寸和焊盘等大(长19.69mil 宽15.75mil),如图3所示。

图3

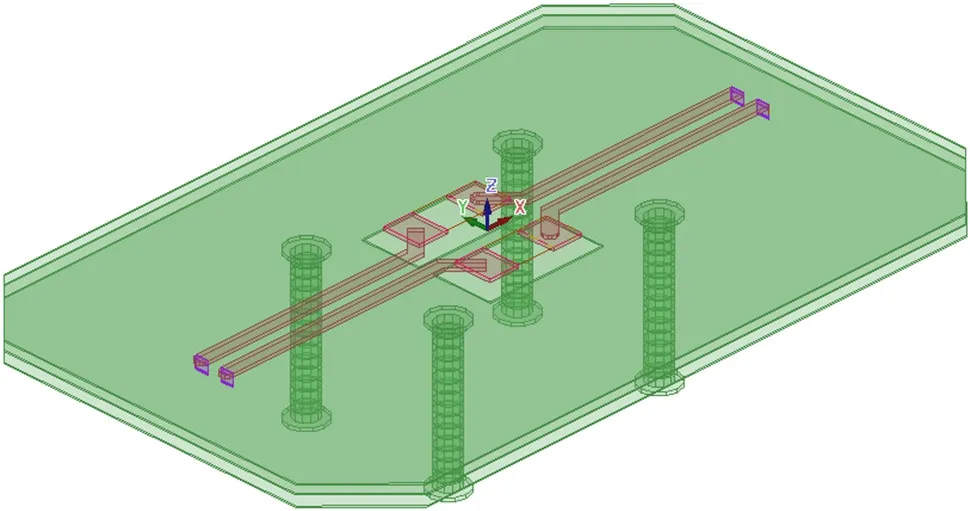

Case3(绿色曲线):电容焊盘下方挖空第2 层,参考第3 层地平面,挖空尺寸和电容本体等大(长41.34mil 宽21.66mil),如图4 所示。

图4

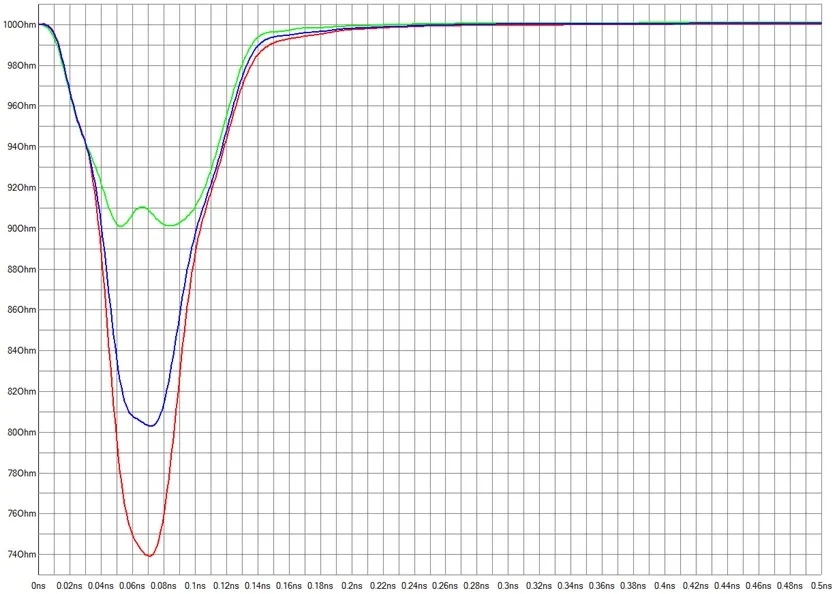

SDD11 和SDD21(如图5 所示)。TDR:上升时间40ps,如图6 所示。

图5

图6

通过SDD11(差模回波损耗)和SDD21(差模插入损耗)可以看出,在本案例的叠层结构下,Case3 的无源传输性能最优;从TDR 也可以看出,Case3 在电容焊盘处的阻抗明显优于Case1 和Case2。

4.2 过孔

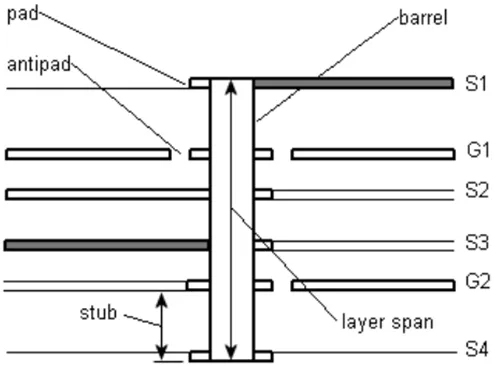

信号过孔由焊盘(pad)、反焊盘(antipad)、贯穿孔(barrel)、过孔残桩(stub)组成。焊盘是传输线与过孔连接的金属化圆环;反焊盘是过孔与铜箔、信号线之间避让间隙;贯穿孔是PCB 上贯穿TOP 和BOTTOM 层的一个金属圆柱体结构;过孔残桩是过孔未使用到的部分。如图7 所示。

过孔的等效模型可以由RLC 构成,经过简化的等效电路模型如图8 所示。

图7:过孔结构示意图

图8:简化的过孔等效电路示意图

从等效模型中可以看到:焊盘等效为电容;反焊盘等效为电容;贯穿孔等效为电感;过孔残桩等效为电感和电容的集合。

过孔寄生电容可以导致信号上升时间变长,传输速度减慢,从而恶化信号质量。同样,过孔寄生电感会削弱去耦电容的作用,从而减弱整个电源系统的滤波效果。此外,过孔阻抗不连续会影响其传输性能,引起高速信号、射频信号反射,造成信号完整性问题。

减小过孔阻抗不连续的常用方法有:去除非功能焊盘、选择合适的出线方式、优化反焊盘尺寸、减小过孔stub 长度等。其中,优化反焊盘尺寸和减小过孔stub 长度是设计中最常用的方法。

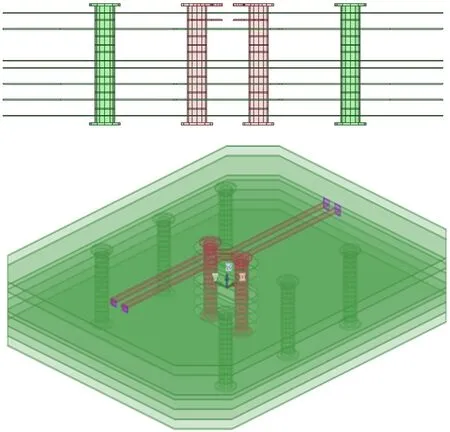

分别建立3 种不同大小反焊盘仿真模型:

过孔直径:10mil

过孔焊盘直径:20mil

孔中心间距:39.37mil

反焊盘挖空为in-line 模式。

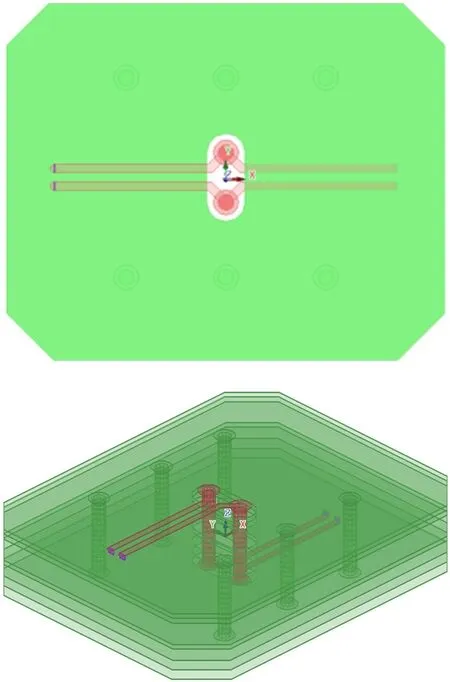

Case1(红色曲线):反焊盘直径30mil,如图9 所示。

图9

Case2(蓝色曲线):反焊盘直径36mil,如图10 所示。

图10

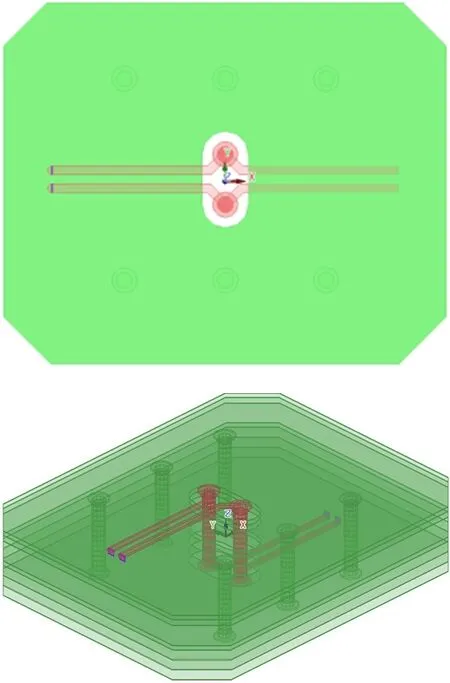

Case3(绿色曲线):反焊盘直径42mil,如图11 所示。

图11

SDD11 和SDD21(如图12)。

图12

TDR:信号上升时间40ps,如图13 所示。

图13

通过SDD11(差模回波损耗)和SDD21(差模插入损耗)可以看出,在本案例的叠层结构下,Case2 和Case3 的无源传输性能要优于Case1;从TDR 也可以看出,Case3 在过孔处的阻抗明显优于Case1 和Case2。

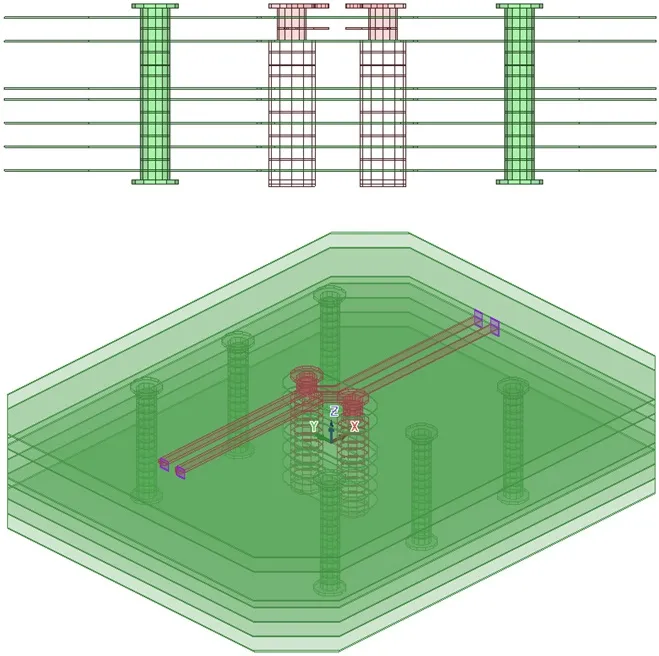

分别建立两种stub 长度的仿真模型:

过孔直径:10mil

过孔焊盘直径:20mil

孔中心间距:39.37mil

反焊盘挖空为in-line 模式。Case1(红色曲线):stub 长度67.256mil,如图14 所示。

图14

Case2(蓝色曲线):通过背钻工艺,将stub 长度减小至4mil,如图15 所示。

图15

SDD11 和SDD21(图16)。

图16

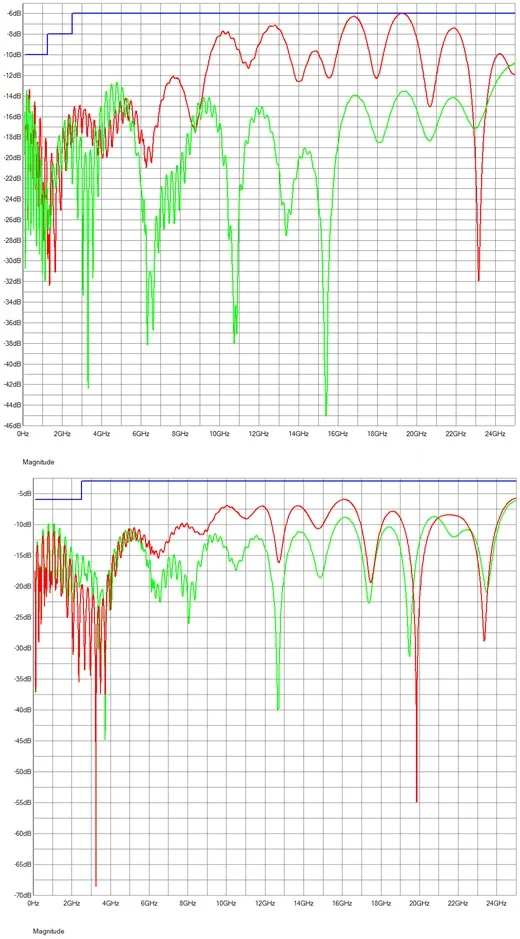

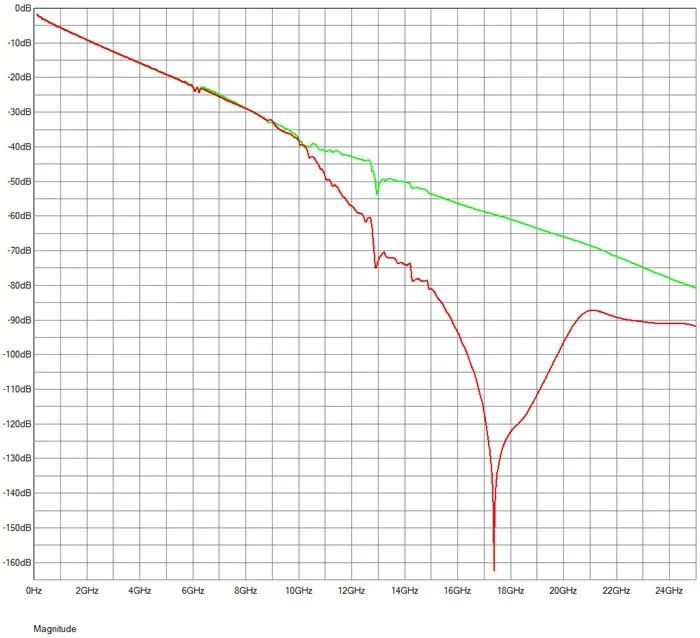

可以看到,在stub 长度有67.256mil 的Case1 中,在17.7GHz频率下,SDD21 达到了-29.2dB,SDD11 达到了-0.88dB,说明在该频率下,大部分能量被反射回源端,通过背钻去除过孔stub 后,SDD21 仅为-0.79dB,SDD11 仅为-12.69dB,改善效果显著。

4.3 整个通道

在完成对通道中各个要素仿真优化之后,还需要将各要素进行级连,构建完整的信号通道,得到整个通道的S 参数,以判定是否符合PCIE 协议的无源指标。以下是通过本文方法优化前后的无源参数对比,可以看到,通过优化耦合电容和过孔,回波损耗在高频段大幅改善,消除了插入损耗10GHz 至17GHz 范围内因谐振引起的损耗急剧增大,使得插入损耗(SDD21)曲线更加平滑,大大提高了通道的高频性能。

优化前:红色曲线

优化后:绿色曲线

SDD11 和SCC11(图17)。

图17

SDD21(图18)。

5 时域眼图仿真设计

对整个链路的无源性能进行判定通过后,就可以加载发送、接收端芯片的IBIS-AMI 模型来进行时域眼图分析了,在此过程中,还可以对芯片FFE、DFE、CTLE 等参数进行扫描,来找到适合当前通道的最优参数配置,进一步提升眼图质量,增加设计裕量,保证系统工作的可靠性。

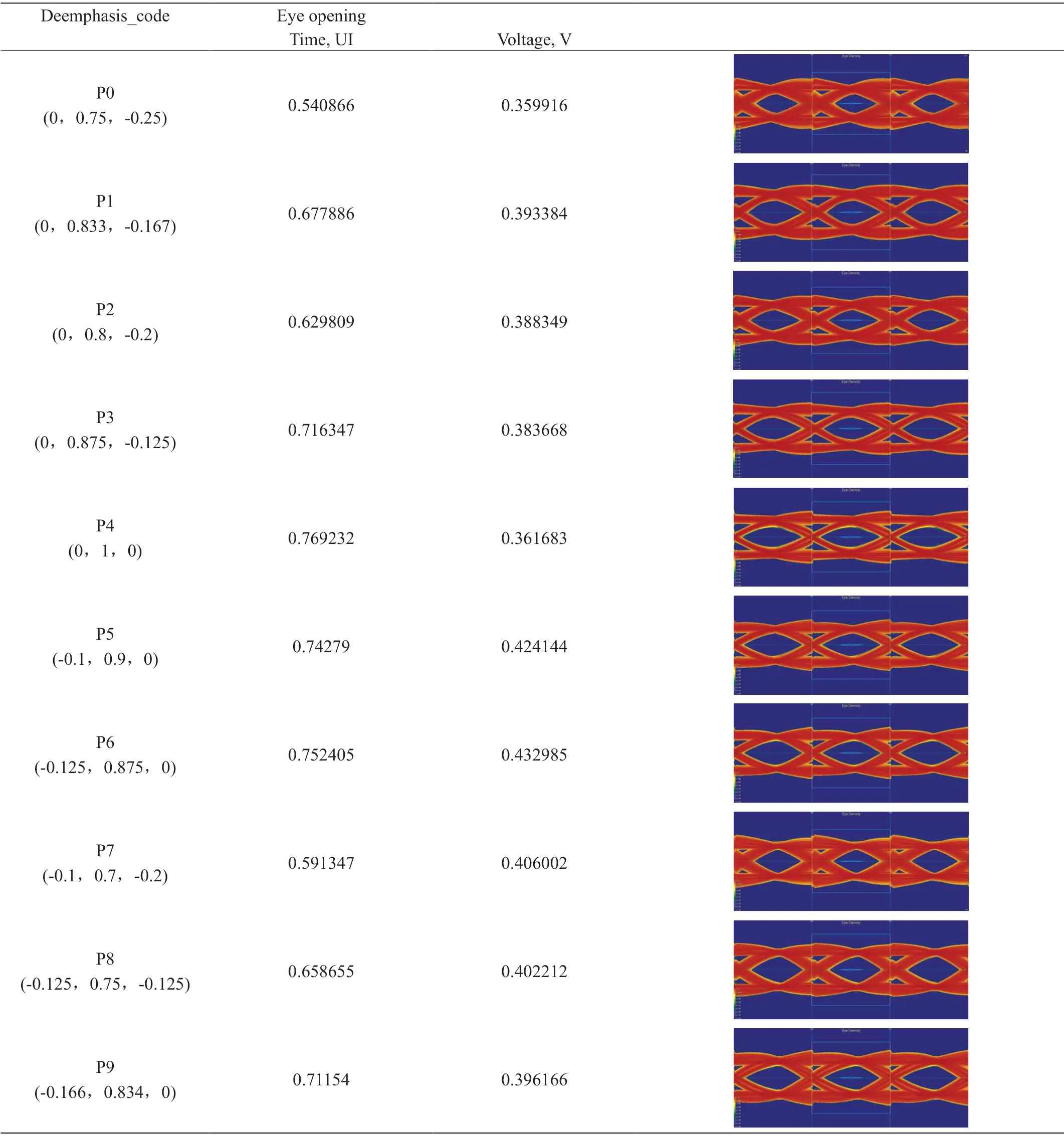

对4.3 章节中优化过后的通道进行眼图仿真,RX 端DFE 采用自适应模式,TX 端Deemphasis 的不同Tap 值对应如表2 所示。

表2

可以看到:当Deemphasis 设置为P6:-0.125,0.875,0 时,接收端眼图最优,眼宽和眼高分别为 0.752405UI,0.432985V。

6 结语

本文通过对某国产处理器PCIE 接口的信号完整性仿真,阐述了基于Hyperlynx 仿真软件的仿真流程和思路,PCB 无源通道的设计优化着眼点,以及IBIS-AMI 模型在高速Serdes 仿真中的应用。通过此方法可显著改善PCIE 信号质量,提高设计可靠性。

图18