基于ARM的双路差分同步采样电路设计与实现

2021-03-30马月红

徐 晴, 马月红

(石家庄铁道大学 电气与电子工程学院,河北 石家庄 050043)

0 引言

数据采集系统是电子工程中非常重要的部分,它与传感器技术、信号处理技术、计算机测量技术共同构成了现代化检测技术的基础[1-2]。高精度采样系统主要应用于通信、仪器控制、医疗设备等领域,随着科技的不断进步,数字系统对数据采样技术的要求不止是简单的数据采样,而是看重其采样速度、采样模式、采样精度、有效位数(ENOB)等参数。

在雷达系统中,传统的数据采集系统是由片外AD采样芯片组成的,目前FMCW雷达系统差频回波信号大都是差分信号,使用片外AD对差分信号进行差分采集不仅增加了电路的大小,而且成本增高,控制难度增大。由FMCW雷达测距原理可知,系统通过对差频信号进行FFT变换,计算出差频信号的频率,进而求出目标距离。如果IQ差分信号采样不同步,会使测得的频率出现问题,进而影响雷达系统测距精度,ADC的采样精度也会影响系统后续的距离定标精度。因此设计了一种基于ARM的双路差分同步采样电路系统,通过STM32F3系列单片机内部ADC实现对差频信号高精度同步差分采样,ADC采样率高达 5 MHz,可同时对多路信号实现高精度、高采样率、高速采样,采集的数据通过DMA传输,可以将采集的数据进行存储,通过RS232串口总线传输到PC上位机进行信号处理、画图、显示[3-7]。

1 差分同步采样系统整体设计

双路差分同步采样电路系统设计框图如图1所示,该系统由电源模块、差分信号模块、ARM电路、flash存储模块、串口通信电路、PC上位机组成[8]。其中ARM电路为系统的主控,实现对差分信号的差分ADC采集,并将采集的差分信号通过DMA通道传输。电源模块直接采用5 V输入,通过LFM3117-3.3芯片转换为3.3 V供电电压,这里不再赘述。

图1 总体设计框图

双路差分同步采样电路系统工作流程如下:首先差分信号模块产生2对差分信号分别为I+、I-和Q+、Q-,ARM内部ADC配置成双路差分同步采样模式,ADC差分采集差分信号将信号数组存放到CR寄存器中,然后通过DMA通道传输,系统在DMA中断服务函数中对采集的差分信号进行信号处理,系统可以进行信号存储,将采集的信号存放到SD存储卡,便于记录信号供后期测试,还可以通过RS232串口发送给上位机实现通信,并将信号波形信息显示出来。

2 差分同步采样电路硬件设计

2.1 ARM芯片选择

在FMCW雷达系统中,雷达中频信号一般是IQ双路,并且是差分信号。为了减小系统成本以及电路规模,本设计选用带有内部差分ADC的ARM芯片来代替片外ADC,为了实现对高频信号精确采样,要求ADC的采样率达到5 MHz。含有ADC的STM32系列非常多,但是并不是每一款芯片都可以达到5 MHz采样率。此时需要关注2个指标,一个是ADC支持的最高采样率,另一个是它的模拟带宽。STM32系统时钟大都在48 MHz和72 MHz,通过设置时钟分频后要保证ADC采样率至少为5 MHz,模拟带宽保证ADC模拟部分通带至少达到2.5 MHz。

市场上做开发板最多的是STM32F103、STM32F407、STM32F429系列,并且配套资源齐全,F4系列的ADC采样率可以达到2.5 MHz,但是其ADC没有差分模式。STM32F3xx具有5 MHz采样率的ADC,并且满足差分采样功能,本设计最终选择STM32F303微控制器。该ARM以Cortex-M4为内核,具有高速、低功耗、实时性等特点,内置12位高速AD转换器、定时器模块、内部存储模块、DAC模块等外设,根据数据采集的需求不同,可以实现多种模式ADC数据采集。

2.2 芯片管脚分配

STM32F303vct这款主控芯片有100个管脚,参考的资料为芯片参考手册及数据手册,通过ST意法半导体的原创工具STM32CubeMx软件来配置STM32F303双路ADC差分同步采样模式,选择ADC1的通道1和通道2,ADC2的通道3和通道4为差分通道,将ADC配置成双路规则同步模式,并打开DMA请求和ADC连续转换模式,ADC1、ADC2采集到的差分信号同时存放到一个32位的数组,其中ADC1采集的数据存放到数组低16位,ADC2采集的数组存放到高16位。串口选择usart1,通过串口转RS232将数组信号传送给PC上位机一边分析处理、显示。ARM芯片管脚分配关系如表1所示。

表1 STM32F303管脚分配

2.3 滤波放大电路设计

系统以雷达系统中频信号为信号源,为了使该系统采集到高质量的差频信号,系统需在ADC采样前对信号进行滤波放大处理,滤波放大电路设计包括两级放大电路和一级滤波电路。

系统为了满足微型化、低功耗等要求,如果对2对差频信号同时进行滤波放大处理,不仅增加电路规模、功率、成本,而且会引入误差,为此将每路差分信号转成单端信号来处理。第一级放大电路如图2所示,该电路主要作用是将差分信号转化成单端信号同时对信号进行放大处理。AD8426ACPZ是一种轨至轨输出仪表放大器,仅需要一个外部电路来调节功率,而且满足对差分信号放大转化成单端信号的功能。

图3为滤波电路,该电路由两级一阶有源低通滤波器组成,中频信号经过滤波电路后有效地滤除高频噪声,系统可以采集到高质量的中频信号。

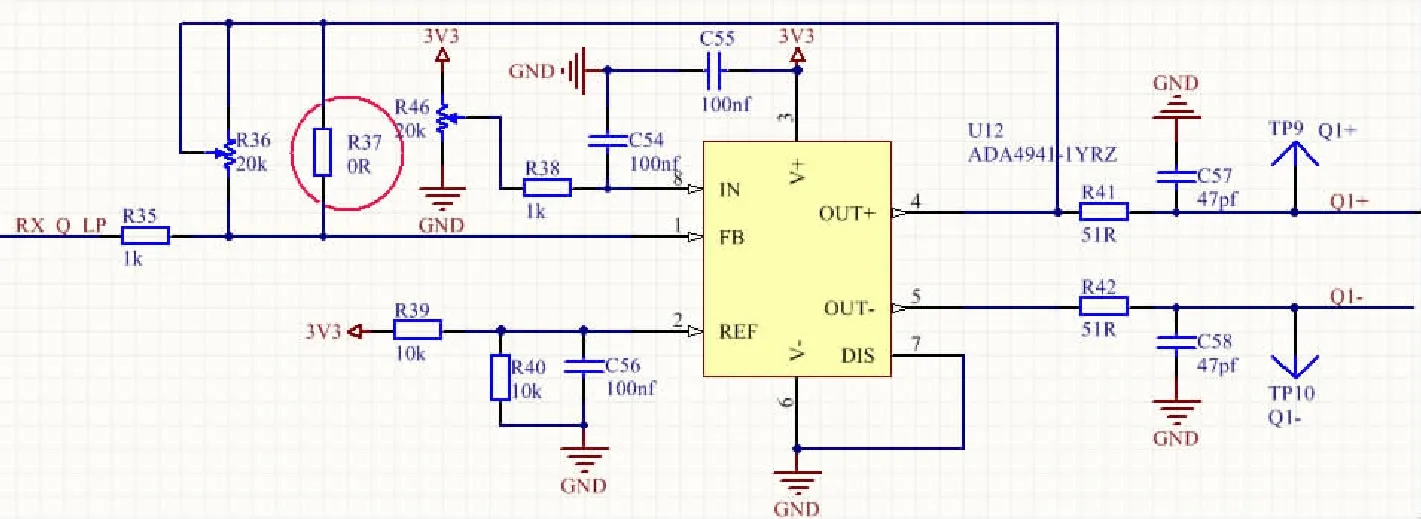

图4为第二级放大电路,该电路主要功能是单端信号转差分信号并对信号放大驱动ADC差分采样。ADA4941是一种低功耗、低噪声差分驱动器,其输出的差分信号具有低失真、高信噪比的特点,可驱动高精度差分ADC。

图2 第一级放大电路

图3 滤波电路

图4 第二级放大电路

2.4 SD卡存储模块

系统选择SD卡作为存储模块,具有较好的稳定性、通用性及容量高、读写速度快等特点。SD卡通过SDIO模式实现与STM32F303通信,将SD卡的DATA2、DATA3、CMD、CLK、DATA0、DATA1引脚与ARM微控制器相连。其中CLK为SD卡的时钟,由ARM产生的时钟信号引入。CMD是命令信号,传输所有的命令及响应。DATA0~DATA3为数据线,用来传输数据[9-10]。系统使用SD卡时首先对SD卡进行初始化。

3 差分同步采样电路系统软件设计

图5 ADC中断模式流程图

该系统的ARM软件设计主要包括:ADC采样中断模式设计、ADC采样DMA通道模式设计、ARM内部信号处理。系统初始化好各个模块后,差分信号源产生2对差分信号,每路信号经过滤波放大电路后由ARM内部ADC1、ADC2分别对I、Q两路实现差分同步采集,采集信号通过DMA传输,当传输的位数与设定的位数相等时会产生DMA中断,在DMA中断服务函数中可对采集的信号进行加窗、滤波处理,最后通过RS232串口将信号发送给上位机,根据设置的串口读取标志位来接收一个完整周期的信号,并可以在上位机实时显示差分同步采样电路采集到的信号波形。

3.1 ADC采样中断模式

STM32F303内部有4个12位ADC,ADC的电压输入范围为:UREF-≤UIN≤UREF+,其中,UREF-、UREF+分别为参考正负电压,由外部引脚决定。ADC采样中断模式流程如图5所示。

选择PA0、PA1作为ADC1的通道1、通道2,信号通过ADC1的通道进入规则通道,ADC设置为软件启动,此时模拟信号转化成数字信号存放到规则数据寄存器中,当存放的数组长度与设定的位数相同时会生成转换结束标志位,在中断服务函数中完成对信号的输出。

图6 DMA中断模式流程图

3.2 ADC采样DMA通道模式

直接存储区访问(DMA)为实现数据高速在外设寄存器与存储器之间或者存储器与存储器之间传输提供了高效的方法。由于DMA传输实现数据高速移动无需CPU操作控制,与ADC采样中断模式相比,ADC采样DMA通道模式大大提高了ADC的工作效率。图6是ADC采样DMA模式流程图,信号经过ADC管脚进入规则通道,配置ADC为差分同步模式,打开ADC的DMA通道并选择与ADC匹配的DMA通道,采集数组通过DMA通道传输存放到规则数据寄存器中,当采集的数据长度与设定的数值相等时会产生DMA中断标志位,在DMA中断服务函数中对数组输出。

3.3 ARM内部信号处理

很多情况下系统ADC采集到的差分信号并不能采集到整数个周期,系统采集到的信号如果从一个周期中切断,此时时间不连续的原始信号做FFT变换会出现信号剧烈变化,测量出的信号就不是很精准,因此FFT变换得到的信号频率不是原始信号的频率,也就是所谓的频谱泄露问题。为了获取到精确的信号频率,需要对信号进行滤波加窗处理,在程序DMA中断服务函数中,对采集到的信号数组经带通滤波器滤除噪声信号,利用点乘运算对信号加hanning窗处理。

在实验过程中对程序每一步单步调试验证结果的正确性,遇到ROM内存不够问题,为了解决该问题对程序进行了优化,采用数组复用技术,最终实现了双路差分同步采样功能。

图7 系统电路

4 实验测试及分析

为了验证系统的正确性,对系统进行了测试,差分同步采样系统如图7所示。实验设置系统参数如下:ARM片外采用25 MHz晶体经分频倍频关系,将系统时钟设置为70 MHz,ADC时钟APB2也为70 MHz,ADC时钟分频系数为1,ADC采样时间设置为1.5个周期,根据芯片手册STM32F303计算ADC采样率公式

fs=SYSCLK/(12.5+SamplingTime)

(1)

式中,SYSCLK为系统时钟70 MHz;SamplingTime为采样时间,取值为1.5,代入式(1)可计算出ADC的采样率为5 MHz。

实验方法如下:以FMCW雷达中频信号为信号源,系统对中频波信号差分同步采样,在ARM内部对信号进行处理并通过串口输出结果,其结果与雷达系统测量出的结果进行对比。图8(a) 是差分同步电路采集的雷达中频信号IQ双路时域显示,此时雷达系统测量实际距离为69 cm,经反推计算出差频信号频率为7.34 kHz,将差分同步采样电路采集的中频信号进行FFT运算,计算出中频信号频率为7.35 kHz,与实际中频信号频率相差0.01 kHz。图8(b)是差分同步采样电路采集的中频信号频域图,信号峰值位置为7.35 kHz。

图8 系统采样中频信号时域及频域

通过雷达系统对不同目标进行探测,雷达测出的中频信号频率与本系统采集的中频信号频率多次对比结果如表2所示。从表2结果可以看出,该差分同步采样电路采集雷达系统的中频信号与雷达系统计算出的中频信号频率相差无几,满足高精度、大带宽、高采样率的差分同步采样要求。该设计可用于各种雷达系统领域,通用性强。

表2 测量结果对比 kHz

5 结论

采用ARM单片机为主控芯片,使用ARM内部ADC实现了双路差分同步采样电路系统。该系统采样率高达5 MHz,具有多种采样模式,可直接应用在FMCW雷达系统领域,具有高采样率、大带宽、采样精度高、体积小、通用性强等优点,有很强的实用性和推广价值。