占空比可调的方波数字信号源电路设计*

2021-03-18吕栋腾

吕栋腾

(陕西国防工业职业技术学院,陕西 西安 710300)

0 引言

在自动控制系统中,方波信号的应用非常广泛,通常可作为一种标准信号在电子电路、测试仪器中进行性能试验或者物理量检测[1]。方波由基频加奇次谐波组成,奇次谐波的丰富程度和谐波之间的相位关系会影响方波的产生。方波的占空比简单来讲是指电路被接通的时间占整个工作周期的百分比,它可以是0~100%之间的任意值。通过控制方波的占空比,配合高精度的传感器,可实现复杂控制系统的闭环控制。本次设计以MAX+PLUSII作为开发平台,采用VHDL语言编程,CPLD为主要载体来实现占空比可调的功能测试。

1 方波电路的设计方法

本次设计的电路系统是一个高电平和低电平分别可以调整的数字信号源电路,用于控制3 000 V高压电源对电容的充放电,输出频率为0.3 Hz~3 Hz,输出电平要和TTL电平兼容。方波电路常见的设计方法有模拟电路、单片机和专用逻辑电路ASIC三种方法。模拟电路的方法通过压控振荡电路得到不同频率的方波,但其抗干扰能力差,难以通过上位机控制。单片机可以得到稳定度高的脉冲,但如果脉冲周期不是时钟信号的整数倍时,需要重新编写程序。专用逻辑电路ASIC的方法是通过硬件电路设计,得到连续可调的不同频率的方波信号[2]。

通过比较我们发现,由于是数字集成电路,ASIC具有较高的稳定性,可根据具体的逻辑要求来设计,便于用微机控制,而且应用较为简便且现场可调。故本次设计的方波数字电路硬件方面使用Altera公司的CPLD器件,采用这种专用逻辑电路设计的方波发生器不仅可以缩小控制电路的规模,而且还可以提高系统的稳定性。软件应用环境为MAX+PLUSII,使用VHDL语言编程并写入CPLD,采用电路模块合成的概念,提高了程序调试和系统的仿真速度[3]。

2 方波电路的系统结构

系统的功能就是产生一组占空比可调的方波。由键盘输入信号,经过同步消抖电路消除抖动进入控制器,控制器的z端口输入六位二进制数,用来控制高电平的持续时间;f端口同样也输入六位二进制数,用来控制低电平的持续时间,由此生成占空比可调的方波。经消抖处理后的信号,再经过分位电路,将六位二进制数转换为十进制BCD码,通过7段译码电路,将每个端口的输入信号用十进制数显示在数码管上。方波电路结构如图1所示。对于Altera的CPLD进行编程使用ByteBlasterMV并口下载电缆,由并口下载电缆将计算机中的配置信息传送到PCB板FLEX器件中,实现对FLEX系列器件的配置重构,并且可以对MAX 7000等器件进行编程[4]。

图1 方波电路结构图

3 方波电路的仿真及调试

该方波数字电路选用的CPLD器件为Altera公司所生产的MAX 7000系列中的EPM7128SLC84-15芯片。在MAX+PLUSII软件开发环境下进行程序的编译、电路系统的综合布局和优化、功能和时序的仿真。系统软件设计采用自顶向下的模块化设计,各子模块都采用VHDL描述,这样便于在其他设计中把整个子系统作为一个模块来调用[5]。在具体设计过程中,对各子模块单独进行编程并仿真验证。

3.1 控制模块

控制模块是主模块,能够产生占空比可调的方波,通过6位二进制数来控制高、低电平的持续时间。此模块有一个基准时钟clk,两个输入端口z、f和一个输出端口q。z、f分别控制高电平、低电平的维持时间。PUL模块符号如图2所示,控制模块PUL的仿真波形如图3所示。

图2 PUL模块符号图 图3 控制模块PUL的仿真波形图

3.2 同步消抖电路

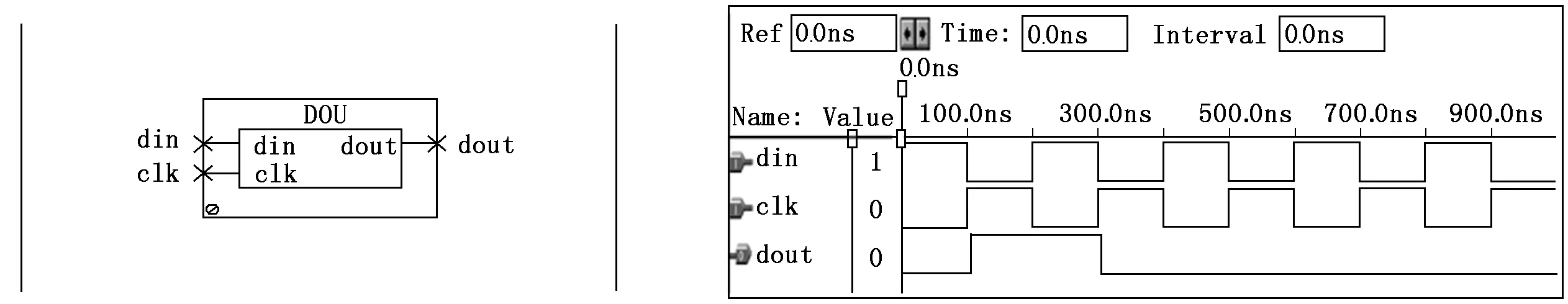

输入信号由按键电路产生,一般按键电路在使用过程中,因为按钮在闭合和断开的瞬间会产生微弱的电弧信号,系统会将此毛刺信号误判为另一次输入信号,而毛刺信号会影响系统的有效输出,所以在此次设计中我们增加了同步消抖电路,以消除毛刺信号的影响和电路系统的误操作。DOU模块符号如图4所示,仿真波形如图5所示。

图4 DOU模块符号图 图5 消抖模块DOU的仿真波形图

3.3 分位电路

在进行7段数码管译码前,需要将输入端口的数分解成单独的十进制数。FENWEI模块符号如图6所示,分位模块的仿真波形如图7所示。

图6 FENWEI模块符号图 图7 分位模块仿真波形图

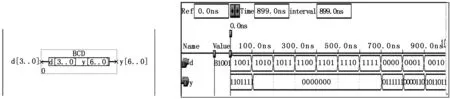

3.4 7段译码电路

该电路选用共阴极的7段数码管显示。共阴极数码管在使用过程中,公共引脚需要正确接地。只要给相应的引脚加上高电平,就可以点亮这段数码管进行显示。7段数码管中的7个发光二极管和一个小数点指示发光二极管对应10个引脚中的8个,剩下的2个引脚对应2个公共接地端K。模块BCD符号如图8所示,仿真波形如图9所示。

图8 BCD模块符号图 图9 译码模块仿真波形图

4 结束语

电路系统在调试仿真结束后,还可使用MAX+PLUSII的时间分析功能来分析设计编译后合成的性质。将电路设计文件转换成供下载用的输出文件,例如*.pof文件与*.sof文件。通过对各模块的延迟矩阵分析可达到最佳布局规划。相比由传统模拟电路RLC或者RC电路构成的方波发生器,这种利用CPLD的数字电路设计方法,控制精度高且修改灵活。需要注意的是在逻辑综合过程中,系统优化的许多约束条件是相互关联的,须反复设定约束条件,以减小芯片设计面积和功耗[6]。通过综合调试,该电路系统工作可靠、输出性能良好,对占空比可调的方波数字信号电路设计有一定的借鉴意义。