一种20~30 GHz高增益混频器设计

2021-03-17孟益超文进才孙玲玲

孟益超,文进才,孙玲玲

(杭州电子科技大学射频电路与系统教育部重点实验室,浙江 杭州 310018)

0 引 言

随着科技的发展,射频接收机成为研究热点。作为接收机前端核心电路的下变频混频器,其作用是通过下变频射频信号到中频信号,进一步可供后续电路使用。由于下变频混频器的转换增益高低对接收机中后续电路的性能影响较大,转换增益的提高一直是研究的热点与难点。20~30 GHz的工作带宽覆盖了完整28 GHz的5G毫米波频段,该频段的混频器是一大研究热点[1]。基于CMOS工艺的下变频混频器的研究主要包括有源混频器和无源混频器,其中无源混频器虽然转换损耗大,但结构简单,容易实现[2],一般可使用反向并联二极管对(Antiparallel Diode Pair,APDP)结构实现[3]。为降低本振信号的输入功率,无源混频器可以使用互补开关晶体管的方式设计[4]。有源混频器一般采用吉尔伯特单元设计,采用巴伦对输入信号进行差分输入,通过附加的线性化电路来提高电路线性度[5],并使用寄生电容消除、负电阻补偿技术、电流注入技术与源极退化技术提高转换增益[6-7],在电源处插入谐振电感的设计方式也可实现转换增益的提高[8]。本文采用增加缓冲放大级的方法,设计了一种20~30 GHz频段内的下变频混频器,为5G技术中混频器设计提供一定的借鉴。

图1 混频器符号

1 混频器的电路设计

混频器的主要功能是利用电子元器件的非线性特性,实现频率转换。混频器的符号如图1所示。图1中,混频器一般包含3个端口:射频(RF)端口、本振(LO)端口和中频(IF)端口,其中RF与LO为混频器输入端口,IF则为输出端口,fRF,fLO与fIF则分别表示3个端口对应的信号频率。混频器的功能是将2路信号混频,即将2路输入信号的频率fRF与fLO相乘,这也是实现频谱搬移的最基本手段。混频器分为下变频与上变频,当混频器被用作上混频时,fIF=fLO+fRF,被用作下混频时,fIF=|fLO-fRF|。

本文设计的20~30 GHz下变频混器以实现大于6 dB的高转换增益为目标,核心电路采用双平衡吉尔伯特结构。通过设计变压器巴伦来实现本振信号与射频信号的差分输入,电路输出端口的缓冲放大电路进一步提高了混频器的转换增益,电路输入端口匹配网络的设计提高了信号与电路的匹配度,减少了信号的回波损耗。

1.1 混频器原理图设计

本文设计的混频器原理图如2所示。通过变压器巴伦实现信号本振LO信号(20~30 GHz)和射频RF信号(20.1~30.1 GHz)的差分输入,同样以差分的形式将中频信号IF(100 MHz)输出。为了得到更优的电路性能,在巴伦之后增加了匹配网络设计。直流电源VG与VDD为晶体管分别提供栅极电压和漏压电压,并使其在偏置状态工作。电容C3,C4,C5与C6作为隔直电容添加在2种信号的输入端。采用电容C1与C2并联在直流电源处,防止交流信号对电源带来高频串扰和噪声。

图2 混频器的原理图

本文设计的电路结构基于吉尔伯特单元,图2中共有6个电阻,其中R1与R2用于隔离晶体管栅极的偏置网络和本振信号,R3与R4用于提供晶体管直流路径。晶体管M1~M4统一都为nMOS型,通过本振信号的控制,4个晶体管都工作在开关状态。其中晶体管M1与M4分为一组,其余晶体管M2与M3分为另外一组。一般采用余弦信号作为本振信号,当信号处于正半周期时,晶体管M1与M4为导通态,而晶体管M2与M3为截止态;当本振信号处为负半周期,M1与M4处于截止态,而M2与M3则为导通态。

图3 开关电路原理图

图3为图2混频器原理图中晶体管M1~M4组成的开关电路原理图,通过分析电路中的电压进一步解释其工作原理。当本振信号为正半周时,M1漏极输出为VLO+VRF+,M4漏极输出为VLO+VRF-;而当M2与M3处于工作状态时,M2漏极输出为VLO-VRF+,M3漏极输出为VLO-VRF-,得出整个信号周期内IF+端信号为VLO+VRF++VLO-VRF-,IF-端信号为VLO+VRF-+VLO-VRF+。由于信号以差分形式输入,则有VLO+=-VLO-,VRF+=-VRF-,得到IF+=2VLO+VRF+=-2VLO+VRF-=IF-。

考虑到采用普通吉尔伯特单元所能实现的增益不能满足要求,为了加强混频器电路的转换增益,基于吉尔伯特单元,在2个中频输出端口分别增加了电阻反馈跨导放大器,其中M5(nMOS型)和M7(pMOS型)组成中频信号IF+跨导放大器,而M6(nMOS型)和M8(pMOS型)组成中频信号IF-跨导放大器。这部分电路原理图如图2虚线框所示。R5与R6则为2路信号的放大器提供电阻反馈,并将输出的中频信号从电流输出转换成电压输出信号。缓冲放大级通过增强开关电路输出的中频信号,进一步提高混频器的转换增益。

1.2 巴伦设计

图4 巴伦结构图

变压器巴伦的设计如图4所示。巴伦由4层线圈组成,巴伦左端为单口输入,另一端口悬空,右端有2个输出端口,将输入信号差分为2路幅度相等、相位相反的信号。巴伦的中心抽头处通过电容C接地,通过该电容对巴伦2个输出端口相位等性能进行调优,最终确定值为870 fF。

采用ADS仿真软件对变压器巴伦性能进行仿真,结果如图5所示。图5(a)中,频段为20~30 GHz时,变压器巴伦输入端口回波损耗S11在-12 dB附近,其中2个输出端口的插损为-4±0.5 dB,插损十分平衡且平稳。在图5(b)中,当频段范围为20~30 GHz时,2个输出端口之间的相位差为180°±5°。

图5 仿真获得的变压器巴伦性能曲线

1.3 匹配网络设计

图6 本振端口的匹配网络

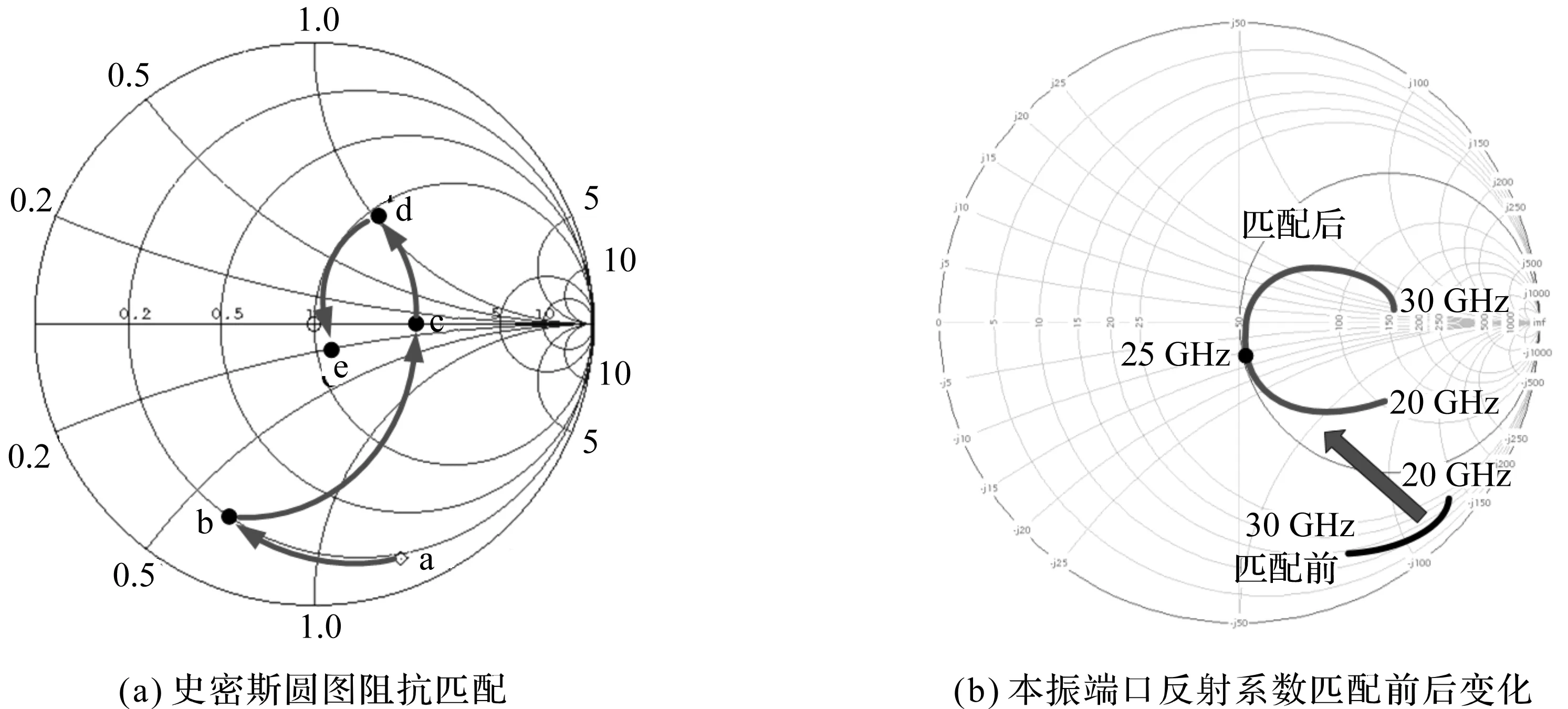

为了提高电路性能,在变压器巴伦与核心电路之间增加匹配网络的设计,匹配网络一般由电感、电容或电感与电容的组合来实现。对电路的本振输入端口进行阻抗匹配,本振端口的匹配网电路如图6所示。图6中,a点之后连接混频器电路,e点为本振输入。由仿真可知:本振输入端口频点为25 GHz处的输入阻抗是18.6-j×125.1 Ω,平分阻抗到2路信号,可知起始点a输入阻抗为9.3-j×71.4 Ω,其中阻抗单位为欧姆,j为虚部。匹配网络分为4块,由a点出发串联269 pH的1个电感L1达b点,再并联感值为203 pH的1个接地电感L2到c点。虚线框是变压器巴伦的等效电路,采用电容C与电感L3并联构成,c点经过接地电感L3到达d,最后经电容C到达e点。

本振端口在史密斯圆图上的阻抗匹配如图7(a)中所示,混频器本振端口反射系数匹配前后变化如图7(b)所示。由图7可知:匹配前,频段内的反射系数位于中心点的外,匹配后,反射系数曲线位于图7(b)中心附近,且中心频点与图(a)中e点位置相近。

图7 本振端口中心频点25 GHz的阻抗匹配

由于射频端口与本振端口的匹配网络结构相同,只需将图6中由a到b点的L1电感值变为129 pH,而b到c点的接地电感L2的电感值变为335 pH,得到射频端口在中心频点25 GHz的史密斯圆图阻抗匹配如图8所示,从图8(a)可以看出,最终得到的匹配点e十分接近史密斯圆图中心;从图8(b)可以看出,匹配前后端口反射系数变化较大,且中心频点25 GHz接近中心处,匹配结果良好。

图8 射频端口中心频点25 GHz的阻抗匹配

2 混频器版图与仿真

将变压器巴伦与核心电路组合后,基于0.18 μm的 CMOS工艺,在20~30 GHz的变频混频器设计版图如图9所示。版图总共包括6个信号PAD,分别为本振输入PAD,射频输入PAD,2个直流电源PAD和2个中频输出PAD。版图的面积是1.41 mm×0.88 mm。

图9 20~30 GHz下变频混频器版图

所设计的芯片仍在流片,因此本文仅对混频器的性能仿真,如图10所示。从图10(a)看出,混频器在20~30 GHz的全频段达到优于7.8 dB的增益,最优达到9.8 dB。从图10(b)看出,中频输出0.1~1.0 GHz时,其带来的噪声系数范围是15.5~16.0 dB;图10(c)是3个端口的隔离度,LO-RF之间的隔离度为-36~-29 dB之间,LO-IF的隔离在-27 dB以下,RF-IF的隔离度是-42~-34 dB之间。从图10(d)看出,本文设计所达到的1dB压缩点,在中心频点25 GHz处为-13.6 dBm。

图10 20~30 GHz频率范围混频器的仿真结果

本文设计与其他设计结构的下变频混频器性能参数对比情况如表1所示。

表1 不同结构的下变频混频器性能对比

由表1可知,无源结构混频器结构简单,但转换增益较低;有源结构混频器的转换增益得到提高,导致直流功耗增大。本设计在20~30 GHz频率范围内和较低的本振功率下,实现了良好的转换增益,改良的吉尔伯特结构使得电路拥有良好的端口隔离度。但是,本设计中,由于缓冲放大级电路的存在导致晶体管数量增加,造成直流功耗的增大。而且,由于本振信号与射频信号需要采用变压器巴伦差分输入,因此使设计版图增大,并进一步使混频器的整体电路增加了面积,相比其他设计,本设计还需要进一步改进。

3 结束语

本文基于0.18 μm CMOS工艺设计了一款使用吉尔伯特单元的20~30 GHz下变频混频器。对比普通吉尔伯特结构的下变频混频器,本文设计的缓冲放大级电路对中频输出信号进行放大,提高了混频器的转换增益,实现了预定大于6 dB的高转换增益目标。但是,电路复杂度的增加和额外元件的引入使得电路的功耗上升,如何同时实现高转换增益与低功耗仍是设计难点。