脉冲激光诱发65 nm体硅CMOS加固触发器链的单粒子翻转敏感度研究

2021-03-15韩建伟马英起上官士鹏梁亚楠

李 赛,陈 睿,韩建伟,马英起,上官士鹏,李 悦,朱 翔,梁亚楠,王 璇,2

(1.中国科学院国家空间科学中心,北京100190;2.中国科学院大学,北京100049;3.航天工程大学 激光推进及其应用国家重点实验室,北京101416)

0 引言

空间辐射环境中各种粒子,如电子、质子、α 粒子、重离子等的入射会造成材料和元器件的损伤,其中粒子与微电子器件中的半导体材料发生相互作用,可能造成航天器上电子设备出现复位、关机、“大电流”等故障。基本空间辐射效应包括总剂量效应、位移损伤效应及单粒子效应等。统计表明,在轨航天器因辐射环境引起的故障中由单粒子效应造成的异常占较大比例。随着器件工艺尺寸的日益缩小,元器件受单粒子效应的影响日趋显著。单粒子翻转效应(single event upset,SEU)是指半导体器件的敏感区(通常是反向偏置的P-N结)在单个高能粒子的轰击下发生电荷收集并造成逻辑状态改变的现象,是最常见的单粒子效应之一。

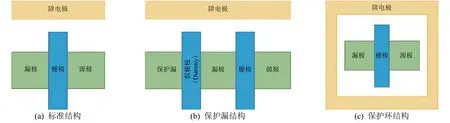

随着器件工艺尺寸的不断缩小,产生单粒子翻转所需的临界电荷越来越少,且电荷共享也更易发生,使得SEU 效应越来越严重。小尺寸工艺下单一重离子轰击产生的轨迹能够同时导致多个敏感节点同时收集电荷,被称为电荷共享效应。针对重离子轨迹上的电荷横向扩散到多个P-N结的相关研究表明,在4μm 距离上扩散的电荷量可达直接入射电荷量的15%。也有研究表明,在90 nm 工艺节点重离子入射最多影响2个单元,而在65 nm工艺节点重离子入射将影响3个单元(LET 值不大于40 MeV·cm/mg 的辐射条件下)。徐慧利用DICE 结构设计的65 nm 工艺触发器研究了其在LET 值为13 MeV·cm/mg 时发生电荷共享的敏感间距约为1.6μm。增加敏感节点间距和采用保护环、保护漏结构等是常见的版图加固设计:增大敏感节点间距可有效减小电荷共享效应的发生;保护环结构可通过增加阱接触的方式对器件有源区进行隔离,从而有效减小阱电势的扰动,显著提高PMOS晶体管的抗辐射能力;保护漏结构可通过在敏感器件的漏极附近增加电极的方式来泄放电荷,有助于NMOS晶体管抗辐射性能的提升。

抗单粒子效应加固试验评估常用的地面模拟源主要包括粒子加速器提供的重离子、质子、中子,放射源以及脉冲激光等。其中,脉冲激光模拟手段因其能量连续可调、操作方便安全在世界范围内得到认可和推广。重离子主要通过与靶原子核外电子发生非弹性碰撞产生电子-空穴对,激光主要通过光致电离产生电子-空穴对,虽然脉冲激光和重离子与半导体材料相互作用过程以及沉积能量(电荷)的方式不同,但两者都在半导体中产生了电荷,形成了电离径迹,而且径迹中电荷与半导体器件P-N结的相互作用过程也是相似的,同时电荷在重新分布的过程中所遵循的漂移、扩散、复合的物理规律是一样的,经过快速演化后的电荷密度分布十分相似,因此器件内部灵敏结吸收电荷后两者在半导体器件输出端能够产生相近的单粒子效应规律。

本文以典型的时序逻辑单元触发器(flip-flop,FF)模块作为研究对象,利用脉冲激光研究不同版图加固设计和不同测试模式下其单粒子翻转敏感度,并粗略给出电路发生翻转时的激光能量对应的重离子LET值,研究结果可为相同工艺尺寸器件的抗辐射加固设计提供参考。

1 试验样品及试验设置

1.1 试验样品

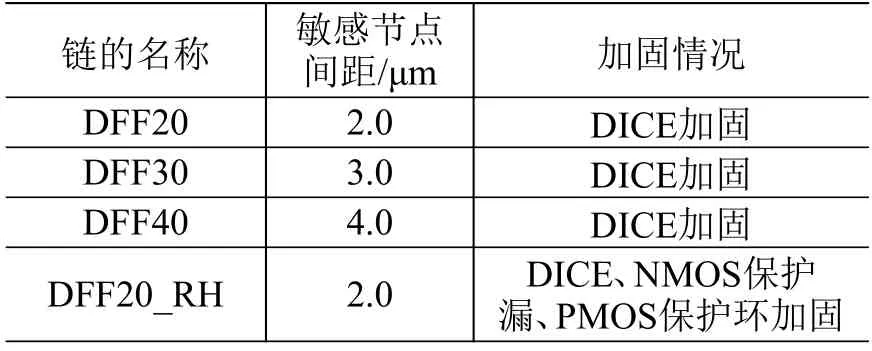

试验样品为定制65 nm 体硅CMOS工艺D型触发器链,芯片中设计了4条不同敏感节点间距和采用保护环、保护漏加固的触发器链,每级DFF模块的电路采用双互锁存(DICE)加固设计,详细信息如表1所示。芯片的I/O电压为5 V,工作电压为1.2 V。因脉冲激光不能穿透芯片正面的金属层,故对芯片进行了背部开封装处理,从背部硅衬底层进行辐照。

表1 试验样品详细信息Table1 Detailsof the DFFchains

1.2 脉冲激光试验装置和等效LET 值计算

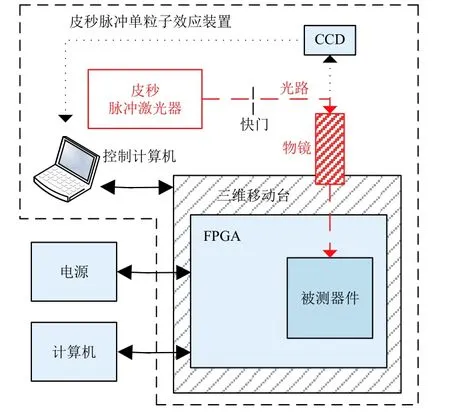

试验在中国科学院国家空间科学中心的脉冲激光单粒子效应试验装置上进行,采用Nd:YAG 型激光器,激光波长为1064 nm,脉宽为25 ps,光斑直径约2μm,脉冲激光的重复频率为1~50 kHz,等效LET 值范围为0.1~120 MeV·cm/mg。图1所示为试验装置原理。试验样品背面朝上固定在三维移动台上,脉冲激光从正上方入射到样品背部,通过移动三维移动台实现芯片的扫描测试,并由CCD实时监测激光入射到芯片表面的情况。

图1 试验装置原理Fig.1 Schematic diagram of the test system

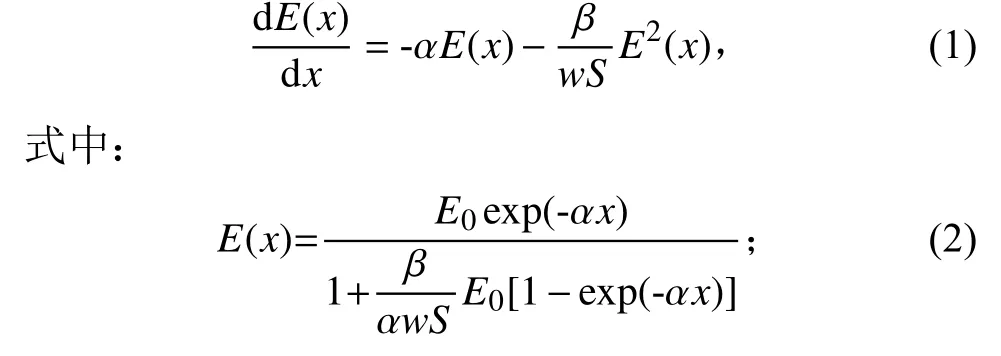

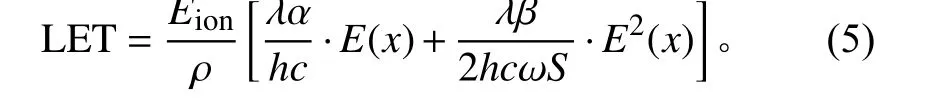

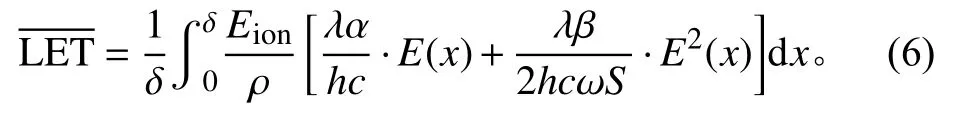

可通过脉冲激光与高能离子产生的电荷量相等来进行等效LET值计算。在激光强度较高或者半导体器件掺杂浓度比较高时,将会导致比较严重的非线性吸收现象。双光子吸收严重时脉冲激光在单位长度上的沉积能量为

α为激光在半导体中的吸收系数,cm;β 为双光子吸收系数,对于硅器件,β=30 cm/GW;w 为脉冲宽度,s;S 为光斑面积,m;E为激光能量,J。

脉冲激光在单位距离上产生的电荷数为

式中:E为离子在硅材料中激发1对电子-空穴对所需的能量,E=3.6 eV;ρ为半导体材料密度,ρ=2.33 g/cm。

令N=N,得到

当双光子吸收较强时,激光的穿透深度δ 显著减小,因此在δ 深度上对LET 取平均值得到

波长为1064 nm 的Nd:YAG 激光在硅中的穿透深度δ=1/α≈1000μm,虽然双光子效应显著时穿透深度会减小,但对于硅器件的灵敏层深度而言也是足够深的。激光入射到器件表面时会发生反射,反射率与器件表面材料、厚度有关,实验难以获得,往往忽略此项,因此计算出的等效LET值会偏高。此外,脉冲激光产生的离子径迹较宽,故体电荷密度较低,根据单粒子效应的发生机理,只有当径迹体电荷密度高于器件的掺杂浓度时才会发生,因此对于一些掺杂浓度较高的器件,脉冲激光测得的翻转阈值通常会高于加速器测量结果。

1.3 试验方法及内容

试验时,将移动台扫描间隔设为5μm,扫描速度设为5000μm/s,激光器工作频率设为1 kHz,得到的激光注量为4×10个脉冲激光/cm。试验开始前,使脉冲激光聚焦到芯片硅衬底表面,然后上移移动台找到金属布线反射的二次光斑,并通过上移距离计算得到芯片的硅衬底和有源区总厚度约为450μm,即硅衬底表面到有源区上表面的距离为450μm。试验时,使激光聚焦到芯片的有源区,对芯片进行全扫描,通过测试板实时检测器件发生SEU 的情况并记录数据。图2所示为试验现场,试验测试了不同激光能量辐照下,触发器链在锁存数据“0”和锁存数据“1”测试模式下的SEU 情况。DFF链的SEU 敏感度用平均每级触发器的SEU 截面σ 表示,

图2 试验现场Fig.2 Photograph of the test field

式中:n为DFF链发生SEU 个数,F 为单位面积(cm)内的脉冲激光注入个数;N 为DFF链中DFF的级数。

2 试验结果和讨论

2.1 不同敏感节点间距的DFF链的SEU敏感度

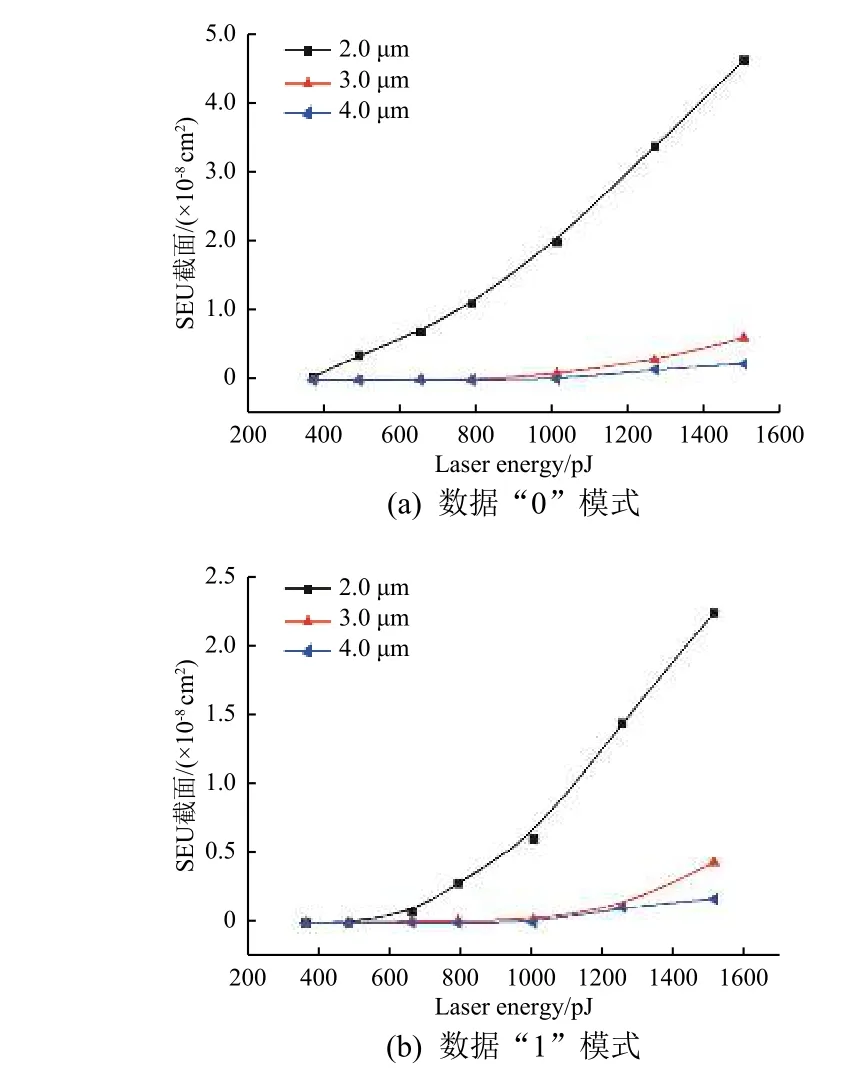

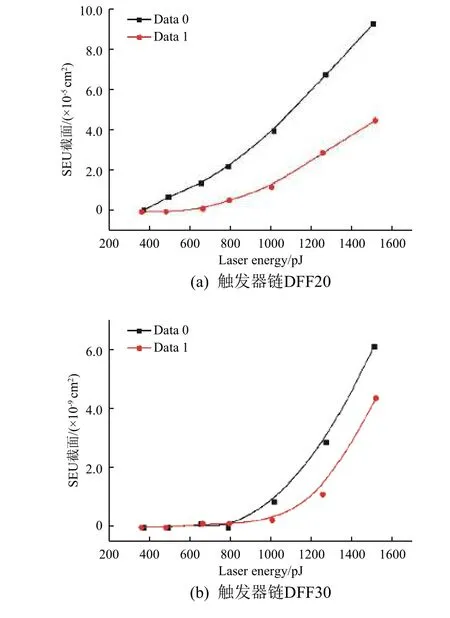

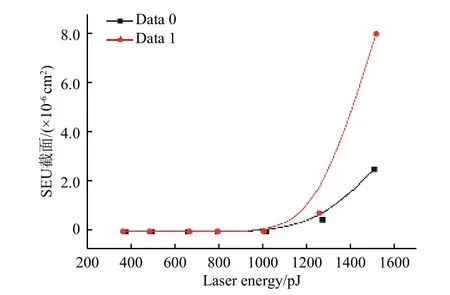

图3所示为具有不同敏感节点间距的触发器链在不同激光能量辐照下的SEU 截面,其中(a)为数据“0”测试模式下的结果,(b)为数据“1”测试模式下的结果。

图3 不同敏感节点间距触发器链的SEU 截面Fig.3 SEU cross-section of DFF chain with different sensitive nodes spacing

从图3(a)可以看出,在数据“0”测试模式下,触发器链DFF20、DFF30、DFF40分别在激光能量为490、650、1010 pJ(利用式(6)计算得到等效LET 值分别为20.2、26.8、41.6 MeV·cm/mg)时发生了SEU;从图3(b)可以看出,在数据“1”测试模式下,触发器链DFF20、DFF30、DFF40分别在激光能量为660、660、1250 pJ(等效LET值 分别为27.2、27.2、51.5 MeV·cm/mg)时发生了SEU。因此可以认为,无论是在数据“0”还是数据“1”测试模式下,敏感节点间距最小的电路单元最容易发生SEU,且随着敏感节点间距的不断增大,电路的SEU 敏感度下降。值得注意的是,当敏感节点间距从2.0μm增大至3.0μm 时,随着激光能量的增加,电路的SEU 截面显著减小,但当敏感节点间距进一步增大时,SEU 截面的减小程度不甚明显。如,数据“0”测试模式下,激光能量为1500 pJ时,敏感节点间距为3.0μm 的触发器链的SEU 截面比敏感节点间距为2.0μm 的触发器链的SEU 截面减小约6.6倍,而敏感节点间距为4.0μm 的触发器链的SEU 截面比敏感节点间距为3.0μm 的触发器链的SEU 截面减小约1.6倍。

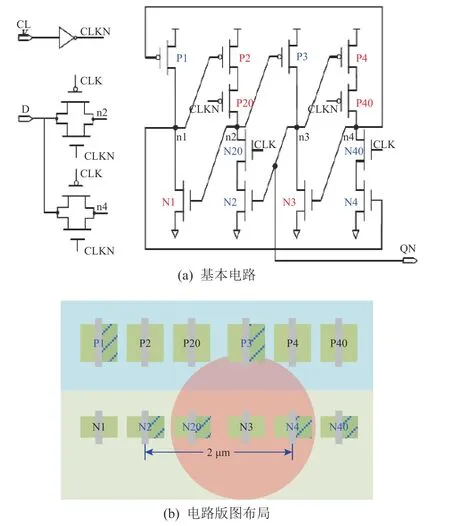

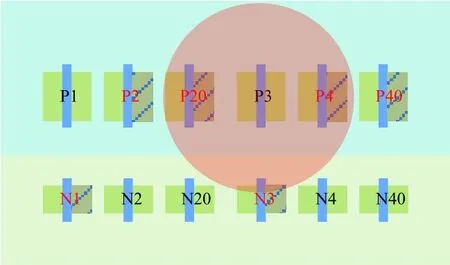

图4为DICE 锁存器基本电路和敏感节点间距为2.0μm 时对应的版图布局。

图4 DICE 锁存器基本电路和对应版图布局Fig.4 Circuit schematic of DICE-structure DFFand layout

DICE 电路由4组相互耦合的反相器组成,两两晶体管构成敏感节点对。当第一级反相器中n1节点发生翻转时,会影响P2栅极电压,但是此时第三级反相器的节点n3并未受到辐照和发生改变,因此n2节点仍保持原来状态,第二级反相器所存储的数据不会发生翻转。同理,第四级反相器存储的数据也不会发生改变。因此,仅一级反相器发生翻转时,翻转后的数据由于无法锁存将在一段时间后恢复到原来的状态,不会造成电路发生SEU。然而在小尺寸工艺下,由于敏感节点对间距的减小,电荷共享极易发生。当锁存数据为“0”,即节点n1=n3=0,n2=n4=1时,晶体管P1、P3、N2、N20、N4、N40(图4(b)中名称标蓝的晶体管)处于反向偏置状态,因此其漏端(图4(b)中阴影标注)是电荷收集的敏感区域。图4(b)中给出了激光光斑所能覆盖区域的情况。虽然激光与材料作用电离出电荷的机制与重离子不同,但在电荷收集和能量传输阶段,两者的物理过程和机制是类似的。激光光斑从硅衬底入射到器件有源区内部并在辐照区域与材料发生光电效应产生电荷云,而DICE 结构中敏感晶体管对N2/N20和N4有可能同时处于被激光诱发的电荷云中并收集电荷;当所收集电荷多于节点翻转所需的临界电荷时,电路存储的数据将发生翻转。

在电荷径迹一定的情况下,敏感节点间距越小,DICE 电路版图中的敏感晶体管对越容易发生电荷共享,从而诱发SEU,因此敏感节点间距为2.0μm 的触发器链表现出较高的SEU 敏感度。当敏感节点间距大于电荷共享效应可以发生的最大间距时,电路的SEU 敏感度会大幅度下降;因此,相比于敏感节点间距为2.0μm 的触发器链,敏感节点间距为3.0μm 的触发器链的SEU 敏感度明显降低。随着激光能量的增加,电离出的电荷密度增加,作用区域增大,因此电荷共享效应更容易发生进而导致SEU,试验触发器链发生电荷共享的最大敏感节点间距在2.0~3.0 μm 之间。当敏感节点间距大于电荷共享可发生的最大间距后,间距的改变对电路的SEU 性能影响减弱,这是因为随着间距的增大,由电荷共享引起翻转的有效轰击位置显著减少。

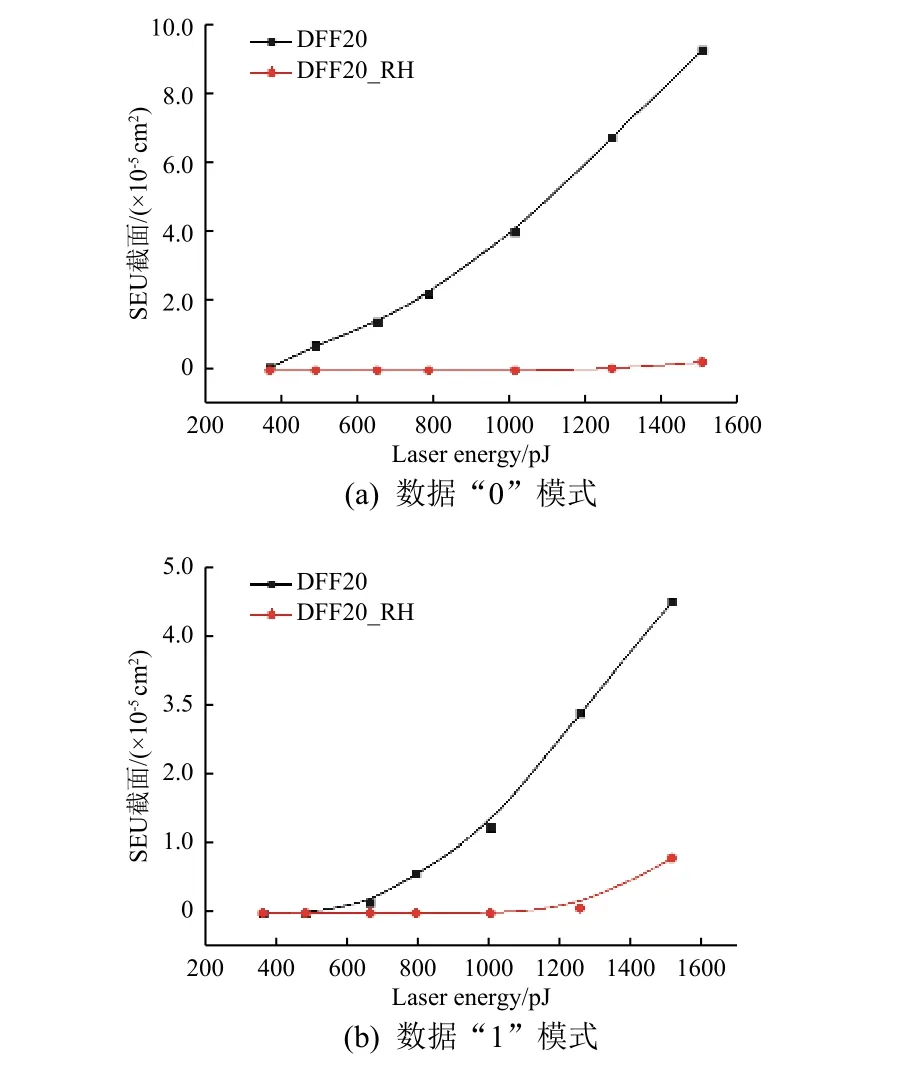

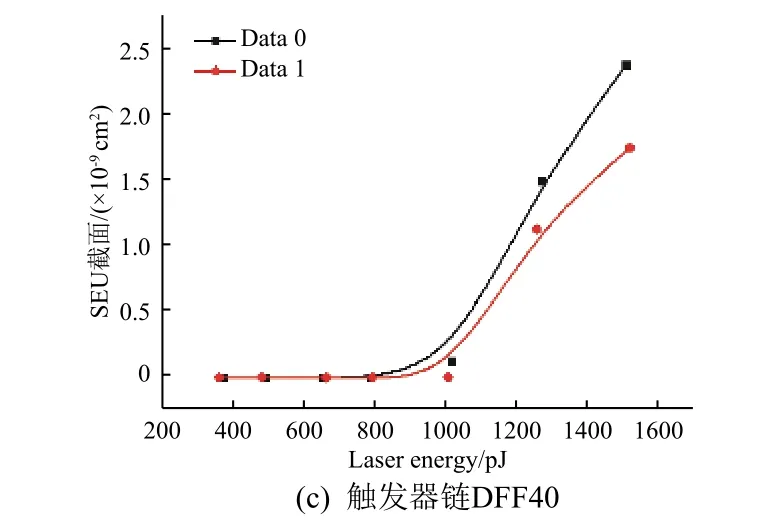

2.2 保护环和保护漏加固后的DFF链的SEU敏感度

图5所示为经保护环(PMOS管)和保护漏(NMOS管)加固后的触发器链和未经加固的触发器链在不同激光能量辐照下的SEU 截面,其中(a)为数据“0”测试模式下的结果,(b)为数据“1”测试模式下的结果。可以看出:数据“0”模式测试时,未经保护环和保护漏加固的电路在激光能量为490 pJ(等效LET 值为20.2 MeV·cm/mg)时即发生了SEU,而经保护环和保护漏加固的电路在1265 pJ(等效LET 值为52.1 MeV·cm/mg)时才发生SEU;数据“1”模式测试时,未经保护环和保护漏加固的电路在激光能量为660 pJ(等效LET 为27.2 MeV·cm/mg)时发生了SEU,而经保护环和保护漏加固的电路在1250 pJ(等效LET 值为51.5 MeV·cm/mg)时才发生SEU。将能诱发电路发生翻转的最小激光能量作为引发SEU 的能量阈值的粗估,对比可以发现,经保护环、保护漏加固设计后的触发器链的SEU 阈值约是未加固触发器链的SEU 阈值的2倍,具有较佳的抗SEU 性能。

图5 加固和未加固触发器链的SEU 截面Fig.5 SEU cross-section of DFF chain with and without hardening

图6(a)、(b)、(c)分别给出了MOS管版图的标准结构、保护漏结构和保护环结构。对于P衬底中的NMOS管来说,电荷收集主要是受漂移和扩散机制影响,当重离子轰击NMOS管的敏感位置漏极时,保护漏反偏的P-N结可充当二次收集电荷区域,能有效缓解漏区漂移和扩散电荷的收集,从而加速输出节点的电压恢复。对于N阱中的PMOS管来说,其电荷收集过程受寄生双极晶体管的双极放大效应影响更大,而PMOS周围的保护环结构有助于维持阱区域的电势,从而限制了寄生双极晶体管的电荷收集放大作用。因此采用保护漏和保护环加固的触发器链电路表现出了更高的抗SEU性能。

图6 MOS管的标准结构和加固结构示意Fig.6 Schematic diagram of the standard structure and the hardening structure of MOS

2.3 不同数据模式下DFF链的SEU敏感度

图7所示为不同触发器链在数据“0”和数据“1”测试模式下发生SEU 的截面对比结果。从图可以看出,随着激光能量的增加,DFF20、DFF30、DFF40触发器链的SEU 截面均增大。值得注意的是,3条触发器链在数据“0”测试模式下的SEU 截面均明显高于数据“1”测试模式下的。在激光能量为1500 pJ(等效LET 值为61.7 MeV·cm/mg)时:DFF20链在数据“0”测试模式下的SEU 截面比数据“1”模式测试下的SEU 截面高约106%;DFF30链在数据“0”测试模式下的SEU 截面比数据“1”模式下的SEU 截面高约40%;DFF40链在数据“0”测试模式下的SEU 截面比数据“1”模式下的SEU 截面高约35.7%。

图7 不同触发器链在2种测试模式下的SEU 截面Fig.7 SEU cross-section of DFF chain under data“0”and data “1” test

因电子的迁移率大于空穴迁移率,所以在相同的辐射环境下NMOS漏极收集的电流要大于PMOS漏极收集的电流,故而截止的NMOS管比截止的PMOS管更加敏感。敏感晶体管的类型不同可能是造成电路在数据“0”和数据“1”两种测试模式下SEU 敏感度不同的内在原因。当锁存数据为“1”,即节点n1=n3=1,n2=n4=0 时,晶体管P2、P20、P4、P40、N1、N3(图8中名称标红的晶体管)处于反向偏置状态,其漏端(图8中阴影标注)是电荷收集的敏感区域。与数据“0”测试模式下敏感晶体管(图4(b)中名称标蓝的晶体管)的分布对比可以发现,数据“0”测试模式下容易发生电荷共享从而造成电路产生SEU 的敏感晶体管为N20和N4,而在数据“1”测试模式下容易发生电荷共享从而造成电路产生SEU 的敏感晶体管为P20和P4。

图8 数据“1”模式下的敏感晶体管示意图Fig.8 Schematic diagram of sensitive transistors in data“1” test

图9所示为NMOS经保护漏加固、PMOS经保护环加固的触发器链DEF20_RH 在两种数据测试模式下的SEU 截面,其更敏感的测试模式并非为数据“0”,而是数据“1”。这个结果表明,不同加固结构下MOS管的敏感度不同,对于试验触发器链的电路和版图设计,经过保护漏加固的NMOS管比经过保护环加固的PMOS管具有更高的抗辐照能力,这从侧面说明,晶体管敏感度的差异将影响电路在不同数据模式下的SEU 敏感度。

图9 DFF20_RH 在数据“0”和数据“1”模式下的SEU 截面Fig.9 SEU cross-section of DFF20_RH in data“0”and data“1” test

3 结束语

通过对65 nm 体硅CMOS工艺下不同设计的触发器链的SEU 敏感度研究发现:

1)小尺寸器件设计中,DICE结构的DFF电路会因电荷共享而发生SEU,因此可适当增大敏感节点间距来提高器件的抗SEU 性能;但是当敏感节点间距较大时,其增加后的加固效果减弱,对于65 nm 体硅工艺的DICE电路DFF,采取3.0μm 的敏感节点间距即可有效降低电路的SEU 敏感度。

2)触发器单元中NMOS管经保护漏加固和PMOS管经保护环加固后的SEU 阈值可提高约1倍,有效降低了电路的SEU 敏感度。

3)不同类型的敏感晶体管在不同数据测试模式下触发器链的SEU 敏感度不同,因此设计芯片时有必要针对最敏感数据测试模式下最敏感的晶体管进行有效加固。此外,脉冲激光作为一种地面模拟手段,可有效用于确定SEU 敏感器件设计的最佳间距和验证防护效果。