基于CMOS 工艺的高线性宽带放大器芯片设计*

2021-03-11李烁星萌何

何 宁 李烁星 张 萌何 乐

(1.航天科工通信技术研究院有限责任公司,四川 成都 610051;2.东南大学航天科工通信技术研究院 量子信息与通信联合研究中心,江苏 南京 211100)

随着CMOS 亚微米及深亚微米工艺发展[1],器件的特征频率不断提高,当前工艺节点可达到100 GHz以上[2],可实现RF(Radio Frequency)前端单元器件制备,完成微波射频前端与后端数字电路集成,实现整个微波收发芯片单片集成,使硅基微系统成为现实。基于CMOS 工艺实现RF 前端电路设计与制备为当前的研究热点之一[3]。

当前无线通信技术是向高速化、大带宽等方向发展。宽带放大器为射频收发系统第一级系统,需要有放大信号,抑制各级电路噪声,改善通信系统灵敏度等性能要求,对整个接收系统的性能指标起着关键作用[4]。本文基于TSMC 0.18 μm RF CMOS 工艺设计了一款高宽带高线性放大器,主要采用三级级联结构,实现在500 MHz~2.5 GHz 频率范围内工作性能良好,可同时满足P 波段、L 波段及S 波段综合射频(通信、雷达、电子战)收发系统中实现应用。

1 基本系统设计方案

硅基衬底电子迁移率差,本征跨导较低[5],为实现低噪声、高增益、高带宽等特性指标,本宽带放大器设计采用三级级联结构。原理框图如图1 所示,电路主要由输入级、中间级和输出级三个模块组成,输入级实现射频宽带信号匹配及低噪声放大功能,中间级对低噪声信号进行宽带延展电压增益,输出级对射频信号进行输出匹配及功率驱动。

图1 放大器芯片原理框图

多级级联电路的噪声系数(Ftotal)表示如下[6]:

式中,GAi为第i级放大器的资用功率增益,Fi为第i级的噪声系数。公式表明,第一级噪声系数F1在整个系统噪声Ftotal中占主导地位,产生噪声直接影响整个收发系统噪声性能,增益GA1对后续电路的噪声系数具有抑制功能。因此,输入级作为放大器第一级联模块,除需要实现宽带频率范围内阻抗匹配功能以外,必须要有较低噪声系数,一定的功率增益以抑制后续电路噪声,但过高增益会拥塞后级电路,增加后级电路的设计难度,且过大增益和线性度会影响整个系统线性度。因此,输入级主要采用宽带低噪声放大器设计结构。

兼顾宽带匹配和噪声性能的输入级模块以及输出匹配和功率驱动的输出级模块增益不高,因此中间级模块要实现高增益,同时延展带宽的功能,主要采用高电压增益的分布式放大器结构设计。因前两级具有较高的输出阻抗,输出级要实现射频信号的输出匹配,同时要有较高的功率增益,并兼顾线性度和输出匹配特性,故采用功率放大器设计方法以实现匹配、高功率输出及高线性度等特性。

2 电路设计

2.1 输入级放大器电路

低噪声放大器一般采用共源结构、共栅结构及共源共栅结构三种设计方案。共源和共源共栅结构放大器在窄带内能够提供较高增益并具有较小的噪声系数[7],但具有寄生参数不确定性,当涉及ESD电路及芯片键合封装时,键合线电感值为3 nH,ESD电路二极管寄生电容至少为200 fF[8],寄生参数对输入阻抗产生很大的影响,匹配时会出现较大的频率偏移从而导致偏差。

本次输入级放大器设计采用共栅结构,共栅结构输入端近似实阻抗,ESD 保护电路及键合线寄生参数对输入阻抗的影响较小,能轻易解决寄生参数影响,易于实现宽带匹配,且输入端不需要额外的片外匹配元件,可以避免片外元件值偏差引起芯片误差。共栅结构输入阻抗公式如下所示[9]:

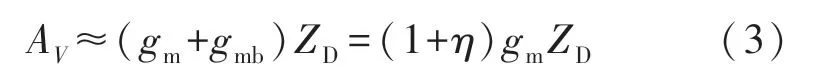

式中:gm为晶体管跨导;gmb为背栅跨导;ro为输出电阻;ZD为连接晶体管漏极的等效负载阻抗。从公式可以看出,通过调整gm和ZD,可以改变输入阻抗近似至50 Ω,与天线相匹配,从而满足输入端阻抗匹配的要求。但共栅结构的缺点是增益偏低、噪声偏大,其电压增益为[9]:

通过式(2)、式(3)可以发现,若得到较低的输入匹配阻抗,负载阻抗ZD要降低,要获得较高增益,ZD要提高,即ZD不能同时满足匹配与增益性能要求。为解决ZD在输入匹配阻抗和增益间的矛盾,本次设计的输入级放大器采用两级共栅电路级联的结构,具体原理图如图2 所示。

图2 输入级宽带放大器原理图

其中M1为第一级电路,M2为第二级共栅电路,输入信号Vin从M1源极馈入,输出放大信号从M2漏极输出。M2漏极端连接大阻值电阻Rd以实现较高电压增益要求。M2栅极连接Vdd 恒定值,对M1与输出信号Vout具有隔离作用,从而有效防止输出端信号Vout对输入端Vin造成干扰,使输入输出匹配可以各自相对独立完成,并以此保证输入级放大器的反向隔离度要求。

2.2 中间级分布式宽带放大器

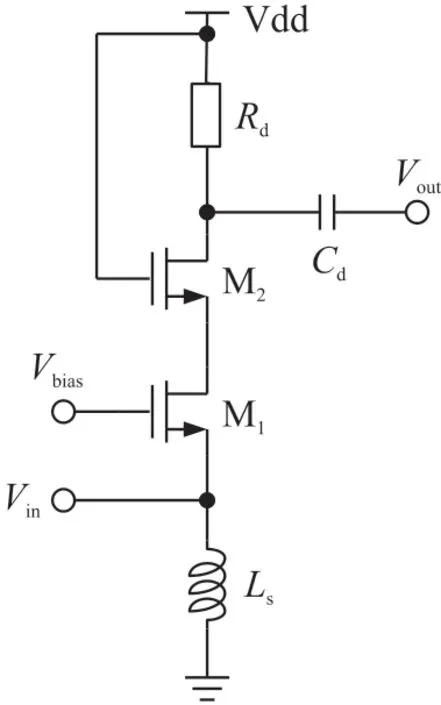

中间级放大器在宽带频率范围内为级联链路提供足够的电压增益,为延展带宽,采用分布式放大设计。具体电路结构模型如图3 所示,电路采用三级分布式放大,为降低级间匹配难度,减少电感使用,电路采用具有高输入阻抗的共源结构,采用电压传输方式,三个晶体管输入端分别连接在一条延迟线上,输出端则连接在另一条延迟线上。

图3 中间级分布式宽带放大器原理

其主要原理是利用晶体管的寄生电容构成人工传输线,将晶体管寄生电容作为传输线特征阻抗的一部分,在很宽频带内以延迟换取增益[4,7],理论上其工作频率只受传输线截止频率的限制,从而实现增益与延迟的互换而不影响带宽;但阻抗Z0无法达到很大的值,因此要获得很高的增益必须消耗较大的功率[7]。每段传输线的延迟为Δt,输入信号沿传输线传播,第i个放大器输入端的信号为Vin(tiΔt)。单个放大器输出端的等效负载为Z0/2,故每级放大器的增益为-gmZ0/2。输出信号也沿传输线传播,因此三级放大器的总输出电压为:

以此类推,可以得到N级放大器总增益为:

2.3 输出级功率放大器

满足全频带内稳定是放大器工作必须满足的首要条件,如果放大器在某一个频率点上产生自激,那将无法正常工作。放大器的稳定性可以分为绝对稳定和潜在不稳定两种情况。绝对稳定即对于任意的无源负载和信号源阻抗都能稳定地工作,潜在不稳定即对负载阻抗和信号源阻抗不能任意选取。大多数情况下,放大器被要求是绝对稳定的。因工艺、结构、性能的差异性,放大器通常用S参数来考察射频绝对稳定性,其绝对稳定条件如下公式所示[7]:

式中:D=S11S22-S12S21;K称为稳定性判别系数,K>1表示稳定状态。S12表示晶体管内部反馈量,为电压波反向传输系数;S12越大,内部反馈越强,反馈达到一定强度时,将会引起放大器稳定性变差,甚至产生自激振荡;S21表示正向传输系数,在同样反馈系数S12下,S21越大,反馈功率越强,影响放大器稳定性。当式(6)中三个条件同时成立,才能保证放大器是绝对稳定。否则为潜在不稳定状态,放大器就有可能发生自激振荡。

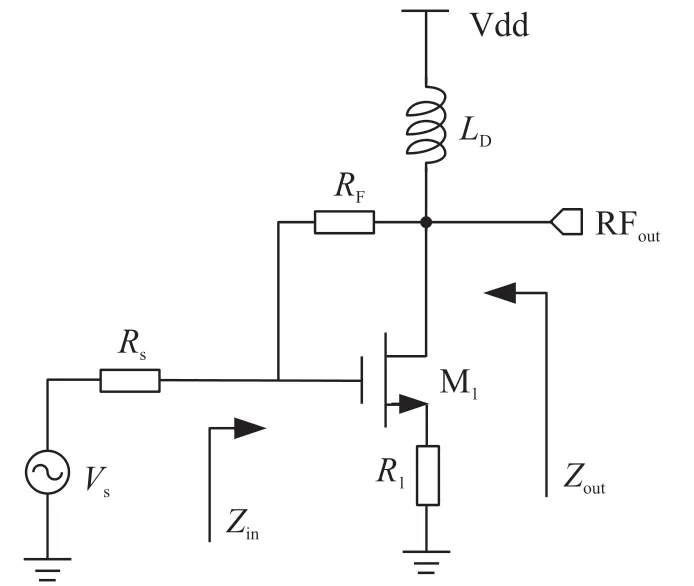

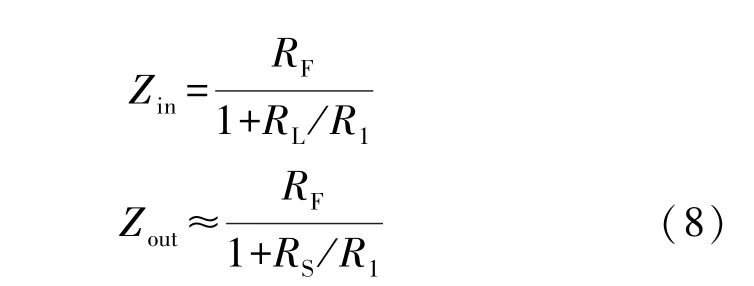

输出级功率放大器电路如图4 所示,其中Rs为信号源阻抗,RF及R1为反馈电阻。为获得较高的射频端口电压驻波比,输出级电路采用单级共源结构和电感负载设计,电感负载具有负载无压降且等效的双电源特性,线性度可大幅度提高。但该结构在高功率输出时极易产生自激振荡,因此在此基础上,加入电阻RF负反馈结构,可延展带宽,进一步提高稳定度和线性度。该结构组合使用了并联和串联反馈,又被称为并联串联放大器。其输入阻抗为[8]:

图4 输出级放大器原理图

式中:A为放大器的电压增益,若R1远远大于1/gm1,且RF足够大,则A=-RL/R1,其中RL为负载电阻。将其代入公式,可以得到输入阻抗Zin与输出阻抗Zout:

从式(8)中可以看出,如不考虑寄生参数的影响,Zin和Zout都是与频率无关的量,很容易实现宽带输出功率匹配。

通过阻抗迁移扫描的仿真方法,可以在功率输出最优点和附加功率效率(Power Added Efficiency,PAE)最优点中,折中得到性能最能满足系统需求的阻抗设计。

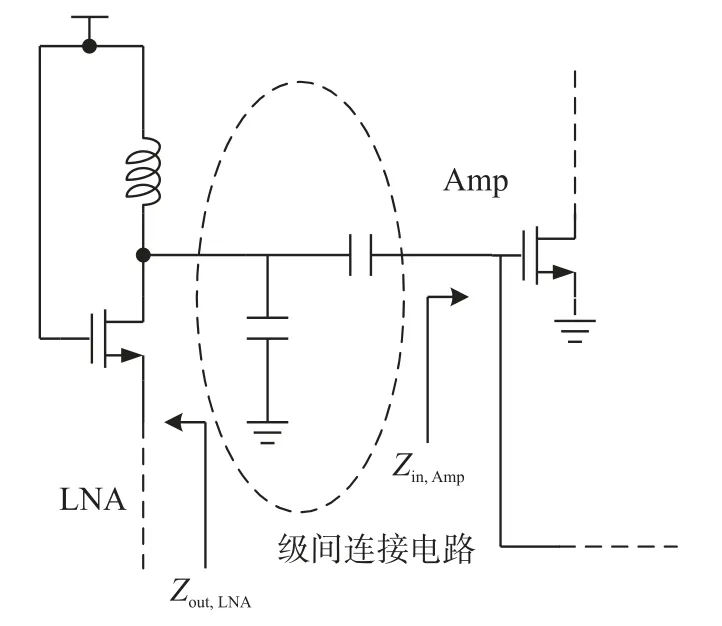

2.4 链路连接电路

在射频系统集成中,模块间链路连接十分重要,在较高频率下,不恰当的连接会造成信号严重反射,导致系统性能下降,尤其在级联电路中,需要充分考虑信号传递方式,如究竟是功率传输还是电压传输设计等因素。

为降低各级模块间信号反射,可采取多种解决方案,采用源极跟随器等有源电路,可有效地降低放大器的输出阻抗,但会增加系统额外功耗。本次设计的级联放大器采用无源器件电路连接,在两级间实现输入阻抗的共轭匹配,但在无源元件的情况下,高实部模块匹配到低实部模块不单只使用电容元件,还要使用电感元件,而片上电感的Q值往往很低且面积庞大,对信号的无损传递和芯片面积的节约都很不利。因此本设计的中间级分布式宽带放大器采用具有高输入阻抗的共源结构,高负载阻抗的放大器级间匹配的实现就相对较为容易,只要微调整级间匹配电容,即可实现信号的有效传输,级间匹配电路如图5 所示。

图5 放大器级联级间匹配原理图

3 电路系统单片集成

本次设计的高线性宽带放大器芯片采用单片集成TSMC 0.18 μm RF CMOS 工艺设计流片,各级联模块及走线集成在同一硅衬底上,而硅单晶是半绝缘的衬底材料,衬底耦合较为严重,模块之间的隔离度性能会直接影响系统的功能,如何尽可能地减小各个模块之间的相互耦合、干扰以提高系统整体性能是一个重要考虑因素。

本次设计的级联放大器系统中,输入级交流信号最弱,最容易受噪声的影响,该模块采用N+和P+双保护环包围,其相当于一堵屏蔽的墙,将核心电路保护在墙内,避免外部信号对保护墙内电路的干扰。输出级模块信号较强,对其他电路的影响较大,工艺采用深N 阱(Deep N Well,DNW)隔离,其剖面图如图6 所示,相当于在衬底上制作了一个碗状的保护空间,将电路嵌在该空间内,可以有效阻止保护空间内的电路信号泄漏。级间传输信号采用管道包围屏蔽的方法,为减小信号从过孔之间的缝隙泄漏,每层的过孔均错位放置。

图6 深N 阱DNW 剖面图

本设计的宽带放大器芯片显微图如图7 所示,芯片面积约0.7 mm×1.2 mm,芯片左、右侧分别为ground-signal-ground(GSG)焊盘,作为射频输入输出信号端口,上下端分别为Vdd,Gnd 直流焊盘。

图7 宽带放大器芯片显微照片

4 测试结果分析

放大器工作测试电源电压为3.3 V,电流为50 mA。芯片的S参数测试结果如图8 所示,芯片的测试输入频率从500 MHz 到3 GHz 范围内,宽带匹配S11小于-10 dB,具有较低的驻波。增益S21从500 MHz 到2.5 GHz 范围内大于16 dB,3 dB 带宽大于1.5 GHz,相对带宽达到100%,芯片的反向隔离度S12在500 MHz 到3 GHz 范围内小于-40 dB,反向隔离度性能良好。由于兼顾功率输出能力,S22满足在500 MHz~3 GHz 范围内小于-7 dB,噪声系数NF在全工作范围内小于5 dB,OP1dB大于9 dBm,饱和输出功率大于15 dBm。从测试结果来看,本文设计的宽带放大器具有宽的工作带宽1.5 GHz,较好的线性度,并兼顾了噪声性能。测试结果汇总如表1所示。

表1 宽带放大器芯片测试结果

图8 宽带放大器芯片S 参数测试结果

综合评价器件性能需要多项性能参数,而品质因子优值FOM(Figure of merit)函数覆盖多项参数,使用单一数值表示,可对放大器电路进行整体性能评价。为了兼顾放大器增益、工作带宽、线性度、功耗以及噪声等性能参数评价,参考相关文献[11,14],定义FOM 函数如下:

为防止负值出现,线性度采用OIP3衡量,OIP3可依据IIP3与增益进行计算,而现实中IIP3测试具有一定难度,可依据IIP3与增益1 dB 压缩点之间约9.6 dB 相关性进行计算[7],具体公式如(10)所示:

经计算本次设计的宽带放大器芯片FOM 值为89,具有较好的综合性能。

5 结论

本文对宽带放大器芯片设计进行了详细分析,对各级低噪声放大器、分布式放大器、功率放大器以及级间匹配电路设计理念进行了讨论,最终完成系统芯片的设计与工艺流片,芯片的测试结果验证了理论分析的正确性。

芯片测试结果显示,本次设计的宽带放大器芯片同时满足P 波段、L 波段及S 波段等多频段要求,相对带宽达到100%,具有较高增益,较好的线性度好、饱和输出功率大,良好的匹配特性以及较低的噪声系数。在CMOS 工艺下实现的指标已接近Ⅲ-Ⅴ族化合物半导体工艺芯片水准[10]。表2 为近年来相关放大器芯片数据成果对比,表中数据表明本文设计的芯片整体性能处于较高水平,具有较高的成本优势及实用价值。

表2 CMOS 宽带放大器芯片研究数据对比