基于Zynq-7000的千兆以太网传输系统设计与实现

2021-03-06杨振雷刘承敏青先国朱宏亮蒋天植罗庭芳

杨振雷 刘承敏 青先国 朱宏亮 包 超 蒋天植 喻 恒 李 进 罗庭芳 袁 航 单 伟

(中国核动力研究设计院核反应堆系统设计技术重点实验室成都610213)

随着核能行业的快速发展,核仪控系统复杂度逐渐提高,数据传输量也迅速增长,对数据传输提出了较高要求。传统核仪控系统通常采用控制器局域网络(Controller Area Network,CAN)或外围设备互连(Peripheral Component Interconnect,PCI)等数据总线进行数据传输,CAN总线具有实时性强、开发周期短、稳定性高的优势,已经成为计算机控制系统和嵌入式工业控制局域网的标准总线。但CAN总线数据通信速率最高只有1 Mbps,在一定程度上已经难以满足数据传输需求;PCI总线结构非常复杂,最大传输速率也不超过133 Mbps。在现有的核仪控系统中,工业以太网逐渐得到广泛的应用,例如分布式控制系统(Distributed Control System,DCS)、堆外核测量系统、辐射监测系统等均开始采用工业以太网技术,商用的核仪控系统主要以百兆以太网为主。随着以太网技术的发展和普及,将千兆以太网技术已成为当前核仪控系统研究的热点和趋势[1-2]。相对于传统的数据通信模式,千兆以太网技术在数据传输速度、传输距离、组网架构等方面均有较大的技术优势[3-4]。

目前,嵌入式千兆以太网硬件方案有多种实现方法[5-9],例如基于单片机、ARM(Advanced RISC Machine)平台、DSP(Digital Signal Processing)平台和FPGA(Field Programmable Gate Array)平台等。国内外众多高校和研究机构在大科学装置中均采用了嵌入式以太网解决方案,欧洲核子研究组织的Gnemmi等[10]基于FPGA实现了多种以太网硬件方案,在大型强子对撞机(Large Hadron Collider,LHC)强辐照环境下开展传输系统可靠性研究;中国科学技术大学的吴旭等[11]在大型高海拔空气簇射观测站(Large High Altitude Air Shower Observatory,LHAASO)设计了一套基于Xilinx公司Virtex-5系列的千兆以太网数据传输系统,数据传输速率可达237 Mbps,满足工程测量需求;中国科学院上海应用物理研究所的周大勇等[12]在上海光源(Shanghai Synchrotron Radiation Facility,SSRF)控制系统中采用以太网技术使设备控制器直接连接至控制网络,简化了控制系统结构,同时便于系统维护和升级。可见,嵌入式以太网硬件方案已经广泛应用于国内外大科学装置的科学研究与工程应用中。

随着半导体技术的发展,可编程逻辑器件制造商Altera(现被Intel收购)和Xilinx均推出了SoC(System on Chip)器件,SoC器件将ARM处理器的软件可编程性与FPGA的硬件可编程性进行了有效集成,既能实现硬件加速与数据处理功能,又集成了多种硬核以及混合信号处理功能。本文以Xilinx公司Zynq-7000型SoC作为开发平台,充分利用ARM和FPGA集成的优势,设计了一套用户数据报协议(User Datagram Protocol,UDP)千兆以太网传输系统架构,然后采用ModelSim仿真工具对系统功能进行了仿真验证,最后基于Xilinx的开发板ZC706对系统方案进行了具体实现和功能性能验证,并给出了最终的实际测试结果。

1 传统以太网方案

1.1 Zynq简介

Xilinx公司的Zynq-7000是第一代可扩展处理平台,作为一款可编程SoC器件,将ARM处理系统(Process System,PS)和FPGA可 编 程 逻 辑(Programmable Logic,PL)进行有效集成。具体而言,Zynq内部包含一个双核ARM Cortex-A9处理子系统和28 nm工艺的可编程逻辑子系统,PS和PL之间 采 用 了ARM的AXI(Advanced eXtensible Interface)总线进行数据交互,共包含AXI_ACP(AXI Accelerator Coherency Port)总线、4个AXI_HP(AXI High Performance Port)高 性 能 接 口、4个AXI_GP(AXI General Purpose Port)通用接口。另外,PS部分集成了多种常用的外设接口。SoC器件的产生,使得嵌入式系统的结构更为简捷和灵活,并在一定程度上提高了系统的可靠性和性能。

1.2 方案架构

基于Zynq-7000的千兆以太网硬件方案有多种实现方式。Xilinx推荐了三种千兆以太网实现方式[13],如图1所示。

1)方案一:PS部分实现方式

Zynq-7000的ARM中集成了两个数据链路层MAC(Media Access Control)硬 核GEM(Gigabit Ethernet MAC)。因此,物理层采用外置Marvell公司的PHY(Physical)芯片,数据链路层直接使用其中一个硬核GEM0,协议层采用Linux以太网驱动实现,对外以太网物理接口采用RJ45连接器实现。

2)方案二:PS部分GEM硬核和PL部分PHY实现方式

PL部分采用Xilinx提供的1000 BASE-X PCSPMA IP核实现物理层功能,PS部分采用ARM的另一个GEM1硬核实现数据链路层功能,协议层采用Linux以太网驱动实现。由于1000 BASE-X PCSPMA IP核 采 用Xilinx的 高 速GTX(Gigabit Transceiver)接口,因此对外以太网物理接口采用SFP(Small Form-factor Pluggable)光纤接口,也可以采用SFP转RJ45接口实现。

3)方案三:PL部分Ethernet IP核和PL部分PHY实现方式

PL部分采用Xilinx提供的1000 BASE-X PCSPMA IP核实现物理层功能,PL部分采用Xilinx提供的AXI-Ethernet IP核实现数据链路层功能,协议层采用Linux以太网驱动实现。与第二种实现方式类似,对外以太网物理接口既可以采用SFP光纤接口,也可以采用SFP转RJ45接口实现。

以上三种方法通过不同的组合方式实现以太网功能,能够满足大多数应用场合需求。但是这三种方法均采用Linux以太网驱动作为协议层的实现,过多占用ARM的运行资源,并且未能充分利用SoC器件可编程逻辑部分的优势。因此,本文参考国内外厂商以太网传输系统的研制经验[14-15],提出了一种新的千兆以太网传输系统架构,协议层采用UDP面向非连接的传输协议,以满足现有项目提出的传输速度大于等于650 Mbps的实际需求。

2 总体方案

2.1 方案架构

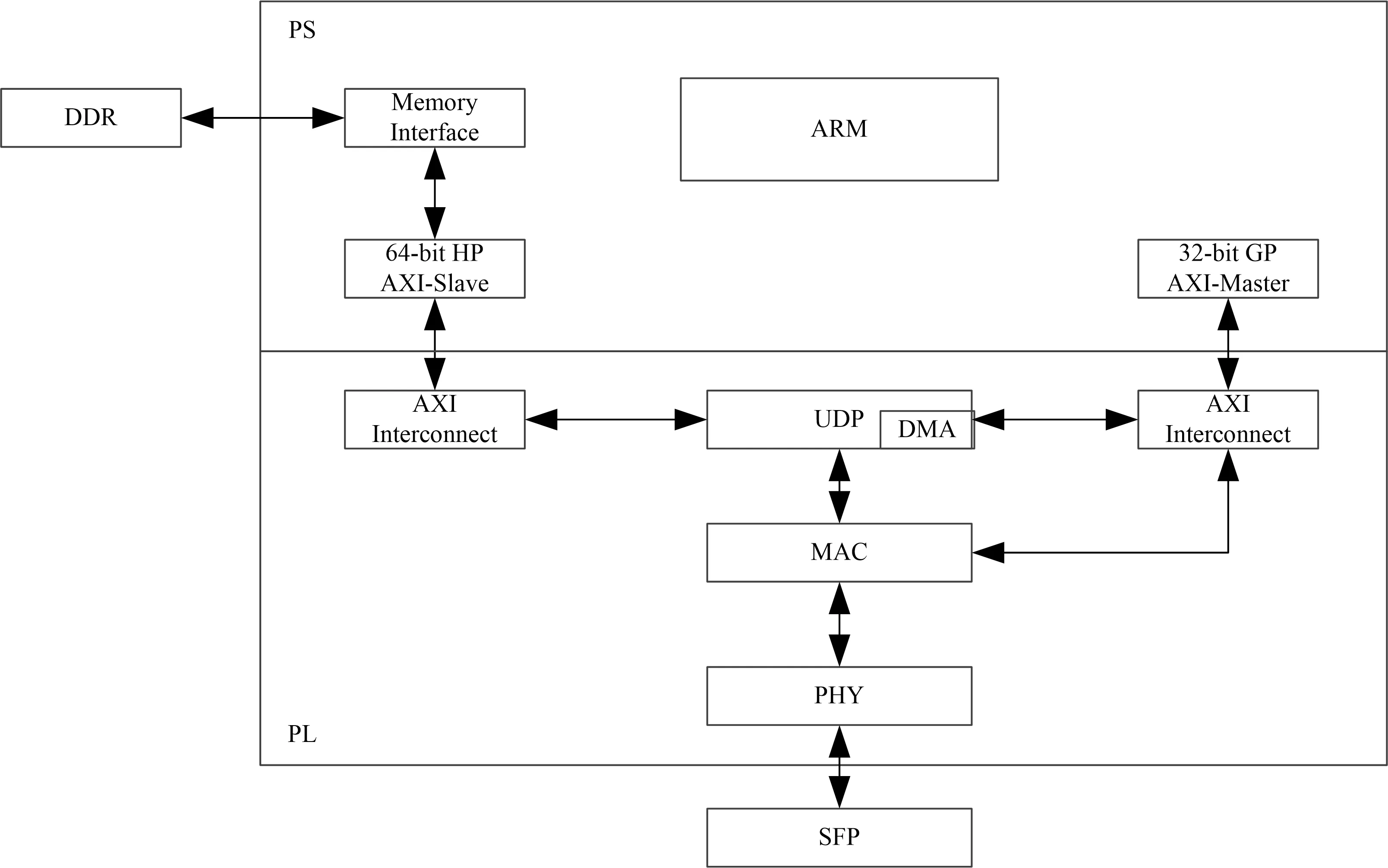

本文设计的系统方案如图2所示,在PL部分主要实现三部分功能:UDP模块、MAC模块、PHY模块。UDP模块主要实现UDP协议层功能,具体包括UDP接收和发送功能、数据帧解析功能、地址解析协议功能(Address Resolution Protocol,ARP)、网际报文控制协议功能(Internet Control Message Protocol,ICMP)以 及 数 据 存 储DMA(Direct Memory Access)功能;MAC模块主要实现以太网数据链路层的功能,并且实现管理数据输入输出接口(Management Data Input/Output,MDIO)功能,以及对PHY的配置功能。PHY模块,主要实现以太网物理层的功能,本部分采用Xilinx的1000 BASE-X PCS-PMA IP核实现。PS部分,通过32位GP总线对UDP模块、MAC进行配置和控制,例如IP(Internet Protocol)地址、MAC地址、地址掩码的设置以及内存(Double Data Rate,DDR)地址读写的控制等;通过64位HP总线实现UDP接收数据和发送数据到DDR的缓存功能。

2.2 UDP协议层实现方式

UDP协议层逻辑框图如图3所示,主要包含数据帧解析模块、UDP发送模块、UDP接收模块、ARP模块、ICMP模块、仲裁模块以及DMA模块。

2.2.1 数据帧解析模块

数据帧解析模块主要实现MAC帧解析的功能,通过数据有效信号对MAC帧字节计数,当MAC帧起始信号有效时,开始计数;当MAC帧结束信号有效时,结束计数;然后,按照以太网V2标准对MAC帧内容逐字解析,判断帧类型是否是IP数据报或者ARP协议帧;最后,再对IP数据报进行解析,过滤传输给本地的有效信息并解析帧携带的关键信息,例如源IP地址、目的IP地址、IP数据报长度等。

图2 以太网传输系统顶层系统框图Fig.2 Top system diagram of Ethernet transmission system

图3 UDP协议层结构图Fig.3 Framework of UDP protocol

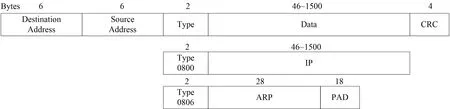

以太网V2标准MAC帧格式如图4所示,通过对MAC帧内容进行解析,按照帧字节计数(包计数大于等于6且小于等于11)得到源物理地址。按照帧字节计数判断数据报类型,若包计数等于13且数据类型码为0x0800,则帧类型为IP数据报;若包计数等于13且数据类型码为0x0806,则帧类型为ARP协议。若帧类型为IP数据报,本模块需要根据字节计数,检查IP数据报中的IP地址是否与本地IP地址匹配,若匹配,则继续根据IP数据报字节计数获取IP数据报包头长度、源IP地址和目的IP地址等信息;若不匹配,则丢弃该帧。

2.2.2 ARP模块

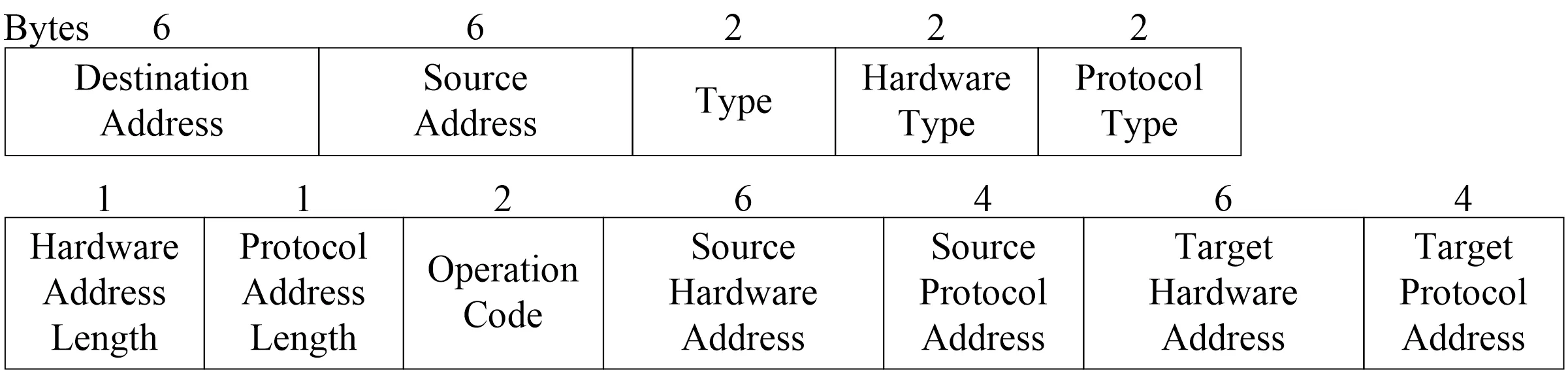

ARP模块主要用于检测ARP请求帧以及生成ARP应答帧。本模块首先检测MAC帧帧类型字段,若帧类型字段为0x04,表明为ARP帧;再检测是否为ARP请求信号,若操作码字段opcode为0x01,表明为ARP请求帧;再检测IP地址是否为本地IP地址,若与本地IP匹配,则为有效的ARP请求帧,按照图5所示的ARP协议帧格式生成ARP应答帧。为了尽快查找到IP地址到MAC地址的映射关系,本模块设计了ARP缓存区,存放一定时间周期内的IP地址与MAC地址的映射表,并保持动态更新。

图4 MAC帧格式图Fig.4 Diagram of MAC frame format

图5 ARP协议帧格式图Fig.5 Diagram of ARP frame format

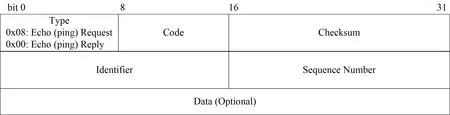

2.2.3 ICMP模块

ICMP模块主要实现ICMP请求包的检测功能以及生成ICMP应答包。与ARP模块处理类似,本模块首先检测输入MAC帧的协议类型字段,若输入信号中协议类型是ICMP协议,则继续检测该帧总字节计数,若帧总字节计数小于等于0x200,则继续检测该ICMP帧是否为ICMP请求帧,若是ICMP请求帧,则为有效ICMP请求包。按照图6所示的格式生成ICMP应答包。这里对ICMP请求报与ICMP应答报经对比发现,将ICMP请求包的MAC帧首部MAC地址互换,IP首部IP地址互换,ICMP报文中协议类型由0x08变为0x00,ICMP报文中校验和减少0x08,便能够生成ICMP报文应答包。

图6 ICMP报文格式图Fig.6 Diagram of ICMP frame format

2.2.4 UDP接收模块

UDP接收模块主要实现UDP数据帧有效性检测以及UDP数据的接收功能。具体实现过程如下:

1)UDP校验和计算。在UDP首部前面增加12字节的伪首部,分别为4字节的源IP地址、4字节的目的IP地址、1字节(字节内容为0)、1字节(字节内容为6)、2字节的UDP长度,然后对伪首部、UDP首部、UDP数据部分按照二进制反码运算求和,同样,若UDP数据个数为奇数,需填充全0字节构成偶数进行计算,最后,对计算出的结果求反码进而得到UDP的校验和。

2)UDP数据帧有效性检测。根据数据解析模块解析的内容,依次判断接收到的IP数据报内容是否是UDP协议、目的端口号与本地端口是否匹配,然后再检测UDP校验和是否正确。如果以上内容均不正确,判断帧为无效帧,丢弃处理。

3)接收数据。当检测到有效帧后,去除IP数据报首部、UDP首部,便可得到UDP的有效数据部分。

2.2.5 UDP发送模块

UDP发送模块主要实现IP校验和计算、UDP校验和计算、数据组帧以及数据发送功能。具体实现流程如下:

1)将发送数据进行缓存。将发送数据写入缓存,当缓存数据量达到一定的数据量时,将缓存数据读出。

2)计算IP首部校验和。IP首部校验只针对IP数据报的首部进行校验。IP数据报校验的基本单元为2字节的数据,所有的2字节数据进行反码算术运算求和,最后得出的结果再取反码得到IP首部校验和。

3)计算UDP校验和。在UDP数据报首部前面增加12字节伪首部,然后对伪首部、UDP首部、UDP数据进行反码算术运算求和,对计算出的结果再求反码得到UDP首部校验。

4)MAC帧封装。按照MAC帧的标准格式生成MAC帧头、IP首部和TCP首部,最后结合UDP数据区,形成一个完整的MAC帧发送出去。

2.2.6 DMA数据存储实现方式

DMA数据存储模块主要实现DDR读写功能。为了实现对DDR的快速读写,本模块按照AXI4的读写时序进行设计。当UDP接收数据缓存到一定数据量时,AXI请求信号置高,AXI读写信号置高,表明将要执行写操作,DMA模块从FPGA内部缓存的相应地址读取规定长度的数据写入到DDR相应地址空间中。当执行UDP发送操作时,AXI请求信号置高,AXI读写信号置低,表明将要执行读操作,DMA模块从DDR中相应地址读取规定长度的数据写入到FPGA内部缓存中,然后通过UDP发送模块发送。

2.3 数据链路层实现方式

数据链路层的设计结构图如图7所示,主要包括MAC接收帧解析模块、MAC发送帧封装模块、循环冗余校验(Cyclic Redundancy Check,CRC)模块、GMII(Gigabit Medium Independent Interface)接口模块以及PHY配置模块。MAC发送帧封装模块,通过解析物理层向数据链路层交互的GMII比特流,将数据链路层数据封装成GMII数据帧格式;MAC接收帧解析模块,针对接收方向的GMII比特流进行解析,从而得到MAC帧数据。CRC校验模块,主要实现接收方向MAC帧内容的正确性检测功能和发送方向的CRC校验值计算功能;GMII接口模块,依照IEEE802.3标准,实现MAC帧、GMII帧格式的转换;PHY配置模块,通过MDIO接口实现对PHY层的配置功能。

图7 数据链路层结构图Fig.7 Structure diagram of data link layer

3 实验验证

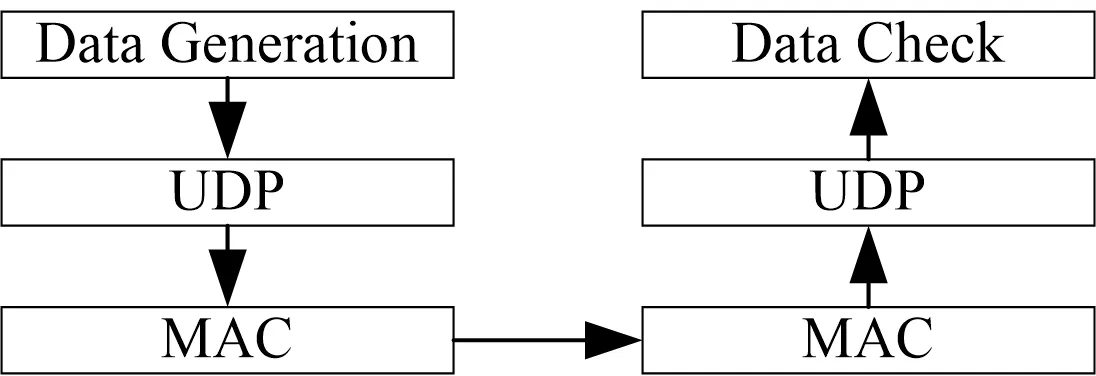

3.1 仿真验证

为了对设计方案进行验证,本文采用ModelSim进行了功能仿真。ModelSim是Mentor Graphics子公司Model Technology的产品,是逻辑设计重要的仿真工具之一。本文设计了图8所示的仿真验证框图,主要包括数据生成模块、数据检查模块、两个同样的UDP模块和两个同样的数据链路层模块,这样对UDP的发送模块和接收模块以及数据链路层模块都能进行完整的验证。

图8 仿真验证结构图Fig.8 Block diagram of simulation verification

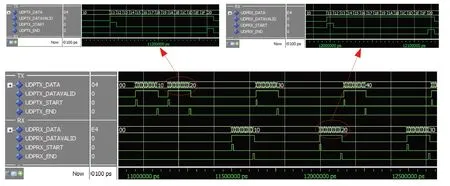

首先设置发送侧和接收侧的MAC地址、IP地址等,这里发送侧MAC地址设置为0x000102030405,IP地址设置为192.168.1.1,端口号设置为0x5678;接收侧MAC地址设置为0x001122334455,IP地址设置为192.168.1.2,端口号设置为0x1234。然后,数据生成模块生成累加数据并启动发送,为了便于观察,发送帧长度设置为16字节;最后,对接收侧的数据进行检查。若接收到的数据与发送的数据匹配,则表明方案合理。图9为ModelSim的仿真波形图,通过仿真结果可以看出,UDP发送的数据均能够完整接收到,表明整个设计方案在功能上是可行的。

3.2 性能测试

仿真验证完成以后,本文基于Xilinx的ZC706开发板进行了实际验证,对实际使用环境中的UDP协议栈的可靠性进行了验证。

图9 UDP发送和接收过程仿真波形图Fig.9 Simulation waveform of UDP sending and receiving process

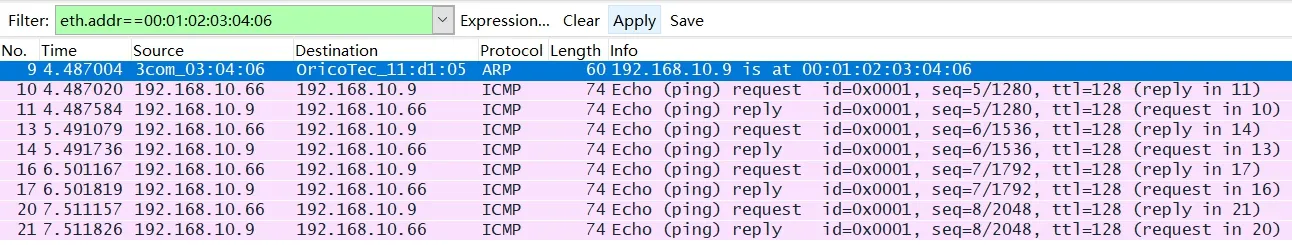

开发板的IP地址设置为192.168.10.9,MAC地址设置为0x000102030406,端口号设置为0x9119;工控机的IP地址设计为192.168.10.66,MAC地址为工控机的自身地址,端口号设置为0x1024。本文在SoC内部设计了数据生成模块不断地产生累加数据,并且通过设置数据产生的时间间隔来改变生成数据的速度,通过调整UDP数据包的大小对系统的传输速度进行了测试。

在测试传输速度前,首先通过工控机对开发板进行了PING操作,如图10所示,从图10可以看出,工控机与开发板网络已经连通。然后,对系统传输速度进行了测试,图11为不同UDP数据包情况下实际的数据传输速度。测试结果发现,当UDP数据包大小等于1 024字节时,数据传输速度约为830 Mbps,并且稳定性较好;当UDP数据包大小等于512字节时,数据传输速度约为870 Mbps,并且稳定性较好;当UDP数据包大小等于256字节时,数据传输速度约为750 Mbps,稳定性较差,当增加数据生成模块内数据产生时间间隔,即减小数据量,系统稳定性变好。

图10 ARP和PING验证结果Fig.10 Verification results of ARP and PING protocol

图11 不同UDP包大小的实际测试结果(a)256字节,(b)512字节,(c)1 024字节Fig.11 Actual test results of different UDP packet sizes(a)256 bytes,(b)512 bytes,(c)1 024 bytes

4 结语

本文基于Xilinx的SoC器 件Zynq-7000为研究对象,实现了一种新的UDP千兆以太网传输系统架构,对千兆以太网传输系统实现方式进行了详细描述,并对系统方案进行了功能仿真,最后在Xilinx ZC706开发板上进行了性能测试。测试结果表明:本文提出的UDP千兆网以太网传输系统架构具有较强的通用性,传输速度最高能够达到870 Mbps,能够满足绝大多数核仪控系统的实际需求。