基于1394网络的分布式组合导航系统时序建模与仿真

2021-03-05梁兆鑫王涛赵喆陈银超杨朝旭

梁兆鑫,王涛,赵喆,陈银超,杨朝旭

(航空工业成都飞机设计研究所 飞控部, 成都 610073)

0 引 言

分布式组合导航系统伴随着分布式网络拓扑结构的发展而产生,是现代航空电子系统的重要组成部分。与传统的集中式导航系统相比,分布式导航系统将多个不同种类的导航测量系统分散地安装在载体的不同位置,并通过总线连接,进行融合解算,这样既提高了系统的冗余度,又能够为飞行器提供更加精准且更为可靠的位置、姿态和航向信息。

分布式组合导航系统采用1394b总线网络进行通信。IEEE 1394总线又被称为火线(Fire Wire),是Apple公司于1985年提出的一个串行总线技术标准,1995年被美国电气和电子工程师协会(IEEE)正式认可,进而确立为通用标准。随着时间的推移,该标准被不断地修订、完善和改进,依次形成了IEEE 1394a、IEEE 1394a-2000以及IEEE 1394b-2002等标准。为了提高总线的可靠性、确定性以及总线网络的安全性,增强总线网络的管理手段,降低总线系统的消息延时,SAE(Society of Automotive Engineers)组织在IEEE 1394协议的基础上,从应用层角度考虑,对协议提出了进一步的限定和约束,形成了新的SAE AS5643协议。

常见的1394总线网络故障模式有3种:节点可达性故障、总线可用性故障以及数据可靠性故障。对于分布式组合导航系统,组合导航计算机通过总线实时获取各类传感器数据,是实现传感器信息融合算法的基础,倘若某传感器节点由于物理连接断开而出现不可达的情况,那么组合导航功能就无法实现。因此,为了保证分布式系统的总线网络拓扑的完整,避免可达性故障的出现,同时具备容忍一次网络断线故障的能力,必须在系统工作前对各节点的线缆连接情况进行检查。

针对1394总线网络测试的研究工作有很多。王仲杰等搭建了一套1394总线网络系统测试平台,实现了对1394总线网络的线缆特性、误码率、信号质量以及总线协议符合性等测试;杨峰等对1394线缆的结构及差分阻抗进行了理论分析,并使用专用设备对1394线缆的差分阻抗进行了测试;N.Takashi等利用建模和数值仿真手段,对两种队列模型下,1394总线网络异步流包的平均等待时间等性能进行了测试和分析。但现有的研究工作尚未涉及1394总线网络的完整性测试,且针对1394总线网络在完整性测试过程中时序问题的研究也未见报道。

针对上述问题,本文首先给出基于1394总线网络的分布式组合导航系统总线完整性检查方法,并以某次检查过程中出现的虚警故障为切入点,通过建模与仿真等手段,对总线完整性检查过程的时序问题进行研究。

1 1394总线网络完整性检查方法

SAE AS5643协议中给出了3种不同的总线拓扑结构,分别是:基本拓扑、带环的基本拓扑、带环的多余度拓扑。本文研究的分布式组合导航系统采用带环的基本拓扑结构,一个简单的环状1394总线网络,如图1(a)所示,其中Node1和Node2的两端分别与CC的端口P0和P1相连,构成总线环。在各个节点正确连接的情况下,端口P0的状态为active,即正常工作状态,而P1的状态为loop disable,处于环断开状态,CC通过端口P0与Node1和Node2进行通信。

带环的1394b总线网络具备环断开特性,即容忍一次网络断线故障,若总线环上某两个相邻节点间的线缆断开,CC的另一端口将被自动激活,确保节点能够通过另一个端口与CC进行通信。若Node1与Node2间的线缆断开,端口P1将被自动激活,从loop disable状态变成active,从而使Node2能够通过P1与CC进行通信,如图1(b)所示。不成环的基本拓扑结构,不具备环断开特性,一旦有线缆连接故障,该节点以后的所有节点都将掉线,无容错能力。

(a) 带环的基本拓扑 (b) 带环的多余度拓扑

为了便于对总线完整性检查方法和原理进行描述,首先介绍本文研究的分布式组合导航系统的组成和结构。该分布式系统如图2所示,总线控制器CC位于组合导航计算机(INC)中,并通过内部总线与CPU进行通信,其他远程节点总线网络接口子卡分别位于GPS、INS、CNS以及ADS之中,各个节点通过符合1394b标准的铜制双绞线相互连接,组成了带环的1394总线网络。总线网络中相邻两节点之间的信道被分别命名为Cable1~Cable5。需要说明的是,上文中所述信道包括线缆及其两端连接的电连接器。

图2 分布式组合导航系统示意图

1.1 基于SAE AS5643协议的总线收发数原理

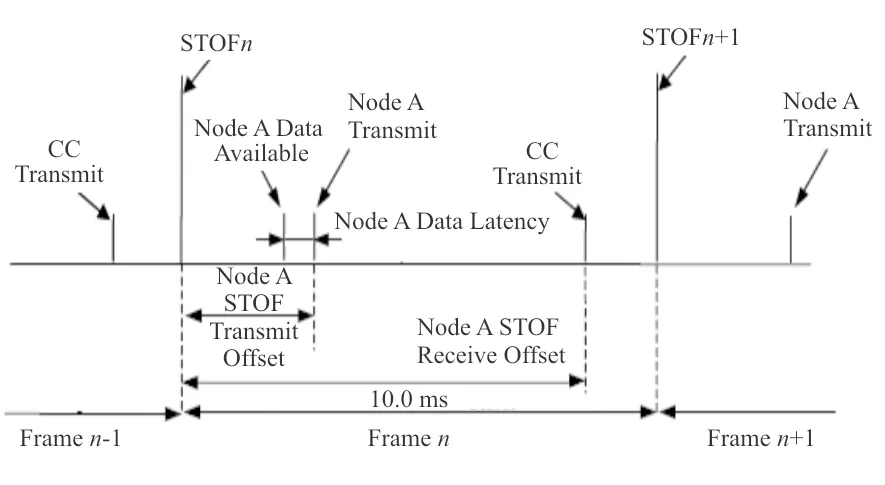

SAE AS5643协议规定了1394总线网络具有初始化和常规总线操作两个阶段。当总线上有任意节点断开或者上下电,都会使得总线进入初始化阶段,重新标识网络拓扑。在初始化阶段完成后,进入常规总线操作阶段,SAE AS5643标准对此阶段进行了详细规范,基本通信过程如图3所示。

图3 常规总线操作[10]

图3中STOF到STOF+1之间的时间称为一个完整的帧周期,帧周期可以与系统应用的任务周期相关联,实现总线上模块间同步。STOF称为帧起始包,只能由CC发起,每个RN节点都有唯一预定义的相对于STOF的发送偏移和接收偏移时间,节点仅在到达发送偏移时启动异步流包发送。总线上数据的传输行为由总线配置表进行定义,分布式组合导航系统采用的总线配置表如表1所示。

表1 分布式组合导航系统总线配置表

1.2 总线完整性检查方法

总线完整性检查可通过软件检查来实现,也可通过硬件检查来实现。分布式组合导航系统采用基于软件的总线完整性检查方法,具体步骤如下。

Step

1

向CC端口发送禁止指令,命令CC的端口P1处于禁止(disable)状态,人为地将总线环断开,在此情况下,若总线网络中存在故障信道,故障信道之后连接的节点都无法将数据继续向前传输。Step

2

由组合导航计算机软件对数据包更新情况进行检查,由近及远地依次检查远程节点发送至CC的数据包是否更新,若数据包更新,则表明该节点离CC近端的信道是完好的;若检查到数据包未更新,则表明该节点离CC近端的信道故障。结合图2,若检查到INS发送的数据包已更新,则说明信道Cable1正常,否则说明Cable1故障,若检查到CNS发送的数据已更新,则说明信道Cable2正常,否则说明Cable2故障,以此类推。本步骤可对信道Cable1~Cable4进行检查,但无法覆盖到Cable5。Step

3

向CC端口P1发送使能指令,命令CC端口P1恢复active正常工作状态,向CC端口P0发送禁止指令,命令CC端口P0处于禁止状态,使得GPS只能通过Cable5与CC进行通信,并通过检查GPS向CC发送的数据包是否更新来判断信道Cable5是否正常。1.3 组合导航计算机获取数据包更新标志的系统运行时序

在分布式组合导航系统中,当CC接收到总线节点在规定时刻发送过来的数据包后,会将该数据包更新标志置“1”,导航计算机软件将数据包信息读走后,会清除该数据包的更新标志。导航计算机软件通过检查该更新标志是否置位来判断数据包是否更新。

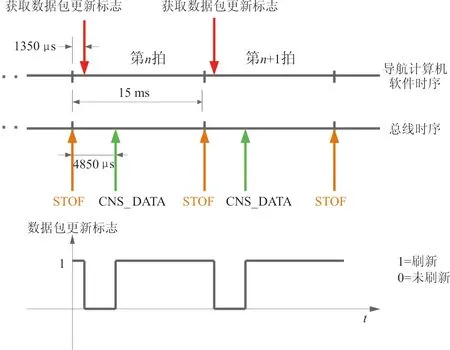

以CNS为例,组合导航计算机获取数据包更新标志的系统运行时序如图4所示。CC在组合导航计算机软件的控制下实现二者的同步运行,帧周期同为15 ms,根据总线配置表的定义,CNS在每周期开始后的第4 850 μs向CC传输其最新数据包。组合导航计算机软件在每周期开始后约1 350 μs读取CNS数据包中的信息,同时获取数据包更新标志。

若总线连接完好且CNS工作正常,那么按照上述时序,组合导航计算机每一拍获取的数据包更新标志都将为1。当系统运行总线完整性检查程序时,软件检查数据包更新标志为1,确认数据包已更新,判断该总线节点连接正常,信道完好。若数据包更新标志为0,则可以说明CNS与INS连接的信道Cable2故障。

图4 总线完整性检查时序(a)

2 虚警故障现象和原因分析

在某次试验过程中,组合导航计算机软件在运行总线完整性检查程序时,报出CNS与INS间信道故障,即采集到CNS的数据包更新标志为0,但总线分析仪记录的数据显示该节点通信正常,可确认该故障为虚警。在不改变总线网络的硬件连接状态下,进行多次重复试验,发现该故障无法稳定复现,属于偶发现象。

2.1 原因探究

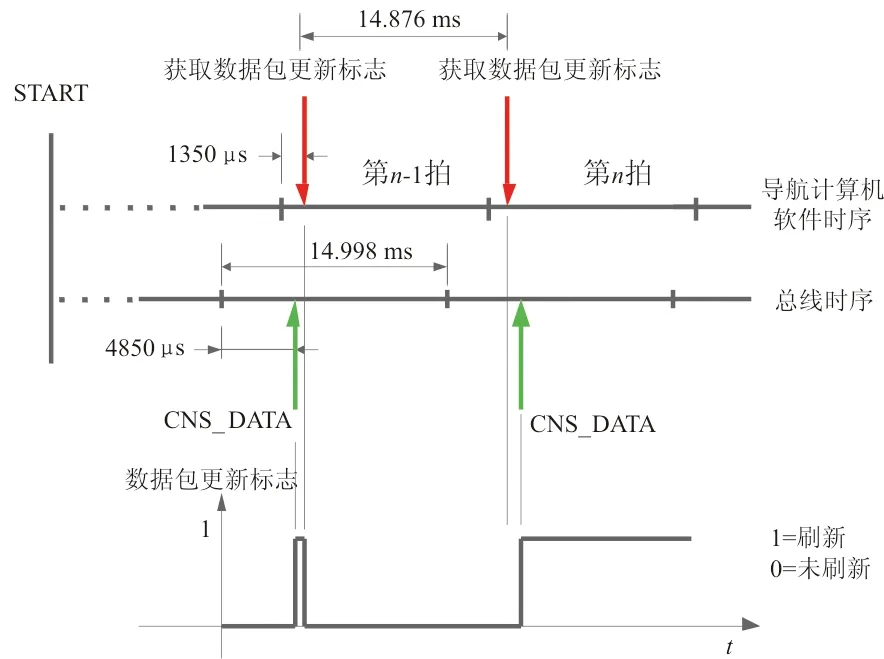

通过查看记录到的故障数据发现,由于组合导航计算机软件帧周期的起始阶段会进行同步等事务处理,其实际运行周期略小于15 ms,约为14.876 ms,而总线运行周期约为14.998 ms。实际上,总线完整性检查是分布式组合导航系统检查程序的一部分,组合导航计算机软件在执行系统检查程序时,总线控制器时钟源发生了切换,CC的运行周期不再由组合导航计算机软件控制,组合导航计算机与CC的运行分别采用不同的时钟,并且不同的时钟其精度也不相同,那么随着时间的推移,上述偏差逐渐累积,在某一时刻必然会出现时序,如图5所示。即在新的数据包到来之前,导航计算机读取了上一拍的数据包,并获取了已经被清零的数据包更新标志,故本文怀疑正是上述原因引起的虚警。

图5 总线完整性检查时序(b)

2.2 故障数据分析

为了对上述怀疑进行确认,进行多次试验,并对总线分析仪采集的试验数据进行详细分析。为了增大报故概率,还缩短了组合导航计算机软件的工作周期。

在故障数据中,本文最关注的是组合导航计算机软件进行总线完整性检查当拍的时序情况。在运行系统检查程序的第0拍,组合导航计算机与CC仍然是同步的,以该时刻作为起始参考点,并根据参数说明(如图6所示),按照以下步骤绘制时序图。

图6 时序图绘制参数说明

Step

1

绘制总线检查当拍(第n

拍)组合导航计算机软件运行时序。首先确认导航计算机软件进行总线完整性检查的那一拍相对于起始参考点的拍序号n

,并计算其相对时间T

。设P

为上位机软件运行周期,i

为拍次,总线检查拍次n

使用JTAG读取,同时还要使用JTAG获取数据包更新标志时刻的小帧偏移φ

。其中:

(1)

Step

2

绘制总线检查当拍(第n

拍)CC运行时序。在总线分析仪记录的数据中,将切换时钟后CC发送的第一个STOF包选为参考点,找到发送偏移最接近T

时刻的STOF包,并记录其发送时间T

,同时观察STOF包的实际发送周期P

。Step

3

比较分析。同时绘制导航计算机和CC在检查拍的前一拍(第n

-1拍)时序,观察相邻两拍中上位机软件获取数据包更新标志的时刻与CC接收到CNS发送最新数据包CNS_DATA时刻的相对位置关系,将时序分析结果与故障清单进行比较,判断系统功能是否正确。对试验过程中出现的故障数据和正常数据进行记录,并按照上述步骤进行分析。结果表明:当出现如图5所示的时序时,软件会报出总线连接故障,而当未出现如图5所示时序时,软件不会报故,这也印证了之前的怀疑。其中两次试验的试验数据如表2所示,第一组数据报故障,第二组数据正常。

表2 试验数据及结果

3 建 模

为了说明故障的偶发性,使用Inchron工具对系统进行建模和仿真。

3.1 时序建模

(2)

式中:T

为组合导航计算机软件运行第n

个周期的起始时刻;φ

=1 352 μs,为获取数据包更新标志时刻的小帧偏移;J

∈(-1 000 ps,1 000 ps),为服从均匀分布的抖动。为实现精确建模,对式(1)进一步展开,可得:

(3)

式中:P

=14.876 ms;ΔP

,~N

(0,100 μs),为第i

个周期的组合导航计算机软件运行周期偏差,该偏差服从正态分布。同样的,对CC的运行时序进行建模,设数据包发送时刻为t

,则总线上第m

个周期的数据包发送时刻为

(4)

式中:T

为CC运行第m

个周期的起始时刻;φ

=4 850 μs,为CNS_DATA最新数据包发送时刻的小帧偏移;J

∈(-1 000 ps,1 000 ps),为服从均匀分布的抖动。类似地:

(5)

用函数R

来表示总线完整性检查结果,当出现虚警时函数值为1,否则为0。根据上文分析及总线完整性检查原理,函数R

可以表示为

(6)

其中,case*为

(7)

若在总线完整性检查当拍及前一拍,上位机时序与总线时序存在式(7)所示关系,系统就会出现虚警故障。总线检查结果R

为ΔP

s,、ΔP

CC,、J

和J

的函数,而上述参数均存在一定的随机性,这也从根本上解释了该虚警故障偶发的原因。3.2 DPRAM双端口缓冲区读写逻辑建模

总线上各节点发送到CC的数据被存储在CC的DPRAM中,DPRAM存储器结构如图7所示。

图7 DPRAM存储器结构

双端口缓冲区存在两块存储区域,分别为缓冲区0和缓冲区1,FPGA第一次接收到消息后,默认将数据填入缓冲区0,同时将缓冲区0中数据包对应的更新标志置为1。第二次接收到消息后将数据存放在缓冲区1中,之后逻辑采用乒乓操作依次向缓冲区0和缓冲区1中写入数据。CPU获取总线数据时,将数据从DPRAM中搬运到SDRAM。由于DPRAM首先向缓冲区0中写入数据,为了避免读写冲突,主机在读取数据时,首先对缓冲区1进行操作,在读取完数据及其对应的数据更新标志后,将更新标志清零。

4 仿真与分析

使用Inchron工具对3.2节描述的DPRAM读写机制进行建模,并根据CC时序与组合导航计算机软件时序,对系统检查程序的运行进行100次仿真。在仿真过程中使用真实的系统参数,其中n

=120。在100次试验中,有28次出现了如图8~图9所示的情况,由于下个周期的数据包尚未到来,上位机软件连续两次读取DPRAM中同一片缓冲区,导致第二次读取缓冲区数据更新标志为0,引起虚警。

图8 单次总线完整性检查试验结果(a)

图9 单次总线完整性检查试验结果(b)

为了避免在总线完整性检查过程中因时序问题导致虚警故障,可以采用如下办法。

方法一:延长组合导航计算机软件运行周期或缩短CC总线运行周期。只要节点向总线上传数据的频率大于导航计算机获取数据包的频率,就可以避免虚警问题。但此方法引起的软件架构变动较大。

方法二:在现有的总线完整性检查过程中,CPU每一周期都读取数据包信息及其更新标志,并在读取之后对更新标志进行清零操作,而实际上,在执行系统检查过程中,无需对数据包信息进行处理,因此可以延迟获取数据包更新标志。具体方法为:在禁止端口后,将DPRAM中的数据读走,使得两片缓冲区域中的数据包更新标志均为0,同时只在数据包进行总线完整性检查当拍读取DPRAM中的总线数据。如此,假如总线线缆连接故障,那么总线数据包在禁止端口后就无法更新,总线完整性检查当拍读到的数据包更新标志为0,即可判断总线连接故障;如果总线连接完好,那么将DPRAM中的数据读走后,仍然会有新的数据包发送过来,新的数据包会将数据包更新标志重新置1,在总线完整性检查当拍读到数据包更新标志为1,判断总线连接完好。由于在总线完整性检查过程中,数据包只读取一次,虚警可以避免。

方法三:从仿真试验结果可以看出,连续两次读取同一片缓冲区的现象也呈现周期性变化,目前的检查方法只信任单次数据包更新标志的检查结果,难以避免偶然性,可以通过多次获取数据包更新标志的方式,在第一次检查结束后,延迟5拍第二次获取数据包更新标志,紧接着再延迟5拍,进行第三次数据包更新标志的获取,将多次检查结果进行综合,只要有一次检查到数据更新即可认为总线连接完好。

5 结 论

在进行总线完整性检查时,组合导航计算机与总线控制器时钟异步导致组合导航计算机软件相邻两周期读取DPRAM中同一片缓存是系统报出虚警的根本原因。由于总线控制器周期与组合导航计算机的理想运行周期相同,因此在设计初期,此类问题较难发现。本文对基于1394总线网络的分布式组合导航系统的时序建模与仿真工作对1394总线网络完整性检查以及异步系统的时序问题研究具有一定的借鉴意义。