AES加密算法的FPGA优化设计

2021-02-28湖南工学院电气与信息工程学院

湖南工学院电气与信息工程学院 陈 超

高级加密标准AES(Advanced Encryption Standard)算法由于其安全性高的优势而应用广泛,再结合FPGA的优势可实现加密速度快,开发周期短且可通用性强的AES加密算法。多轮加密的每一轮采用复用的方式以节省资源,且通过状态机控制加密过程。最后结合FPGA综合仿真,资源消耗为9643,最高工作频率为126.34MHz。

随着通信技术及计算机的发展,人们有越来越多的信息需要通过通信设备来传输与交换,用户对于数据传输的安全性越来越重视,因此需要对数据进行加密传输来保证数据的安全性。而AES以其速度快、设计简单、安全性高、易维护等优点在邮件加密、数字签名、文档加密中广泛应用。

AES算法是2001年由NIST(美国国家标准技术研究所)为取代DES而发布的新一代数据高级加密标准。AES-128算法的密钥比DES-56的密钥在破解的时间花费上强1021倍。如果加解密采用同样的密钥会导致降低安全性。为了保证安全性,设计加解密密钥可采用相关且不同的密钥,即把加密模式的密钥扩展模块的最后一轮子密钥作为解密模式密钥的初始密钥,这样就可以强化通信安全性,保密性以及出色的抗攻击性。

1 AES算法原理

1.1 AES的算法描述

AES算法是一种对称密码,且是属于其中的一种分组密码,其原理采用的是迭代分组密码算法,它由轮变换函数经过数次迭代变换而成。AES加密可用如下加密公式表示。

其中E表示加密函数,K表示密钥,P表示明文,C表示密文。

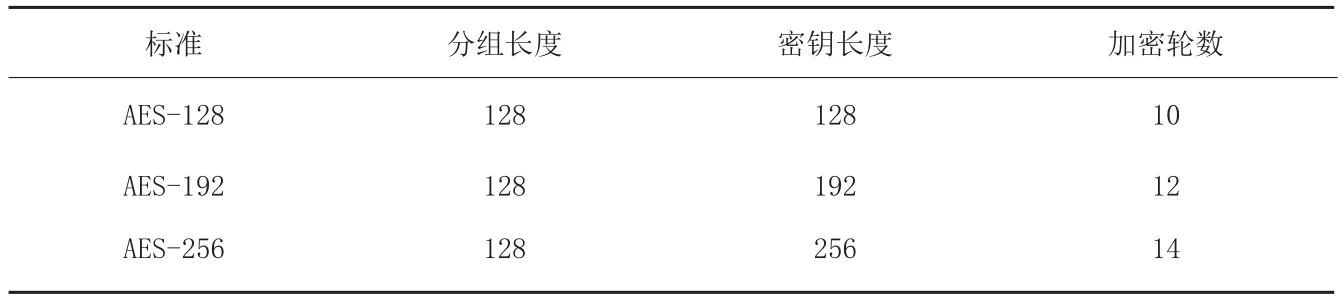

AES的密钥长度可分为128bit,192bit和256bit,而分组长度固定为128bit。除了轮数,这三种的加密过程相同。每种长度对应的变换轮数的关系如表1所示。

表1 AES算法的分组,密钥及轮数关系

1.2 AES的加密过程

把加密数据排列成以字节为单位元素的4×4状态矩阵,该矩阵中字节的排列顺序为从上到下,从左至右。加密的第一个步骤是待加密的明文与初始密钥异或(轮密钥加),然后根据表1的密钥长度进行对应的多轮变换。每一轮包含字节替换,行移位,列混淆,轮密钥加四个过程。其中最后一轮需跳过列混淆。

AES解密是加密的逆过程,文中不再详细阐述。图1所示是AES加解密过程的结构图。

图1 AES加解密执行过程

2 AES加密算法的硬件设计及模块分析

2.1 AES实现的整体结构

由于大部分应用采用AES-128,文中采用128bit来设计,其整体实现结构框图如图2所示,该设计的加密与解密是同一个模块,通过mode输入信号来控制加解密模式。该框架主要由加/解密模块(Encrypt/Decrypt)、密钥扩展模块(key_exp)、字节替换模块(s_box)组成。其中加/解密模块功能主要由状态机控制,完成与字节替换/逆替换模块的数据交互、行移位、列混淆运算、轮密钥加以及对密钥扩展模块的控制。设计中为了节省I/O资源,128bit数据和128bit初始密钥由32bit的data_in依次输入,并通过k_or_d信号来区分数据输入还是密钥输入。输入start信号为高表示输入有效。同样,输出端亦为128bit密文由32bit端口依次输出。加密数据流向为接收数据后由加/解密模块配合其他模块进行10轮迭代变换,最后一轮密钥异或输出即为密文。解密过程与其相同,把密文以相同的步骤作为数据输入,同时设置mode=0,输出即为明文。

图2 设计实现框图

2.2 密钥扩展模块

AES采用的是密码密钥,不能在每一轮都是中相同的密钥,需要根据初始密钥去扩展获得每一轮需要的密钥。十轮密钥扩展得到总长度为W*Nb(Nr+1),其中W为密钥矩阵每列的位数,Nb分组长度为4,Nr指加密轮数。矩阵的每一列密钥元素可用Wi表示,其中i的所在范围为0 ≤i<Nb(Nr+1)。扩展子密钥可由初始密钥生成。

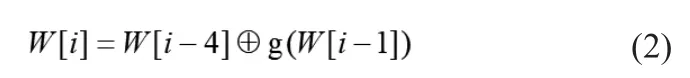

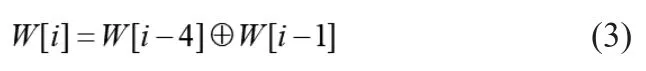

当i能被4整除:

当i不能被4整除:

其中:函数g()由三部分组成:字循环、字节替换和轮常量异或(函数g()可以增加密钥拓展中的非线性,并且破坏AES算法的对称性)。

(1)字循环:密钥W[i]中的4个字节循环左移一个字节。例如输入[a0,a1,a2,a3]变换后为[a1,a2,a3,a0]。

(2)字节替换:将第一步的结果使用S盒进行字节代换,与加密过程字节替换步骤相同。

(3)轮常量异或:将第二步的结果与轮常量Rcon[j]异或,j表示轮数。Rcon用查找表实现,轮计数器kcnt作为查找地址。

2.3 字节替换与行移位模块

字节替换是数据4×4状态矩阵中,每个字节元素的高四位为S盒的行地址,低四位为列地址,用寻址后的值替换状态矩阵的值。逆字节替换同理,只是需要查找逆S盒的行列地址即可。设计中采用查找表的方式进行字节替换与逆字节替换操作。以下为4×4状态矩阵的排列顺序。

行移位是4×4状态矩阵的行循环移位,第一行不变,第二行左移一个字节,第二行左移两个字节,第三行左移三个字节。逆行移位为行移位反向操作,即向右循环移位即可。

2.4 列混淆与轮密钥加模块

列混淆运算为位元变换,根据GF(28)有限域运算规则,即将状态矩阵左乘混淆矩阵,结果就是列混淆后的值。而逆列混淆运算就是状态矩阵左乘逆混淆矩阵。设计中的列混淆与逆列混淆采用函数的方法进行运算,一个时钟周期出结果。部分代码如下:

轮密钥加易于实现,只需状态矩阵与密钥矩阵相同的位置进行异或运算后,得到的就是下一轮迭代变换的起始状态矩阵。

3 AES算法的仿真与实现

3.1 AES算法仿真结果及分析

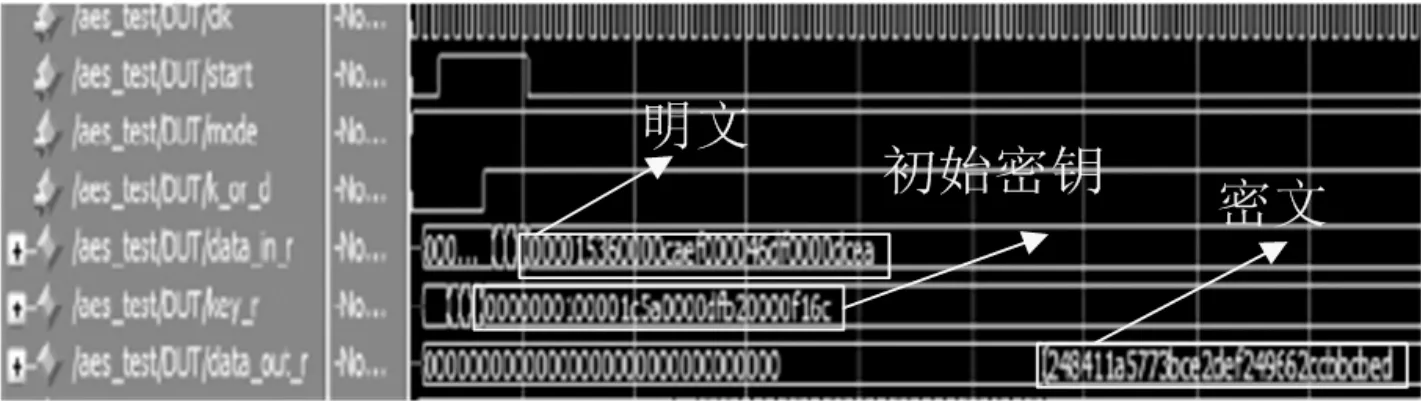

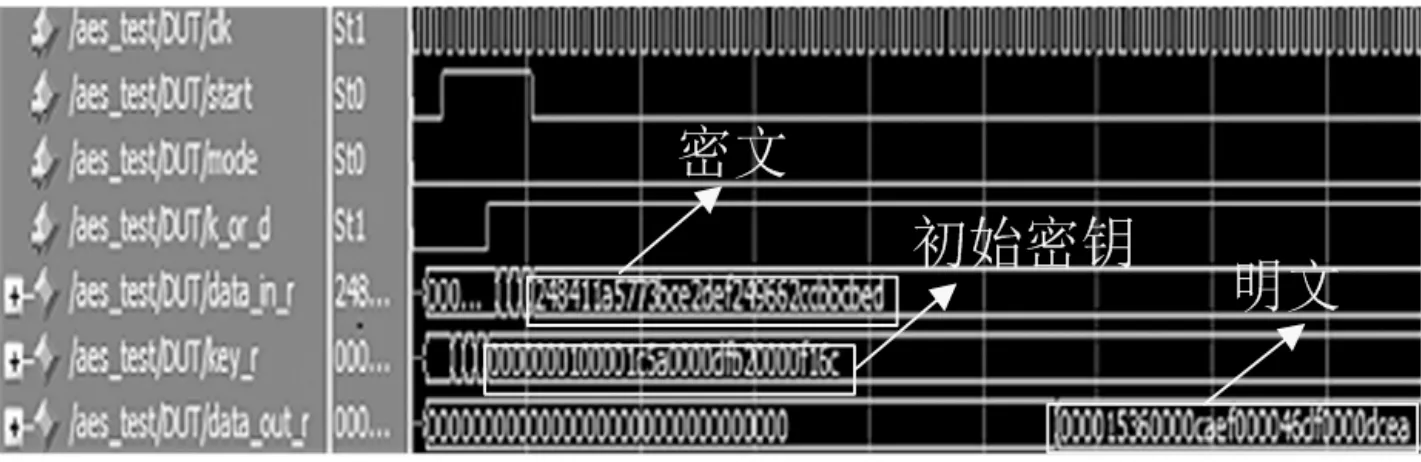

设计采用Verilog HDL对AES算法进行设计以及验证。在十轮迭代加密、解密运算后,得到的加密与解密结果分别如图3、图4所示。

图3 AES加密数据仿真

图4 AES解密数据仿真

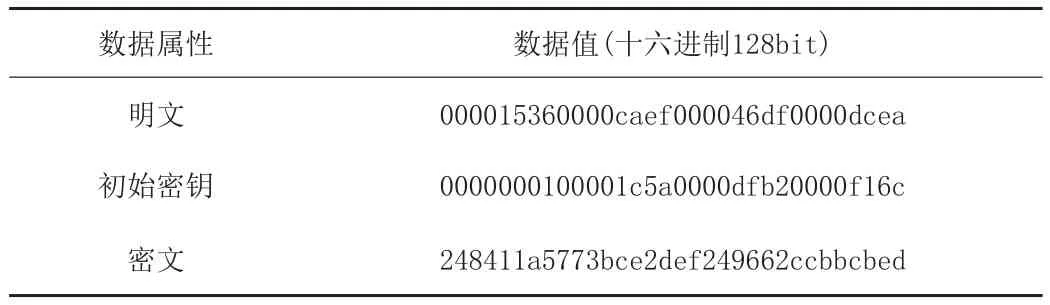

表2、表3分别对应图3、图4的加密和解密实例结果表。由实例数据测试结果可知,文中的AES算法设计在mode=1的加密模式下,输入表2中的明文以及密钥,可得到表2中的密文(如图3所示);然后用密文作为输入在mode=0的解密模式下,输入表3中的密文以及密钥,可得到表3中的明文(如图4所示)。实验表明解密后的明文与加密前的明文相同。同时测试也用了多组数据进行了设计验证,均证明了文中的设计可以对数据进行正确的加密得到密文,密文也可以反过来解密出明文。

表2 AES测试加密数据实例

表3 AES测试解密数据实例

3.2 性能分析

文中设计软件基于Quartus Ⅱ13.1,仿真软件为ModelSim 10.1d,芯片为Cyclone Ⅳ系列EP4CE10E22C8进行验证,最终设计综合出来可实现工作频率最高为126.34MHz,逻辑资源消耗为9643。再通过对比占用的逻辑单元数,可将中文设计与其他文献的方案做比较可得到表4,可说明本方案较其他方案相比,运行速度更快,吞吐量更高;但同时占用逻辑单元数在对比中处于适中位置,不占很大优势,这是用面积换取速度的结果导致。

表4 设计与其他文献方案对比

文中分析了AES算法的原理以及设计的实现方案,实现的关键在于状态机的控制;再通过划分各个模块来分析每个模块的实现方法;最后实例测试采用文中的方案而实现的设计模块以及设计的性能分析。结果表明该设计方案能满足设计要求。