基于Camera Link的高可靠性图像数据传输设计

2021-02-25甄国涌丁润琦张凯华

甄国涌,丁润琦,张凯华

(1.中北大学,山西太原 030051;2.电子测试技术国家重点实验室,山西太原 030051;3.仪器科学与动态测试教育部重点实验室,山西太原 030051)

0 引言

伴随着高帧频、高像素的工业相机应用越来越广泛,对图像数据的传输速率以及可靠性提出了更高的要求[1]。目前图像数据传输主要采用IEEE-1394、LVDS以及Camera Link等标准接口协议。Camera Link接口采用串并结合的传输方式相对于其他协议具有更高的传输速度和更强的抗干扰性能,并且输出总线较少,便于设计开发,Camera Link接口协议已经逐渐成为数字图像传输设计中的首选接口协议,因此选用Camera Link作为此次设计的图像传输接口[2]。在FPGA逻辑设计中通过对Camera Link接口时序进行优化设计以及采用CRC+ECC双校验结合的方法进一步提高了数据传输的可靠性。

1 整体设计方案

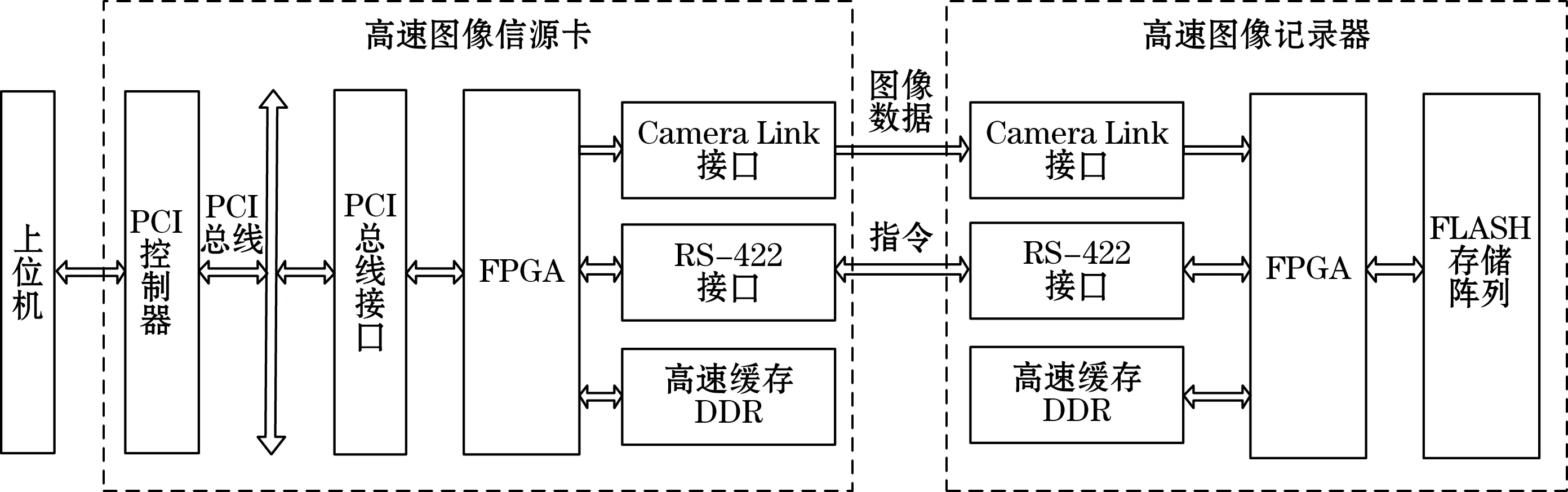

本文设计的图像传输系统主要由高速图像信源卡、高速图像记录器以及上位机组成,如图1所示。其中高速图像信源卡的主要功能为模拟工业相机对图像数据传输和指令互传准确性进行测试。高速图像记录器作为图像数据接收端用于在恶劣测试环境下接收并存储图像数据。

系统的工作流程为FPGA首先收到由上位机发送的图像加载命令,并准备接收PCI总线上的数据,FPGA将接收的数据写入DDR中,当DDR中缓存了完整一帧图像后,FPGA将DDR中的数据通过Camera Link接口将LVCMOS/LVTTL信号转换为LVDS信号发送到图像记录器。图像记录器接收到图像数据后,先将数据缓存在DDR中,当接收了完整一帧图像后,FPGA将缓存读出,并写入到FLASH存储阵列中。RS-422接口主要完成设备之间的指令相互传输。

图1 整体设计框图

2 Camera Link接口设计

2.1 Camera Link接口协议

Camera Link接口标准协议包括用于命令传输的串行通信信号、用于采集卡对相机控制的控制信号、电源信号以及图像数据信号。其中图像数据信号由28位信号组成,包括24位数据信号和4位数据有效信号。数据有效信号包括帧同步FVAL、行同步LVAL、数据有效DVAL以及保留信号SPARE[3]。

2.2 Camera Link接口电路设计

在此次设计中图像发送端选用Camera Link接口专用驱动芯片DS90CR285,在接收端选用DS90CR286作为接收芯片。该芯片支持的最大像素时钟为66 MHz,图像数据最大传输速度为1.848 Gbit/s,且该芯片实现Camera Link接口通讯较简便,电路原理框图如图2所示[4]。

图2 Camera Link接口电路原理框图

3 传输逻辑可靠性设计

3.1 Camera Link接口时序优化设计

为保证使用Camera Link接口发送图像数据时数据传输的准确性,需要按照协议对接口同步信号严格控制[5]。在图像数据开始发送时需先将帧同步信号置为‘1’;之后在经过10个时钟后将行同步信号置为‘1’,发送一行数据,当一行数据发送完成后需等待10个时钟周期后才可发送下一行数据。当帧同步、行同步和数据有效信号同时有效时,图像依次发送。发送完成后FVAL在10个时钟周期后置低,结束数据发送[6]。图像数据发送时序仿真如图3所示。

图3 图像数据发送时序仿真图

为保证图像数据的传输时序满足驱动器DS90CR285的建立/保持时间,需对Camera Link接口时序进行优化设计。Camera Link的驱动器和接收器在进行图像数据传输前需保证两端的锁相环同步,为保证两端快速同步,在上电复位完成后,驱动器不断地向接收器发送无效递增数,接收器根据不断变化的数据流快速对时钟解码,达到锁相环同步的目的[7]。

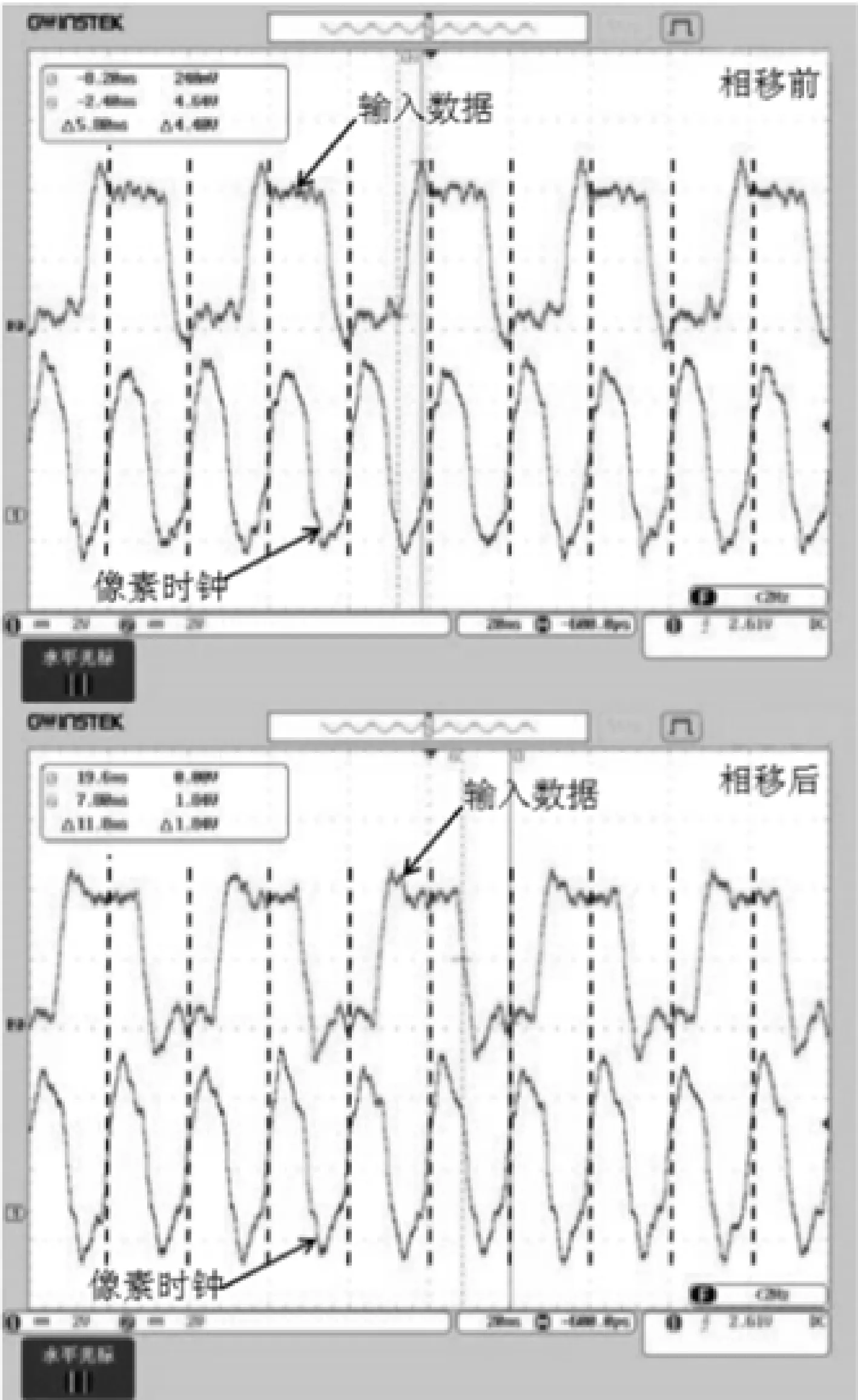

驱动器要求数据的建立时间不少于2.5 ns,为确保数据稳定达到驱动芯片的建立时间,使用FPGA中的DCM模块对图像数据进行移相操作,为保证驱动器在时钟下降沿采样时数据已经达到稳定状态,将时钟相移90°。由于采用的是50 MHz的采样时钟,则采样时间延迟5 ns,满足数据的建立时间。使用示波器测量输入的并行数据最低位与像素时钟的波形如图4所示。

图4 相移前与相移后波形图

3.2 双校验逻辑实现

双校验逻辑实现流程为:Camera Link数据的发送端和接收端在发送和接收数据时都以1 024字节为一包数据。当发送端将一包数据发送完成后紧接着发送这一包数据的双校验码,接收端在接收数据的同时计算该包数据的双校验码,在接收端接收完成一包数据后首先判断发送端发送的CRC值与接收端接收的CRC值是否一致。如果CRC校验值一致表示数据正确,准备接收下一包数据;若CRC校验值不一致,则通过对该数据包的ECC校验码进行判断并计算出该数据包中数据出错的位置。若ECC判断错误位数较少可纠正,则对该出错数据取反纠正;若错误位数较多,不可纠正,则数据接收端向发送端发送重传请求。

3.2.1 CRC校验逻辑实现

数据以1 024字节为一包,为保持较高的检错率在逻辑设计时选用CRC16校验方法。对于数据量较多的运算,传统的逐位串行运算校验速率较低,耗费时钟周期较长。而通过使用查表法CRC运算可并行处理接收的数据,效率较高,适合大量数据校验[8]。在传输过程中发送端和接收端都进行CRC校验,若接收端和发送端的校验结果不一致,则表明在数据传输过程中出现误码或丢数现象,反之,则说明数据在传输过程中无错误。

3.2.2 ECC校验逻辑实现

ECC校验是由奇偶校验方法发展而来,ECC校验是将数据块看做矩阵,通过计算行、列校验码来对数据进行检验以及纠错。ECC校验方法可以对一位错误纠错,可以检验出两位错误但是无法纠正[9]。ECC校验示意图如图5所示。

图5 ECC校验示意图

ECC校验过程为:首先将需发送的数据块中的数据字按位异或,将得到的异或结果与P1、P1′、P2、P2′等异或,得到列校验码。每次发送完成数据字后便将该字与P16、P16′、P32、P32′等异或,得到行校验码。当数据块中的数据字发送完成后,计算的结果即为该数据块的ECC校验值。将信号发送端和接收端计算的ECC校验码根据奇偶位可分为4组12位校验码。

ECC_tx_odd<= P2048&P1024&……P8&P4&P2&P1

ECC_tx_even<= P2048′&P1024′&……P8′&P4′&P2′&P1′

ECC_rx_odd<= P2048&P1024&……P8&P4&P2&P1

ECC_rx_even<= P2048′&P1024′&……P8′&P4′&P2′&P1′

ECC_result<= ECC_tx_odd⊕ECC_rx_odd⊕ECC_tx_even⊕ECC_rx_even

其中ECC_result为数据的ECC校验值。若数据的ECC校验结果全为‘0’则表示数据正确,若结果全为‘1’表示数据中只有1位错误,若为其他值表示数据中存在多位错误。ECC纠错方法:ECC_addr<= ECC_tx_odd⊕ECC_rx_odd,得到的结果中高8位表示错误的字地址,低4位表示出错的位地址。通过地址找到出错的位置取反即可纠正。

3.2.3 发送端逻辑实现

Camera Link发送端采用乒乓操作的方式进行数据发送,发送端首先发送RAM1中的数据,当数据发送完成后紧接着发送2个ECC校验值和1个CRC校验值。当RAM1中的数据以及双校验码发送完成后,发送端紧接着向RAM2缓存下一包数据并等待接收端的重传请求,如果无重传请求,数据发送端将RAM2中缓存的数据读出并发送。若发送收到重传请求,则再次将RAM1中的数据读出并发送。为保障数据的传输效率,发送端在第2次发送完成后,不再等待重传请求直接开始发送下一包数据,发送端工作流程图如图6所示[10]。

图6 发送端工作流程图

3.2.4 接收端逻辑实现

数据接收端将收到的图像数据写入RAM中,并计算这一包数据的CRC和ECC校验值。如果CRC校验值一致表明接收到的数据包正确,不需要纠正或重传,等待接收下一包数据;若不一致则根据ECC校验值判断出错的位数,如果出错的位数为一位,根据ECC校验结果计算出错的位置并进行取反纠错,否则请求重传。接收端工作流程图如图7所示。

图7 接收端工作流程图

4 试验验证及分析

为验证图像传输的可靠性,使用图像信源卡、图像记录器以及上位机构成一个闭环测试系统。使用地面测试电缆,连接图像信源卡和图像记录器的Camera Link接口,使用上位机软件向信源卡发送图像传输指令,图像传输完成后回读图像记录器中的FLASH数据。

在传输距离为5 m的要求下,对该设计进行测试。通过信源卡向图像记录器发送16 bit的递增数信号,图像记录器接收的图像如图8所示,可看出像素点无突变。

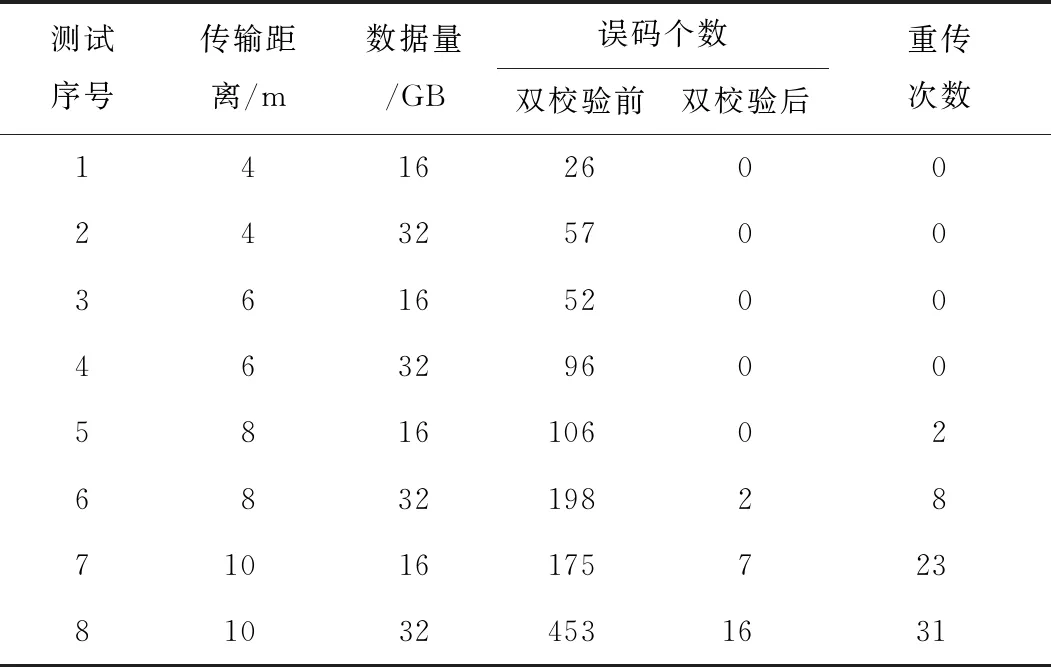

在不同传输距离和不同数据量下对图像数据传输可靠性进行测试,测试结果如表1所示。

根据测试结果可知,在不使用双校验逻辑的情况下数据误码较多,且随着传输距离和数量的增加误码也增加。在加入双校验逻辑后,在短距离、大数据量的情况下都不会出现误码,在较长距离的情况下会有少数的误码,误码率低于一百亿分之一。

图8 16 bit灰度图像

表1 误码统计表

5 结束语

针对图像数据在高速传输时可靠性较低的问题,设计了基于Camera Link的高可靠性图像数据传输系统。通过对接口时序进行优化设计以及使用CRC校验与ECC校验结合的双校验方法,提高了Camera Link接口在传输图像数据的可靠性。经试验验证,加入双校验逻辑后,误码率低于一百亿分之一,图像数据传输可靠性显著提升。参考文献:

[1] 杜文略,李红薇,高越.水下试验图像数据采集存储系统的设计与实现[J].电子器件,2019,42(3):733-739.

[2] 隋延林,何斌,张立国,等.基于FPGA的超高速Camera Link图像传输[J].吉林大学学报(工学版),2017,47(5):1634-1643.

[3] 邱扬刚,邱琦,赵民伟,等.基于Camera Link的高速图像采集技术研究与应用[J].计算机测量与控制,2018,26(4):239-242.

[4] 魏淑稳.基于FPGA的Camera Link图像数据采集装置的研究与实现[D].太原:中北大学,2019.

[5] 张维达,崔明,张甫恺.基于异步FIFO的Camera Link数字图像光纤传输技术[J].仪表技术与传感器,2016(7):47-50.

[6] 汝兴海.图像数据高速传输和数据存储的关键技术研究与实现[D].太原:中北大学,2016.

[7] 刘源,李庆,梁艳菊.基于FPGA的红外目标自动检测系统[J].红外技术,2019,41(6):521-526.

[8] 李辉景,王淑琴,任勇峰,等.基于CRC校验的高速长线LVDS传输设计[J].电子器件,2015,38(6):1346-1351.

[9] 朱金瑞,王代华,苏尚恩,等.存储式弹载数据记录仪存储可靠性技术研究[J].兵器装备工程学报,2019,40(1):159-162.

[10] 范君健,吴国东,王志军,等.基于FPGA的高精度弹载压力数据采集系统[J].兵器装备工程学报,2017,38(9):102-107.