低噪声高分辨IC测试系统设计

2021-02-16齐学红汪海波

齐学红 汪海波

江苏电子信息职业学院,江苏淮安223003

0 前言

IC测试系统[1]是保证集成电路稳定可靠的关键。IC测试分为晶圆测试、芯片测试和封装测试。IC测试仪由系统控制器、通信桥、测试头3部分组成。

DAC芯片测试仪器的性能高于DAC,方可在测量中忽略仪器的失真和噪声。随着芯片制造工艺的提升,DAC芯片的分辨率和转换速率越来越高。DAC的测试要求具有更高分辨率的ADC采集系统。ADC分辨率过高将导致采样率在几M以下,无法对高速的DAC进行测试;如果ADC的采样率较高而分辨率不足,则只能测试更低分辨率的DAC芯片。16位恰好兼顾采集速度和采集精度。鉴于此,设计利用现有的ADC芯片构建低噪声高分辨率采集电路,采集被测DAC产生的正弦波、方波、锯齿波和直流信号等,用于对DAC的性能进行评估。

1 系统测试原理及要求

低噪声信号调理电路获取被测模拟信号,处于系统的前端,对信号带宽及动态范围等具有决定作用。对大信号进行衰减,小信号进行放大,采用固定放大和可调AGC组成级联电路,获得幅度接近ADC采样信号满量程范围;设计偏移调节电路,将输入的共模信号调整到后级电路的中间电平并校正信号调理过程中的偏移,避免信号超过器件允许范围;设计选取精密的元件和优化电路,减少引入噪声,实现高信噪比;设计驱动电路,实现同时驱动4个ADC电路,满足系统时间交替采样的需要。

信号输入采样电路和ADC电路,由SYNC为多路ADC提供同步时钟,获得4路并行交替系统需要的低抖动、多相位采样时钟;ADC转换信号输入FPGA处理器实现信号的存储和处理,FPGA输出信号通过ARM和接口电路,由以太网线和LAN线与上位机PC进行数据交换。系统测试方案如图1所示。

2 系统方案设计

系统主要功能模块包括低噪声信号调理通道、时钟产生电路、高速数据采集单元、数据存储模块、以太网接口电路以及电源模块等,通过以太网与上位机进行数据通信。总体方案如图2所示。

3 系统模块设计

3.1 信号调理电路设计

信号调理模块完成信号的衰减、阻抗变换、放大、偏移、驱动和滤波等功能,满足ADC输入电压要求,同时实现高信噪比[2-4]。

3.1.1 衰减电路设计[5]

采集系统输入阻抗50/1 MΩ可选,输入电压5 VPP。ADC的满量程输入为2.5 VPP,需要幅度衰减。有源衰减因外接电源限制其输入信号幅度;无源衰减电路输入功率小,难以满足设计要求,故设计选择分立元件组成的50/1 MΩ衰减电路。

波形发生器产生波形,经50/1 MΩ的选择开关电路,1 MΩ电路因分布电容和引线电感影响,设计补偿分压电路,电路设计10倍衰减,无源衰减网络稳态响应由R2、R3构成的电阻分压网络确定,R1、R4、C1~C3为衰减网络高频补偿电路,其中,C2为可调电容,便于补偿调整。50 Ω阻抗衰减电路采用π型,由R5、R6、R7组成。衰减电路设计如图3所示。

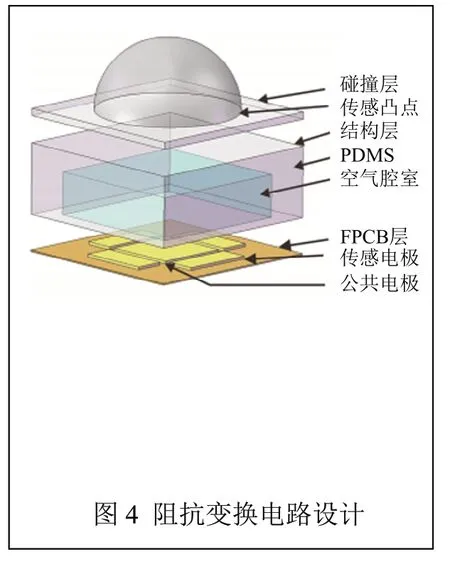

3.1.2 阻抗变换电路设计

50 Ω和1 MΩ输入因小信号过于敏感导致噪声信号随之进入,高输入阻抗使前级电路对后级驱动能力降低,无法驱动小阻抗负载。针对此设计以运放OPA659为核心,R8、R9、C4~C7元件组成射随电路,提高输入阻抗,降低输出阻抗,实现对输入信号的缓冲和阻抗变换。阻抗变换电路设计如图4所示。

3.1.3 增益电路设计[6]

(1)固定增益电路设计

采集系统信号大时需要衰减,而信号小时则需要放大以达到ADC满量程。设计采用一个固定增益电路和一个可调增益电路达到此功能。固定增益设计为10倍,选取运放LMH6703、R10~R12组成同相放大电路。增益电路设计如图5所示。

(2)可调增益电路设计

设计以VCA824为压控增益放大器,牺牲增益获取带宽,设计放大倍数1~10可调,DAC电压经LM431稳压后与-5 V电源产生增益控制信号,控制信号范围-1~+1 V。增益电路设计如图5所示。

3.1.4 偏移电路设计[7]

信号经过衰减、放大等多级电路,元件固有的温票、零票和失真等使信号中心电平变化,可能超出ADC允许范围,设计数模转换芯片LTC2600产生直流电压作为偏移调节信号,由AD8009运放组成减法电路,实现信号偏移,满足ADC输入电压要求。

3.1.5 ADC驱动电路设计

ADC驱动电路有变压器耦合、射频巴伦耦合和全差分运放等形式,设计采用全差分运放构成ADC驱动电路,由高速放大器LMH6553芯片构成ADC驱动电路。电路具有增益可调、前后级隔离、ADC阻抗匹配等优点。

3.1.6 抗混叠滤波电路设计

滤波电路能有效滤除进入ADC电路的噪声,避免造成带内混叠,降低动态性能。设计采用典型的π型RC滤波电路,通过仿真和实际调试,设计通频带在150 MHz,满足设计要求。

3.2 时钟电路设计

ADC量化模拟信号需要稳定的时钟信号,否则会出现采样不均、波形不光滑等问题,影响时钟稳定的因素主要是时钟抖动。

3.2.1 时钟消抖电路设计[8-9]

时钟抖动主要有固定抖动和随机抖动,前者由可识别信号产生,后者则往往由多种信号叠加而成。为提高ADC性能,采用高稳定性的、具有温度补偿的晶振SiT5155及双锁相环芯片LMK04803构成消抖电路,采用差分电路抑制串扰。时钟消抖电路设计如图6所示。

3.2.2 时钟同步设计

系统LMK04803产生4路ADC采样时钟,通过SYNC(高电平有效)同步;ADC内部具有时钟分频器,使输入时钟频率变为最高采样频率的4倍,设计第一个SYNC信号上升沿有效,4个ADC共有4个SYNC同步信号,4路信号同时达到ADC引脚,实现ADC采样时钟输入同步;ADC的16位并行数据与时钟DCO同步,FPGA内部采用上升沿同步逻辑,将时钟上升沿设置在数据的中心位置,达到ADC数据采样同步,ADC同步信号与采样时钟时序关系如图7所示。

3.3 接口电路设计[10]

采集系统接口包括模拟信号系统存储和数字通信接口。数字通信接口是指FPGA、ARM、上位机及以太网之间的接口电路,如图8所示。设计采用8位地址总线、16位宽数据总线、读使能、写使能、片选和地址线低8位,实现FPGA与ARM的通讯连接;系统ARM采用STM32407芯片实现以太网高速数据收发,选用高性能DP83848作为以太网收发器,实现ARM和以太网高速通讯,以太网通过LAN线与上位机通讯。

4 FPGA控制逻辑设计[11]

系统利用FPGA高速稳定特性,将高速采集信号进行存储与处理,并对外设计进行控制,FPGA与ARM之间通信控制通过软件判断实现,控制流程如图9所示。

数据存储是将两路数据分离再存储入大容量设备,系统上电后进入IDLE状态,等待DDR3初始化结束,进入WAIT等待状态,当接收到上位机的存储和读取命令时,分别进行WRITE和READ操作。DDR3控制状态转移如图10所示。

5 系统误差校准

误差分析校正方法诸如正弦拟合、自适应、滤波、重构、插值等,系统采用偏移误差校准、增益误差校准、时间误差校准的流程[12-13]。

5.1 偏移误差

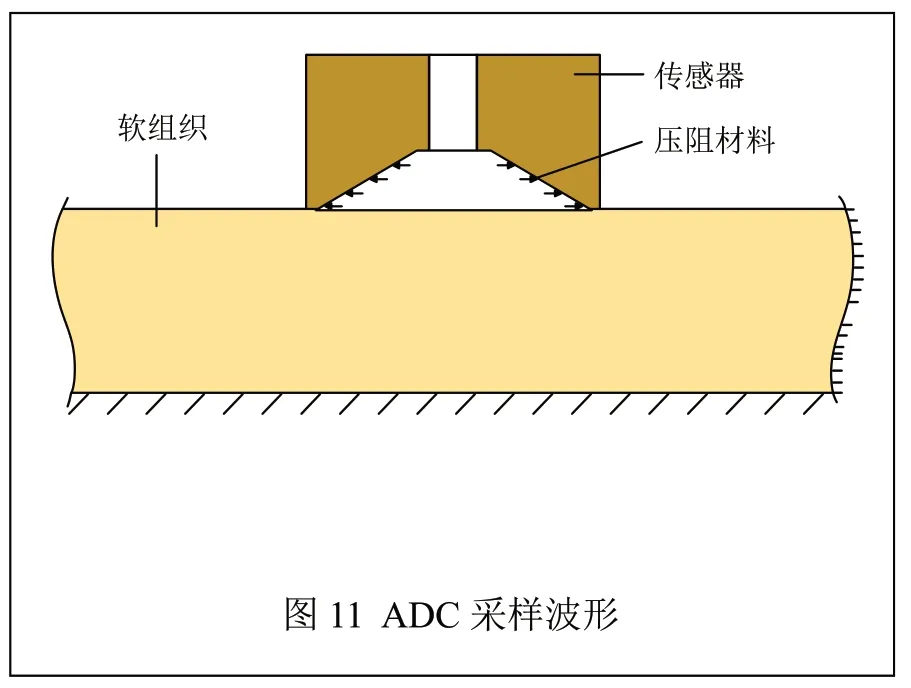

将输入信号对地短接,测量ADC数据输出即得到各自的偏移,理论值为32,768,实际受布线等影响会有偏差。上位机对每个ADC偏移误差独自处理后采集波形如图11所示。偏移误差的采样结果由采样值与偏移值之差得到,如表1所示。

表1 偏移误差统计

5.2 增益误差和时间误差

输入模拟角频率为Ω0的标准正弦信号,ADC采集信号经傅里叶变换,利用MATLAB对采集数据做FFT变换,得到各自增益系数和信号相位,再分别计算增益误差和时间误差。增益误差和偏移误差乘以采样数据得到校正;时间误差通过时间延迟电路进行修正实现。

6 系统测试

系统性能指标包括分辨率、采样率、带宽、信噪比等,分别测试如下:

6.1 分辨率测试

高精度信号源(SPF05A)产生100 kHz、幅度1.25 V、无偏移的锯齿波,由采集板采集数据,通过LAN线传输给上位机,PC上位机显示采集数据。信号分辨率测试连接电路如图12所示。

上位机界面获取测试结果如图13所示。图中,数据表采样数据最大值65,525,由此可见,接近16位,满足设计要求。

6.2 采样率测试

如图12连接采集板,信号源输出VPP=500 mV,T=1 µs的方波,经过PC统计处理,选取其中两个靠近上升沿之间的采样点,得到N=1,000。经测试表明,采样率fs=109,满足设计要求,PC波形显示如图14所示。

6.3 带宽测试

如图12,信号源输出f= 1 MHz,VPP=500 MV,信号输出阻抗为50 Ω,保持信号幅度不变,选取代表性的测试点,测量幅度值如表2所示。由表中数据可见,带宽在170 MHz内,信号幅度接近-3 dB,满足设计要求。

表2 带块测试数据统计

6.4 信噪比测试

如图12连接电路,信号源输出f=1 MHz,VPP=1.125(-1 dBFS),获取信噪比SNR。数据表明,信号幅值在-1,dBFS处的信号VPP=1.06,经过校准和处理后,得到信噪比SNR=-62.9 dB,采集波形及频谱如图15所示,基本满足要求。

7 结束语

低噪声、高分辨率IC测试仪信号采集电路设计采用了低噪声信号调理电路,降低了噪声干扰,提高了信噪比。设计了可调相位延迟电路消除时钟抖动;设计了接口电路实现FPGA逻辑控制;分析了偏移误差、增益误差和时间误差。经测定,IC采集系统,分辨率达到65,525(接近16位)、采样率109、波形信噪比62.9 dB,达到设计要求。