面向物联网应用的SoC安全检查架构设计

2021-02-05闫华钰

闫华钰,陈 岚,佟 鑫,李 莹

(1.中国科学院微电子研究所,北京 100029;2.中国科学院大学,北京 100049)

0 概述

物联网技术的不断发展可实现自动驾驶、智能家居和可穿戴等设备的互联,为人们提供更加便捷的生活方式。麦肯锡2019年度研究报告指出,2015年有250亿部联网设备,预计到2025年将超过500亿部[1]。物联网设备通常由一个或多个SoC组成,一般包含系统感知和用户隐私等关键信息。近年来,以RISC-V为代表的开源硬件的提出突破了传统硬件架构授权的限制,进一步促进了物联网设备的创新和发展,但由于开源硬件缺少安全保护机制,使其硬件安全隐患更为突出,如硬件木马可对加密核进行攻击以获取密钥,或对外设接口进行攻击,造成外设接口的功能被破坏[2],尤其是利用运行时条件触发的系统级攻击,很难通过传统测试方法进行检测和防御。

目前,虽然已有一些电路硬件安全检测方法,但其主要集中在设计制造过程中[3-4],缺乏有效的电路运行时安全检查方法。片上在线安全检查是指在芯片设计时加入安全检查功能,使其能够在部署实现后对芯片进行运行时安全检查,并在发现安全问题时及时响应,这对于SoC全周期安全具有重要意义。本文面向物联网设备应用,针对片上资源和系统级攻击的特点,设计系统级安全策略及可迁移、可扩展和内容可配置的检查架构,并基于RISC-V的SoC环境验证所设计检查架构的有效性。

1 SoC安全检查方法

传统运行时检测方法包括内建自测试方法和信息流追踪方法。内建自测试方法通过扫描链将测试向量传输至检查模块验证模块功能[5],如将AES中的关键路径配置为环形振荡器,通过检测振荡频率检查是否有硬件木马植入[6]。该方法需对逻辑完全了解,且存在测试向量状态空间爆炸等问题。信息流追踪方法通过追踪检查功耗、延时、电流等特定信息通路中是否存在安全问题,如利用采集电路中的电流信息[7]与黄金电路边界作对比以区分异常电路,但该方法增加了大量的额外逻辑开销和延迟开销,并且上述方法均不能实现检查结构的可扩展及内容的可配置,一旦部署就不可更改。

BASAK等人提出一种采用形式化验证方法检测硬件威胁的SoC安全架构,可在不了解电路内部逻辑的情况下进行安全检查[8]。该架构由策略引擎和包装器组成,策略引擎执行安全策略,根据包装器报告的行为对IP进行检查。最初的策略引擎设计采用微处理器,之后为降低资源开销将策略引擎以状态机的形式实现,策略引擎基于FPGA,这保证了策略更新的需求[9]。但该架构未与应用场景相结合,且其设计的架构并非专门针对系统级检查,也没有关于策略可配置性的描述。本文设计以此为启发,对系统级安全策略进行深入研究。

2 系统级安全策略

在物联网应用中,系统芯片经常需要对关键信息进行加密传输,因此保护关键信息在生成和传输过程中的安全性至关重要。结合物联网应用场景,对SoC资源进行分类分析,并研究相应的攻击与系统级安全策略,进而设计片上安全检查架构和流程。

2.1 攻击分类

保护芯片关键信息的难点在于攻击者有多种攻击方式,根据芯片关键信息的获取方式和难易程度,将攻击分为以下6类:

1)普通恶意软件攻击:主要包括缓冲区溢出攻击[10]、代码注入攻击、BIOS感染攻击和面向返回的编程攻击等,在应用软件层面实施攻击,获取或破坏关键信息。

2)系统恶意软件攻击:主要包含利用系统漏洞进行攻击和系统本身执行恶意行为,在系统软件层面实施攻击,获取或破坏关键信息。

3)侧信道攻击:利用侧信道信息推测机密信息,例如差分功耗分析攻击[11]、差分电磁分析攻击[12]和时间攻击。

4)普通硬件攻击:利用设备的调试端口或外设端口进行攻击[13],从而获取机密信息,破坏系统功能,对设备造成破坏。

5)逆向工程:主要包括芯片级反向工程和IP核功能重构,攻击者利用逆向手段获取机密信息、破坏电路功能和注入恶意功能等。

6)恶意硬件注入攻击:在电路中植入恶意的硬件电路或固件代码,达到破坏原始电路功能、降低性能、泄露机密信息或造成拒绝服务等目的[14],主要包括硬件木马攻击、固件恶意代码攻击和硬件后门攻击等,其中以硬件木马攻击为主。

本文主要研究对于恶意硬件注入攻击的检查策略和检查架构。

2.2 安全策略

安全策略根据CIA原则可分为机密性、完整性和可用性策略[15]。根据对恶意硬件注入攻击的详细分析,相应的系统级策略类型可分为访问控制、信息流、生存约束、时效约束和通信策略,下面分类列举出目前已有的系统级安全策略:

1)访问控制类:在启动期间,任何IP都不能访问加密引擎的内部寄存器,该策略保护加密引擎在系统启动期间的机密数据不被泄露,属于机密性策略;当CPU处于高安全模式时,I/O设备无法更改受保护的内存数据,该策略保护内存数据不被篡改,属于完整性策略。

2)信息流类:在系统运行时,除加密引擎外,其他IP不能访问存储密钥种子的固件。该策略保护密钥种子不被泄露,属于机密性策略。

3)生存约束类:加密引擎在使用过程中不能出现功能完整性破坏。该策略保护加密引擎的功能正确,不被破坏,属于完整性策略。

4)时效约束类:IP上的固件经过更新,证书需要重新认证。该策略保护更新后的IP固件得到认证,属于可用性策略。

5)通信类:从IP A到IP B传输的私密信息不能被第三方IP访问。该策略保护数据在不同IP间传输的安全,属于机密性策略。

3 SoC安全检查架构设计

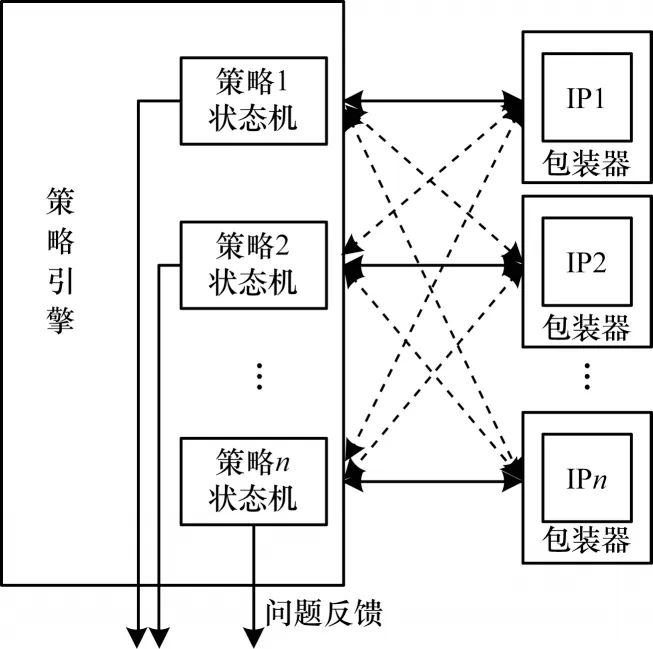

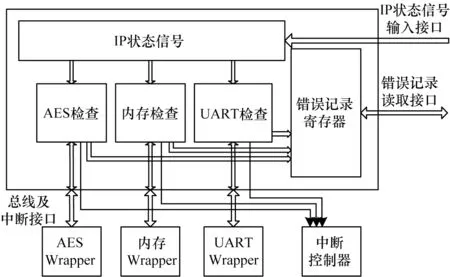

如图1所示,本文设计的系统级策略检查架构包括策略引擎和包装器,策略引擎和包装器采用轻量级设计且可配置和升级。策略检查架构不依赖于SoC的原有架构,采用通用性设计,方便迁移到其他系统中。

图1 策略检查架构示意图Fig.1 Schematic diagram of the policy check architecture

3.1 策略引擎

策略引擎是执行安全策略的核心,以状态机的形式进行安全策略检查,并根据包装器提供的信号判断待检查模块的状态,当条件允许时进行安全检查,并反馈被检查模块是否存在安全问题。策略引擎内的策略状态机根据需要进行配置,可在FPGA等可编程硬件上实现以满足更新需求。

3.2 包装器

包装器包裹在IP模块的外围,将IP的状态信息传递给策略引擎。包装器根据策略引擎的检查状态,灵活地选择将IP的接口分配给系统总线或者策略引擎检查总线,协助策略引擎实现对IP模块的检查。

4 验证系统设计

4.1 实验SoC搭建

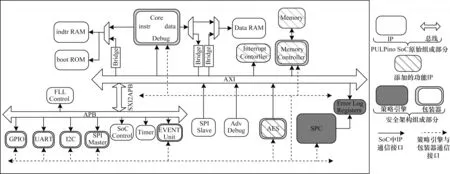

为验证本文设计架构的可行性,在PULPino系统[16]中嵌入检查架构。PULPino是一款设计精简的RISC-V[17]架构开源SoC平台。首先根据验证需要,在PULPino系统中添加AES、内存和AXI中断控制器3个功能IP,形成可用于IoT感知设备的SoC。图2中白色模块为PULPino SoC原始组成部分,斜对角线模块为添加的功能IP,深灰色的SPC模块即为策略引擎,各个IP上包裹的浅灰色模块即为包装器,它们之间通过单独的连线连接。当SPC检查出错误发生时,会将相应的错误代码写入错误寄存器并发送中断信号。CPU通过执行中断程序读取错误寄存器中的值并将错误代码输出。

图2 在PULPino SoC上的策略检查架构Fig.2 Policy check architecture on the PULPino SoC

4.2 面向物联网应用的安全策略检查流程

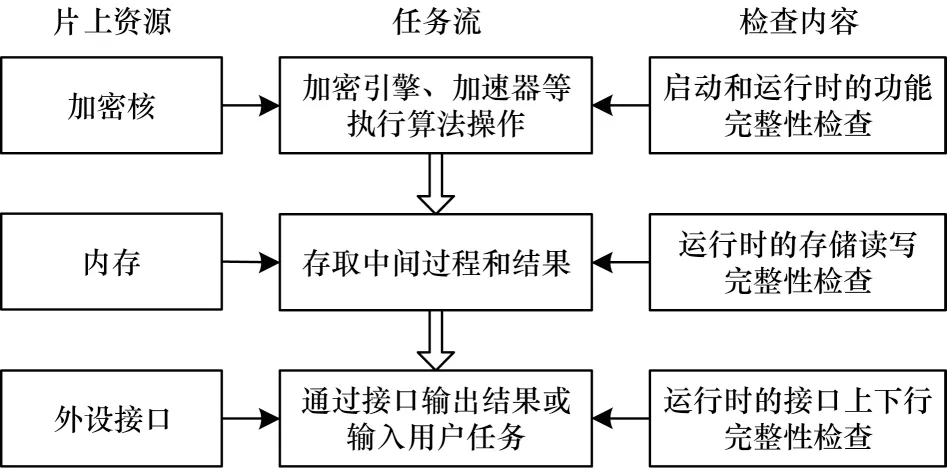

在SoC上的资源主要分为IP核、存储和接口,系统在执行任务时需要各类资源之间相互配合,因此对SoC进行片上安全检查就是对片上的资源进行安全检查。如图3所示,在物联网应用中典型场景为感知设备对采集数据进行加密后传输,下面针对该过程分析SoC中可能存在的系统级攻击和配置执行的安全策略。

在SoC中对数据进行加密传输需加密核、内存和外设接口这3类资源配合完成。若在这些资源中存在硬件木马,将其在运行时触发激活后对数据进行篡改,则将破坏整个任务流,甚至某些特定环节木马可修改特定位置数据,最终破解加密信息。因此,在物联网应用场景中的安全要素为加密后的采集数据,需对该任务流中涉及该要素的加密核、内存和外设接口进行相关安全检查。

图3 安全策略、系统资源和任务流的关系Fig.3 Relationship between security policies,system resources and task flows

4.2.1 硬件木马设计

由于现有Trust-Hub等硬件木马基准库中没有适用的运行时硬件木马基准电路,因此参考文献[2,18]中的高隐蔽性木马结构,并添加运行时触发条件,设计验证实验中的攻击模型。所设计的硬件木马由触发电路和负载组成,在运行时通过特定的数据条件触发,激活后破坏电路的正常功能。

1)AES硬件木马。触发电路为升降计数器[2],在AES中进行特定模式的计算,并且当输入的明文长度大于所设置的阈值时开始计数,当不满足条件木马计数器时清零计数器。在计数到阈值后,使能木马负载,同时清零计数器。木马负载是位于AES轮加密单元中的异或门,当木马激活后,控制异或门翻转特定位置的加密结果。

2)内存硬件木马。触发电路为条件计数器,当输入内存的数据同时满足地址触发条件和数据触发条件时,计数器开始计数[18]。在计数到阈值后,使能木马负载,同时清零计数器。木马负载位于内存写入电路,由篡改电路和选择器组成,当木马激活后,选择被篡改的数据存入内存。

3)UART硬件木马。触发电路为条件计数器,当UART接收到来自总线的数据是输出数据并且满足数据条件时,计数器开始计数。在计数到阈值后,使能木马负载,同时清零计数器。木马负载位于UART输出缓存写入电路,由篡改电路和选择器组成,当木马激活后,选择被篡改的数据存入输出缓存。

本文设计的AES、内存和UART中的硬件木马均为运行时触发木马,但3种木马触发的数据条件不同,木马负载根据各模块的特点,作用的位置不同。

4.2.2 安全策略检查流程

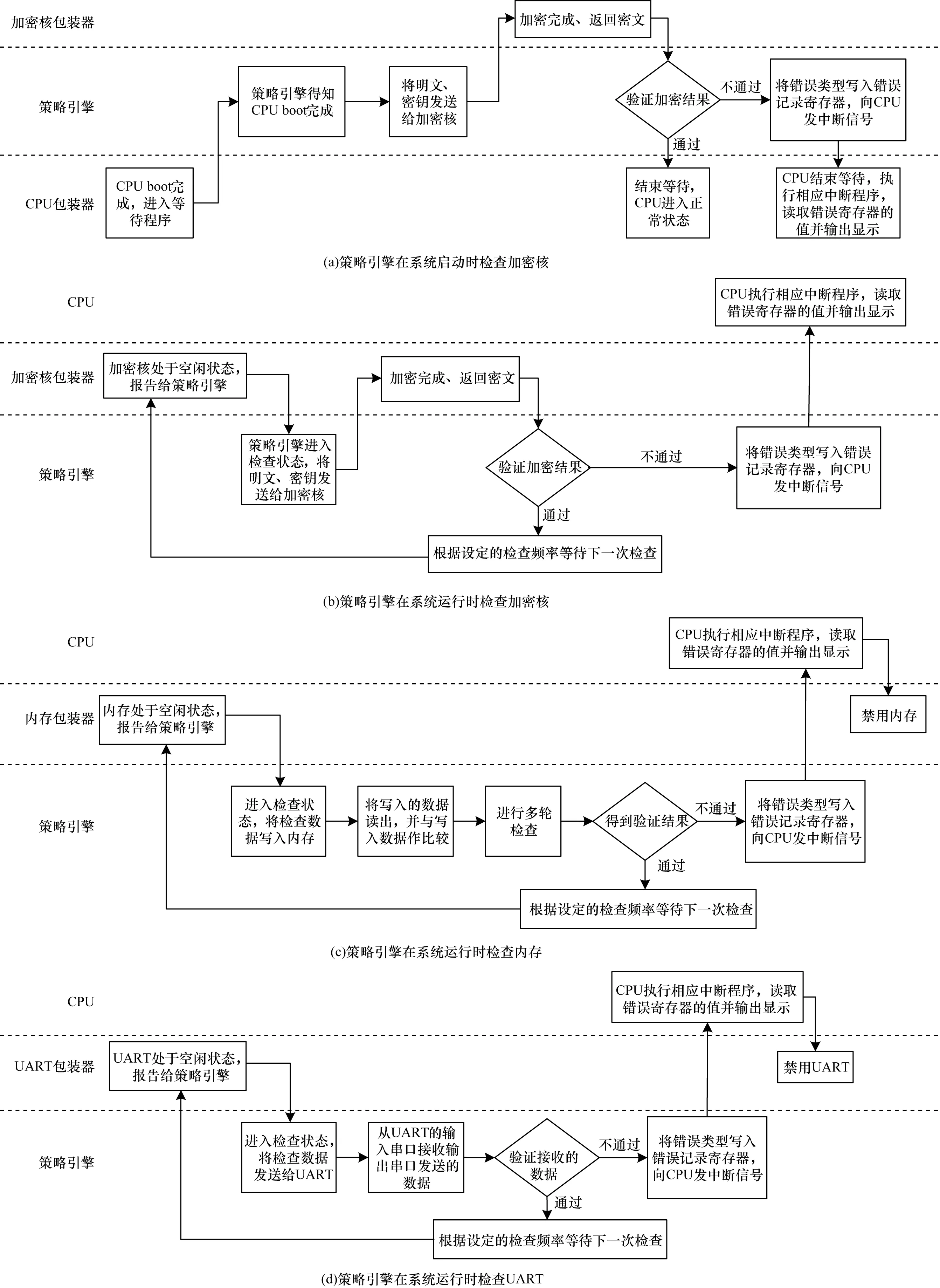

针对上文提到的攻击和安全要素,本文制定了具体执行的4条安全策略。4条策略分别对加密核、内存和外设接口进行安全检查,整体构成了对SoC场景下任务流的安全检查。4条策略的检查流程如图4所示。

策略1加密核在系统启动时不能出现功能完整性破坏,如图4(a)所示,具体过程为:

1)CPU在boot完成后先进入等待程序,这时策略引擎检测到CPU boot完成进入检查状态,开始对AES进行功能完整性检查。

2)策略引擎内部存储明文、密钥和密文对,策略引擎进入检查状态,将明文、密钥数据发送给加密核,并将加密核计算的密文取回。

3)策略引擎根据存储的正确密文验证取回的密文,若验证结果正确,通知CPU结束等待,进入正常状态;若验证结果失败,策略引擎会将错误以错误代码的形式写入错误记录寄存器,并向CPU发送中断信号,CPU结束等待执行中断程序,读取错误寄存器相应位置的值,并将其输出显示。

策略2加密核在使用过程中不能出现功能完整性破坏,如图4(b)所示,具体过程为:

1)加密核包装器检测到加密核处于空闲状态,将其报告给策略引擎。

2)策略引擎内部存储明文、密钥和密文对,当策略引擎发现加密核处于空闲状态时,策略引擎进入检查状态,将明文、密钥数据发送给加密核,并将加密核计算的密文取回。

3)策略引擎根据存储的正确密文验证取回的密文,若验证结果正确,则根据设定的检查频率进行延时等待,在满足检查条件时开始下一次检查;若验证结果失败,策略引擎会将错误以错误代码的形式写入错误记录寄存器,并向CPU发送中断信号,CPU执行中断程序,读取错误寄存器相应位置的值,并将其输出显示。

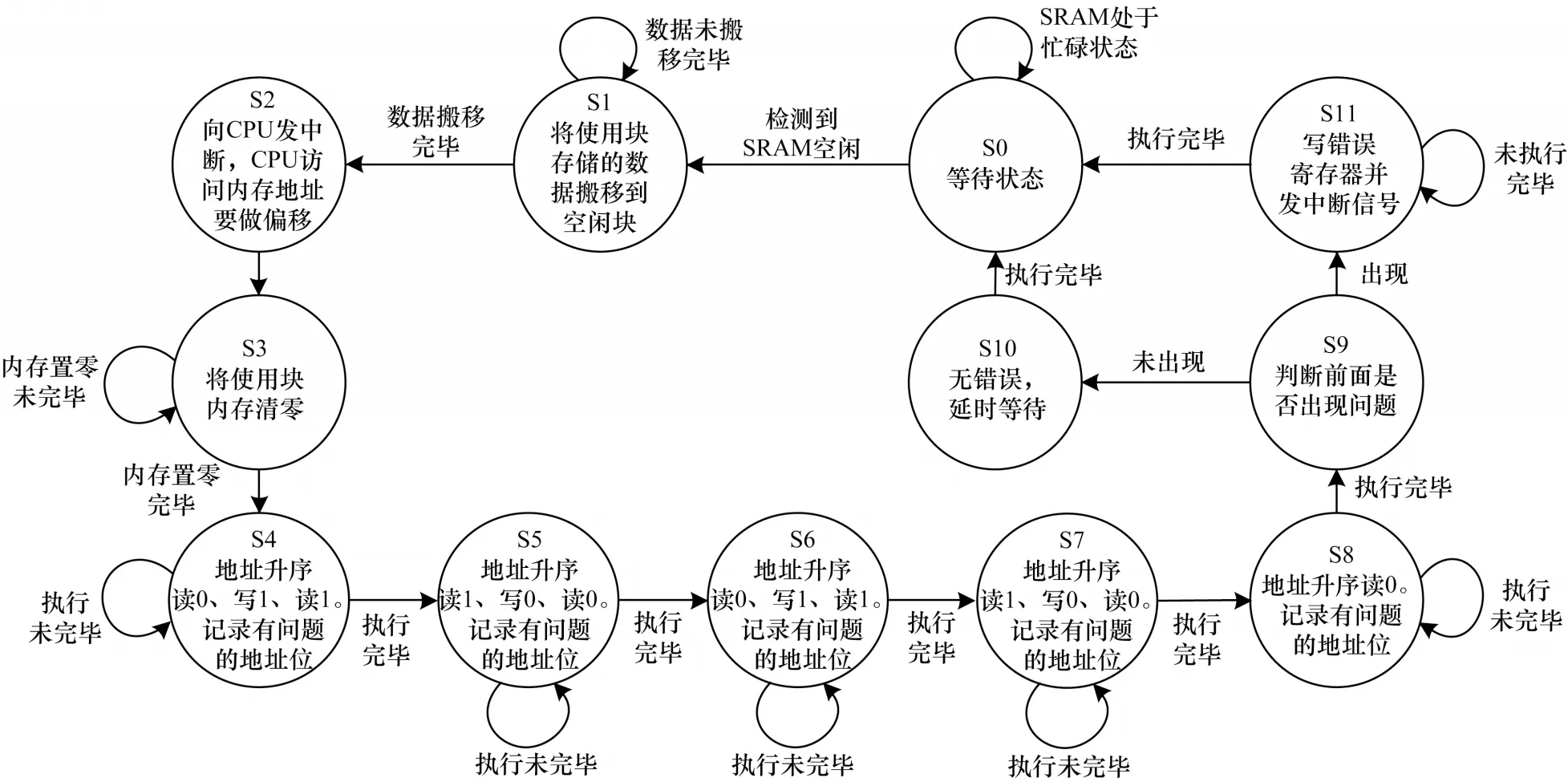

策略3在运行时内存中的数据存取不能遭受篡改,如图4(c)所示,具体过程为:

1)内存包装器检测到内存处于空闲状态,将其报告给策略引擎。

2)策略引擎进入检查状态,采用March C[19-20]算法对内存进行检查。

3)若检查结果通过,则根据设定的检查频率进行延时等待,在满足检查条件时开始下一次检查;若检查结果不通过,策略引擎会将错误以错误代码的形式写入错误记录寄存器,同时向CPU发送中断信号,CPU执行中断程序,读取错误寄存器相应位置的值,将其输出显示并进一步禁用内存。

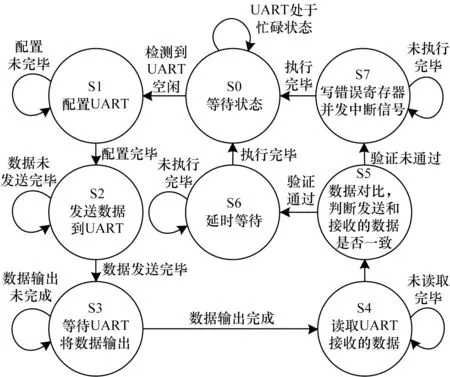

策略4外设接口传输的数据不能遭受篡改,如图4(d)所示,具体过程为:

1)外设接口为UART,UART包装器检测到UART处于空闲状态,将其报告给策略引擎。

2)策略引擎进入检查状态,将检查数据发送到UART,为验证UART传输数据是否正确,UART的输入串口接到输出串口,将发送出的数据回收进行验证。

图4 安全策略检查流程Fig.4 Procedure of security policy check

3)若检查结果通过,则根据设定的检查频率进行延时等待,在满足检查条件时开始下一次检查;若检查结果不通过,策略引擎会将错误以错误代码的形式写入错误记录寄存器,同时向CPU发送中断信号,CPU执行中断程序,读取错误寄存器相应位置的值,将其输出显示并进一步禁用UART。

在各检查流程中,检查频率预先设置快速、中速和慢速3个频次,根据实际应用条件和需要配置检查频率的大小。

5 实验结果与分析

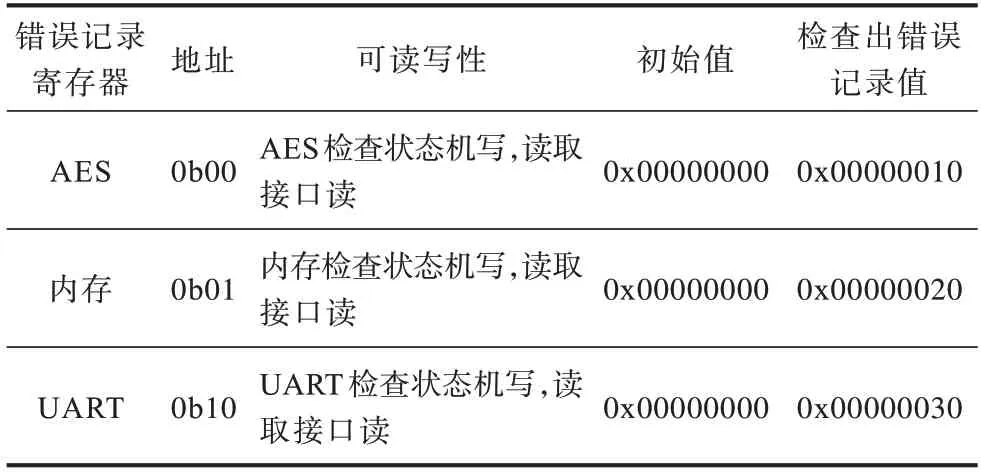

为验证实验结果,在AES、内存和UART中分别植入了所设计的运行时触发恶意硬件木马,并根据运行时安全策略分别实现对应的策略检查器。如图5所示,策略检查器以状态机的方式运行,各策略检查状态机之间并行运行,分别对各模块进行检查,在整体上完成了对SoC中数据加密传输过程的系统级安全检查。错误记录寄存器中包含3个32位寄存器,分别记录3个检查状态机的检查结果,相应的地址和功能定义如表1所示。

图5 安全策略检查电路整体架构Fig.5 Overall architecture of the security policy check circuit

表1 错误记录寄存器功能说明Table 1 Function description of error record registers

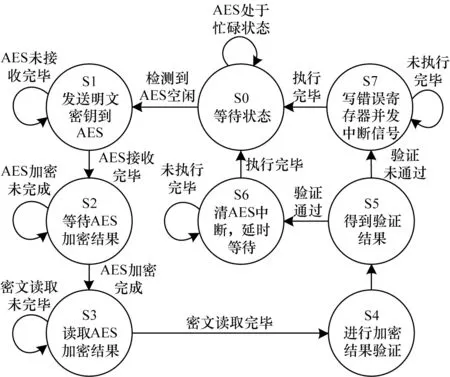

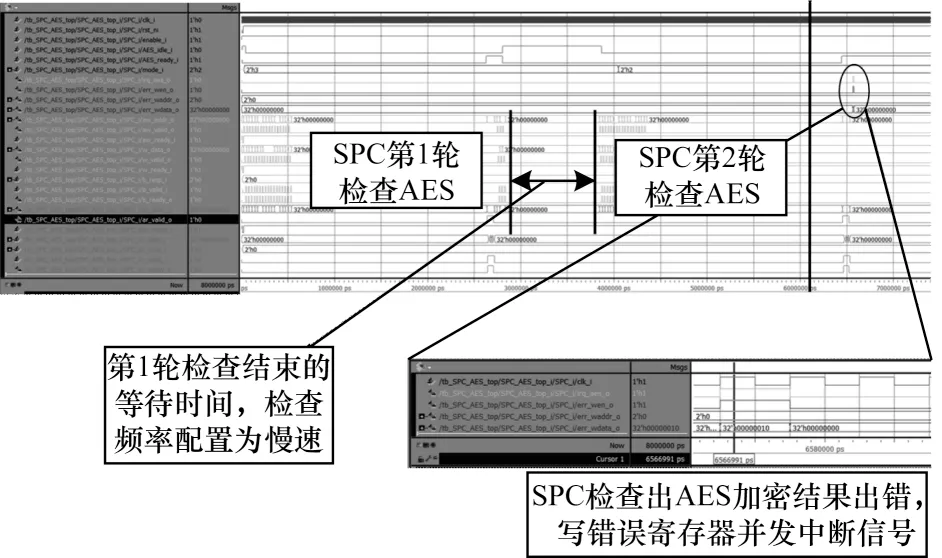

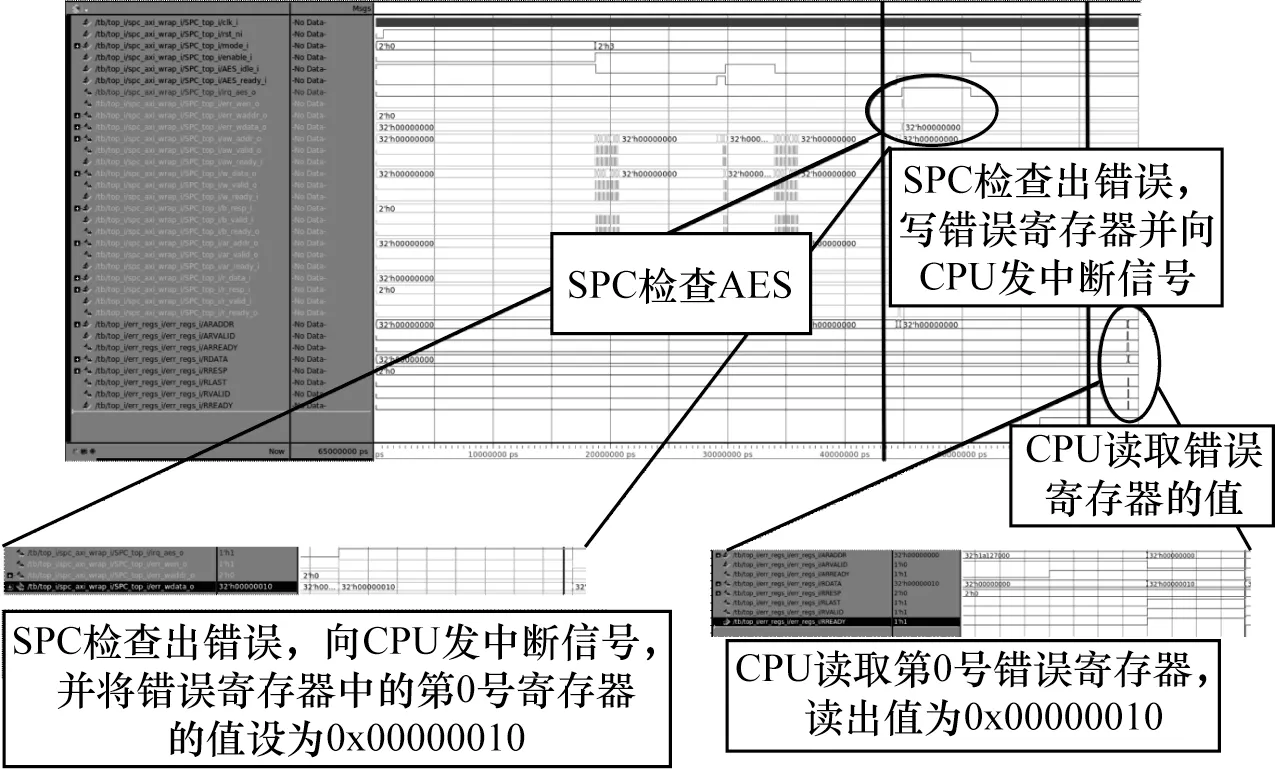

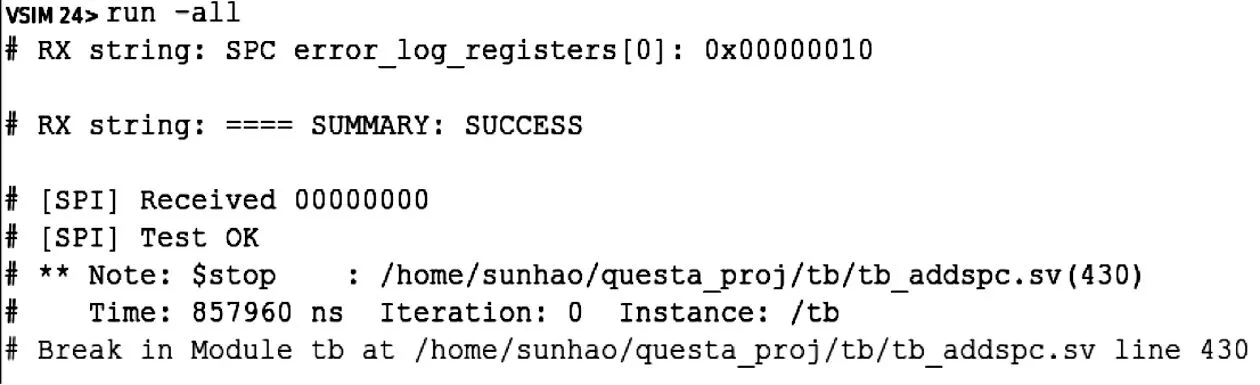

AES运行时检查状态机如图6所示,由于AES在接收明文和密钥数据时就进入busy状态,因此在加密完成后AES会输出中断信号,需CPU或SPC发送清中断信号才会恢复到等待(idle)状态,否则AES会停留在忙碌(busy)状态,不能再次工作。根据状态跳转图进行AES检查状态机模块的Verilog代码编写,在ModelSim[21]中将AES检查状态机和植入了木马的AES进行联合仿真验证,结果如图7所示,检查频率配置为慢速,经过两轮检查发现问题,实验结果表示AES检查状态机可以实现检查功能。内存和UART检查状态机的状态跳转图如图8、图9所示,仿真结果与图7类似,不再详细介绍。将AES、内存和UART的策略检查器添加到PULPino系统中进行仿真验证,下面以AES检查为例,展示检查效果。策略检查器的仿真波形如图10所示,策略检查器发现错误后发送中断信号,CPU执行中断响应程序,读取错误寄存器的值并输出显示,如图11所示。实验结果显示策略检查器可以在PULPino系统中正确实现检查功能,证明了本文所设计的系统级策略检查架构的正确性与有效性。

图6 AES运行时检查状态机Fig.6 AES runtime check state machine

图7 AES策略检查状态机仿真波形Fig.7 Simulation waveforms of AES policy check state machine

图8 内存运行时检查状态机Fig.8 Memory runtime check state machine

图9 UART运行时检查状态机Fig.9 UART runtime check state machine

图10 策略检查器在PULPino系统中的仿真波形Fig.10 Simulation waveforms of the policy checker in the PULPino system

图11 CPU运行中断程序结果Fig.11 Results of CPU running interrupt program

6 结束语

本文分析物联网应用场景下可能面临的系统级安全威胁,对系统级安全策略进行分类设计,构建SoC安全检查架构,根据场景需求进行系统级安全策略配置,通过运行策略执行任务方式进行运行时安全检查。以典型数据加密传输场景为例,为路径中的攻击设计4条安全策略,并在基于RISC-V的SoC中进行策略检查架构的实现。仿真结果显示,运行时策略检查状态机可检查出加密核、内存和UART接口的功能完整性问题并发送错误中断信号,验证了本文设计的SoC安全策略检查架构的正确性与有效性,并且本文研究对建立物联网SoC,尤其是采用开源硬件系统的运行时安全评估体系具有一定的理论意义和实用价值。后续将进一步优化策略检查电路的设计,搭建基于FPGA的系统原型,并分析安全检查架构对系统性能以及资源功耗开销的影响。