基于FPGA的JESD204B-光纤传输接口转换器设计

2021-01-27王红亮

王红亮,和 爽

(中北大学,电子测试技术国家重点实验室,仪器科学与动态测试教育部重点实验室,山西太原 030051)

0 引言

随着星载通信、雷达测试等领域的不断发展,高速数据采集技术的需求不断增加,传统并行接口已逐渐难以满足日益增长的数据传输速率[1-2]。2011年推出的JESD204B串行接口,大幅提升传输速率,并具有对应封装尺寸小、成本低,PCB布局布线简化等优势,已成为目前高速数据转换器的主流接口片[3-5]。但JESD204B接口主要针对转换器采集数据收发,不适用于较远距离的传输,无法与常见的高速数据分析存储设备进行互联。而JESD204B的相关IP产品也尚未开源,无法针对特定开发进行裁剪,且费用昂贵[6]。因此,开发远距离传输JESD204B信号的拓展系统具有重要意义。

目前,光纤传输由于其带宽高、距离远、灵敏度高、体积小等优势[7],已广泛应用于高速数据分析存储设备。在此背景下,本文提出了一种JESD204B-光纤传输接口转换器,并自主设计了JESD204B接口逻辑,实现了高速数据转换器与存储分析设备之间的数据收发。

1 总体设计方案

本文在对JESD204B接口和光纤传输接口相关协议进行分析后,以FPGA作为硬件控制平台,设计了相应接口逻辑、硬件电路与外围测试环境。转换器系统整体方案设计如图1所示。

系统主要划分为JESD204B接口单元、光纤接口单元、数据缓存单元以及时钟管理单元。AD采集板卡的JESD204B接口通过FMC(FPGA mezzanine card)插槽与系统的JESD204B接口单元互连,JESD204B接口单元接收到的数据经过处理整合后,传输至数据缓存单元进行缓存;光纤接口单元基于Aurora传输协议,负责将接收数据打包处理并由SFP光模块转换为光纤信号向外部设备传输;时钟管理单元负责向JESD204B接口内部逻辑和外部AD采集板卡,以及光纤接口内部逻辑提供所需时钟。

2 硬件设计

2.1 JESD204B接口单元设计

系统与外部采集板卡互连采用FMC接口。FMC接口插拔方便,接口信号类型丰富,包含电源信号、JTAG信号、IIC信号、普通用户信号及吉比特信号等,有助于系统针对不同外部采集板卡实现不同的拓展功能,提高系统设计的灵活性[8]。其中,吉比特信号引脚信号完整性可保证高达10 Gbps的信号通信,可满足目前常见采集板卡JESD204B接口的数据传输要求。

外部采集板卡多采用SPI接口进行工作模式等配置。为保证采集板与系统之间SPI信号的电平匹配,设计选取4位双电源电平转换芯片SN74AVC4T774对配置信号进行处理,并在两端信号分别串接阻值为22 Ω的电阻,以防止信号过冲对电路的影响,电路连接如图2所示。

图2 SPI接口电平转换电路

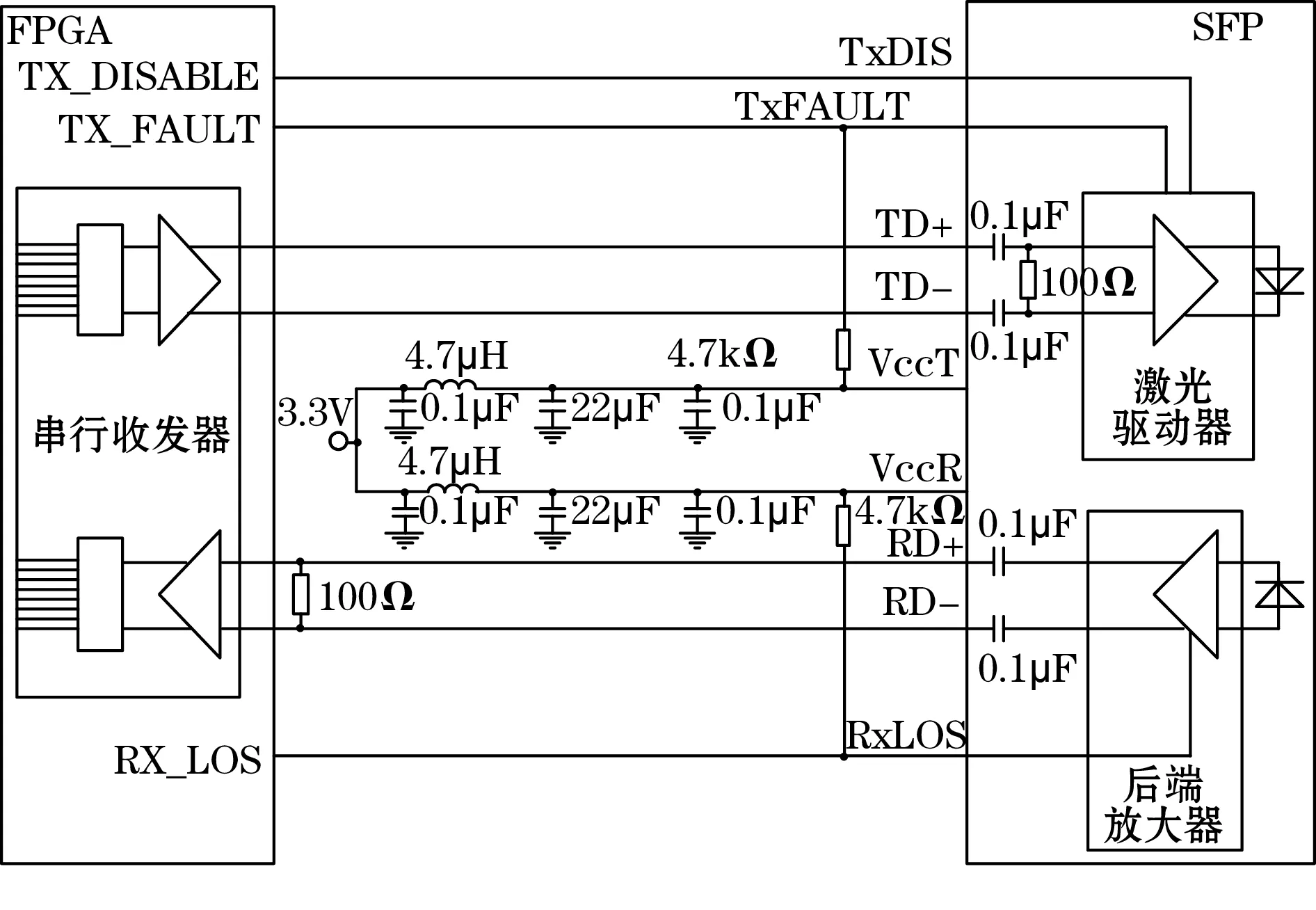

2.2 光纤接口单元设计

光纤接口选用SFP光模块AFBR-703ASDZ来实现电信号与光信号的转换与传输。AFBR-703ASDZ支持10 Gb以太网设备设计,最高线路速率达10.313 Gbps,最大传输距离300 m,可有效传输前端JESD204B接口单元的数据。光纤接口单元电路连接如图3所示。

图3 光纤接口单元硬件连接图

光模块的收发数据端口RD+、RD-、TD+、TD-内部采用交流耦合方式,与FPGA内部串行收发器相连,走线阻抗需满足差分阻抗100 Ω,以保证高速传输的信号完整性。其利用输入的高速差分逻辑信号来调节内部发送端的激光驱动器电流。FPGA通过TxFAULT和RxLOS信号检测光模块发送与接收链路故障与否,通过TxDIS信号控制光信号关断。

3 FPGA内部逻辑设计

FPGA平台选用Xilinx Kintex系列的XC7K325T芯片,其高性能HP Bank适配于DDR缓存接口,内部集成GTX串行收发器,最大线路速率支持12.5 Gbps。FPGA作为系统的逻辑控制核心,完成JESD204B接口与光纤接口的桥接通信。

系统上电后,各单元进入初始化阶段,FPGA首先对时钟管理芯片进行配置,确保各单元所需时钟准确无误。之后控制JESD204B接口逻辑向外发送同步信号,通知外部采集板卡启动链路同步,待链路建立完成后,控制数据缓存逻辑接收采集数据,同时光纤接口单元与外部设备链接完成后,开始从缓存中读取数据向外传输。

3.1 JESD204B接口逻辑设计

接口逻辑构建基于GTX串行收发器与后端通道逻辑组成的数据流逻辑结构,如图4所示。在状态控制逻辑的控制下,外部串行数据由GTX串行收发器完成接收,经由通道逻辑部分实现接口协议的相关时序与验证。

图4 JESD204B接口逻辑结构

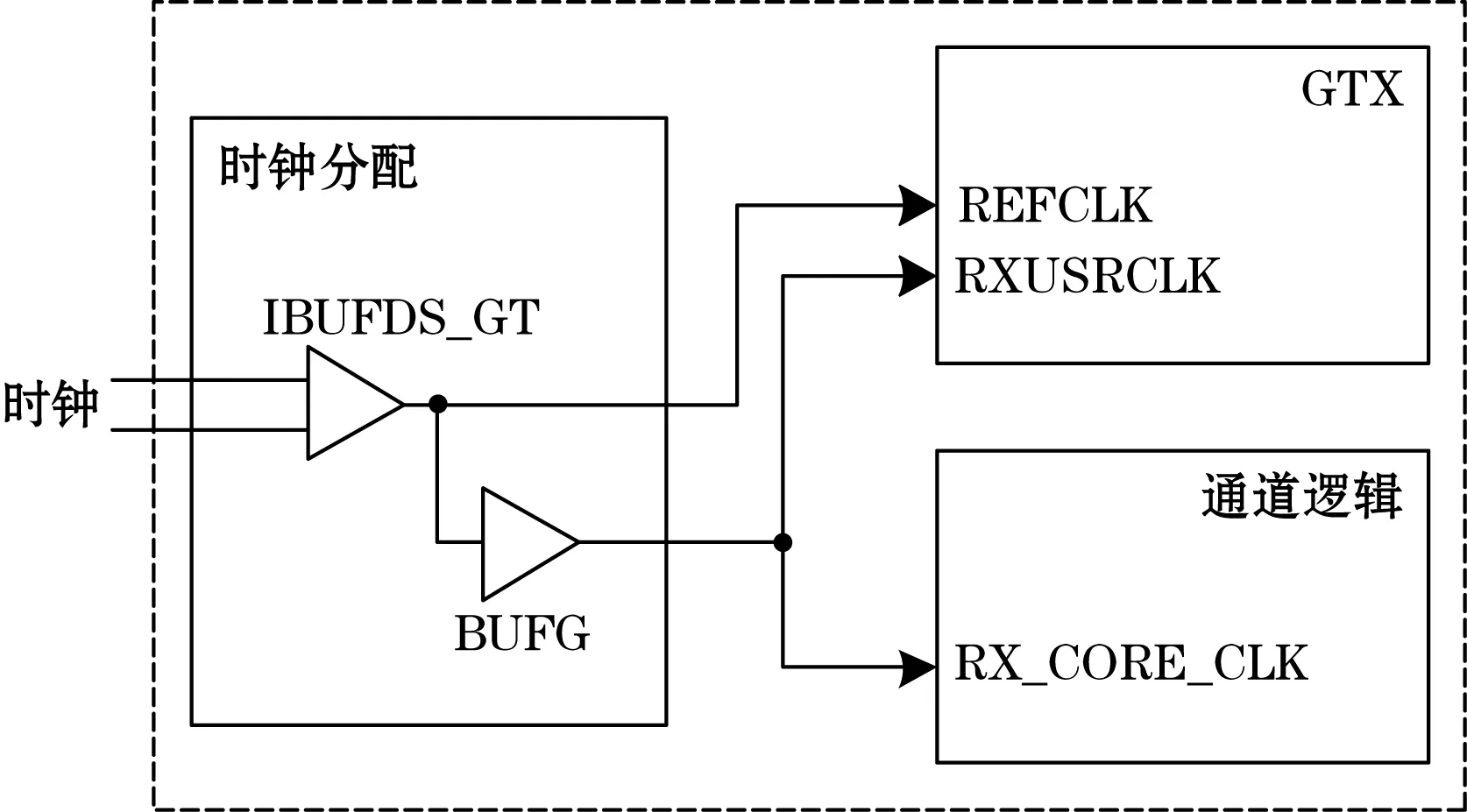

其中,对于GTX串行收发器而言,其内部锁相环需要高精度参考时钟以保证初始化等流程正常运行,其后端的数据通路需要用户时钟作为数据流传输基准。通道逻辑作为GTX数据流的承接部分也需要核心时钟确保正确传输。为减少时钟输入资源,系统配置通道逻辑数据通路与GTX输出数据通路保持一致,从而保证参考时钟与数据流时钟为同一频率,均由串行收发器的MGTREFCLK差分引脚输入的时钟提供。时钟分配逻辑结构如图5所示,输入时钟由GTX专用缓冲转换器IBUFDS_GT转换为单端时钟后,一路直接输出至GTX的REFCLK端口,另一路通过全局时钟缓冲BUFG增大扇出能力,然后分别输出至GTX的RXUSRCLK端口与通道逻辑的核心时钟[9]。

图5 时钟分配逻辑结构

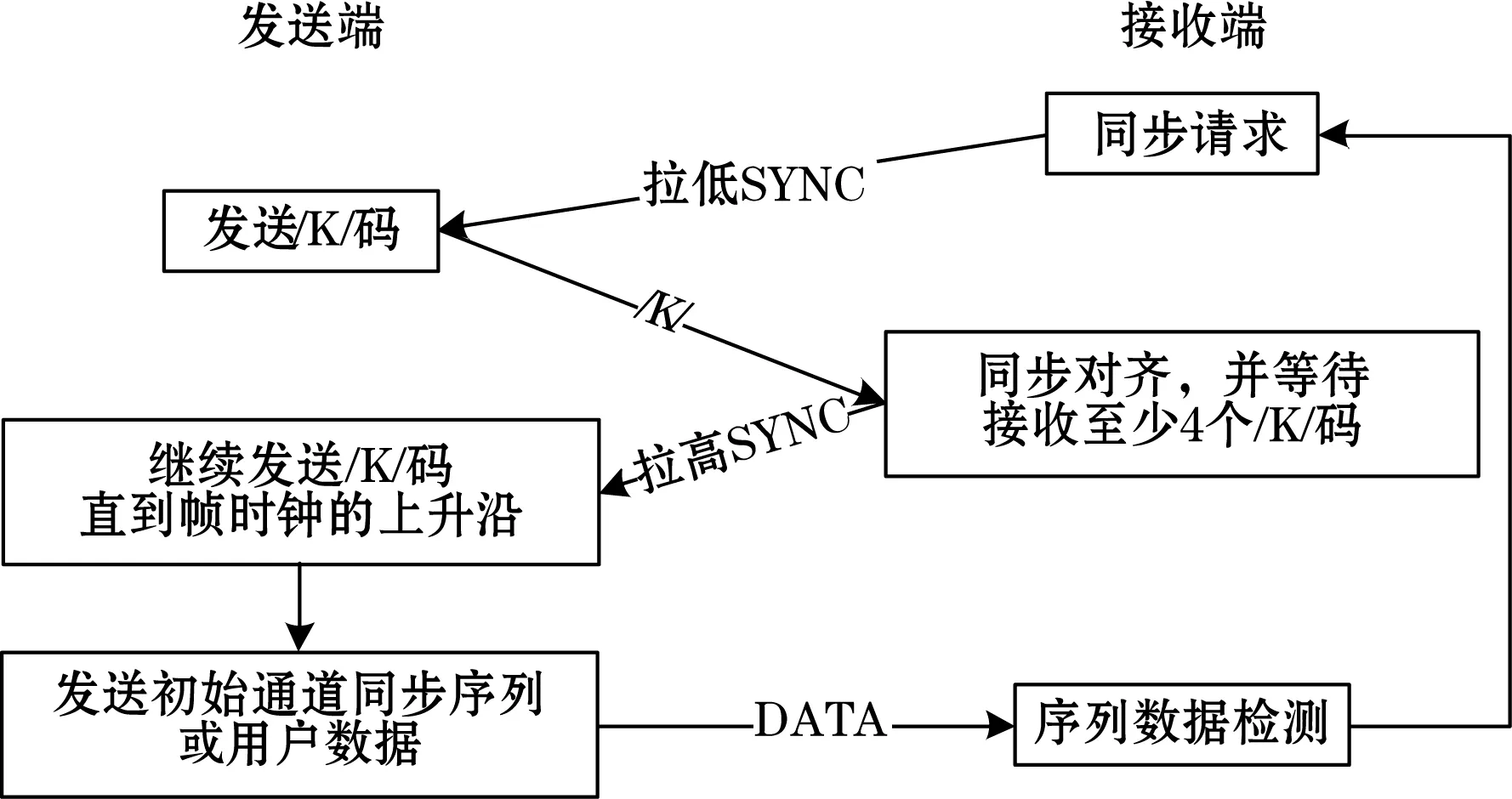

数据流根据JESD204B协议完成同步与传输,流程如图6所示[10]。首先拉低同步信号SYNC,通知外部采集板卡开始建立链路并发送/K/码。同时拉高GTX的复位信号并选择顺序复位,对GTX进行初始化,以保证内部锁相环与逻辑功能器件状态稳定。待复位完成后,对用于串行数据对齐的特殊字符Comma进行检测。检测到Comma字符后,对应检测信号拉高,启动串行数据与时钟的对齐,并将对齐后的数据解串解码。解串解码后的并行数据,需要进行/K/码检测,当连续无误地检测到4个/K/码后,拉高信号SYNC,协议的码组同步阶段结束。初始通道同步阶段开始,外部采集板卡会发送4个包含链路参数的多帧序列,如果序列验证无误,则进入数据传输阶段,链路建立成功;如果验证有误,则回到码组同步阶段,重新初始化GTX以及对齐串行数据。

图6 协议同步交互流程

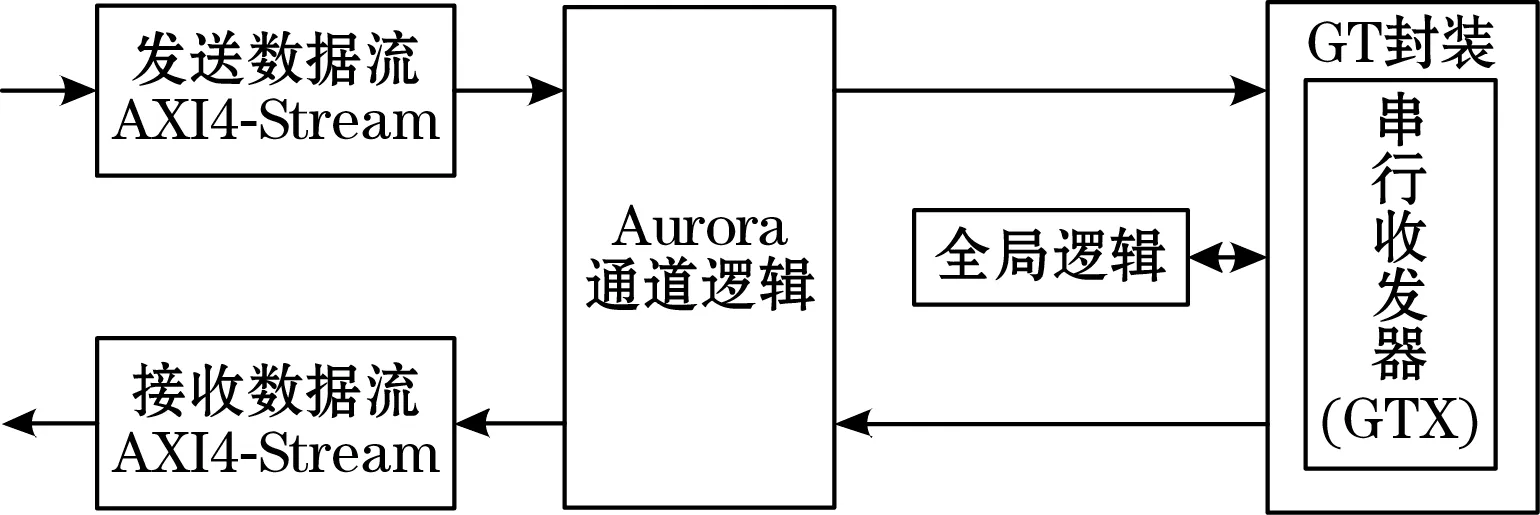

3.2 光纤接口逻辑设计

光纤接口逻辑仍依托于FPGA的底层GTX串行收发器,同时采用Aurora协议进行传输。Aurora是一个轻量级链路层协议,在Xilinx FPGA中可免费使用,拓展性强且占用资源成本低,方便用户针对开发需求进行定制,图7是Aurora IP的内部逻辑结构。

图7 Aurora IP内部逻辑结构

针对系统的高速数据流设计需求,设计具体采用Aurora 64B/66B协议,其相较传统8B/10B编码方式的传输开销更低,线路速率更高,最高可达10.312 5 Gbps[11]。用户数据接口采用通用化总线接口中的AXI4-Stream接口,AXI4-Stream接口面向高速数据流传输,无需考虑地址映射,允许无限制数据突发传输。整个接口通过全局逻辑完成通道绑定以及进行通道初始化,由通道逻辑实例化驱动GTX串行收发器,处理数据流的解码和编码,并执行错误检验。

3.3 数据缓存逻辑设计

数据缓存单元采用基于Xilinx MIG IP的乒乓读写操作控制方案,利用对不同存储区域的读写切换有效降低预充电命令与激活命令之间的时间间隔,并且使用超长突发操作减少发送列寻址和读写命令所造成的时间延时[12],显著地提高数据传输效率。

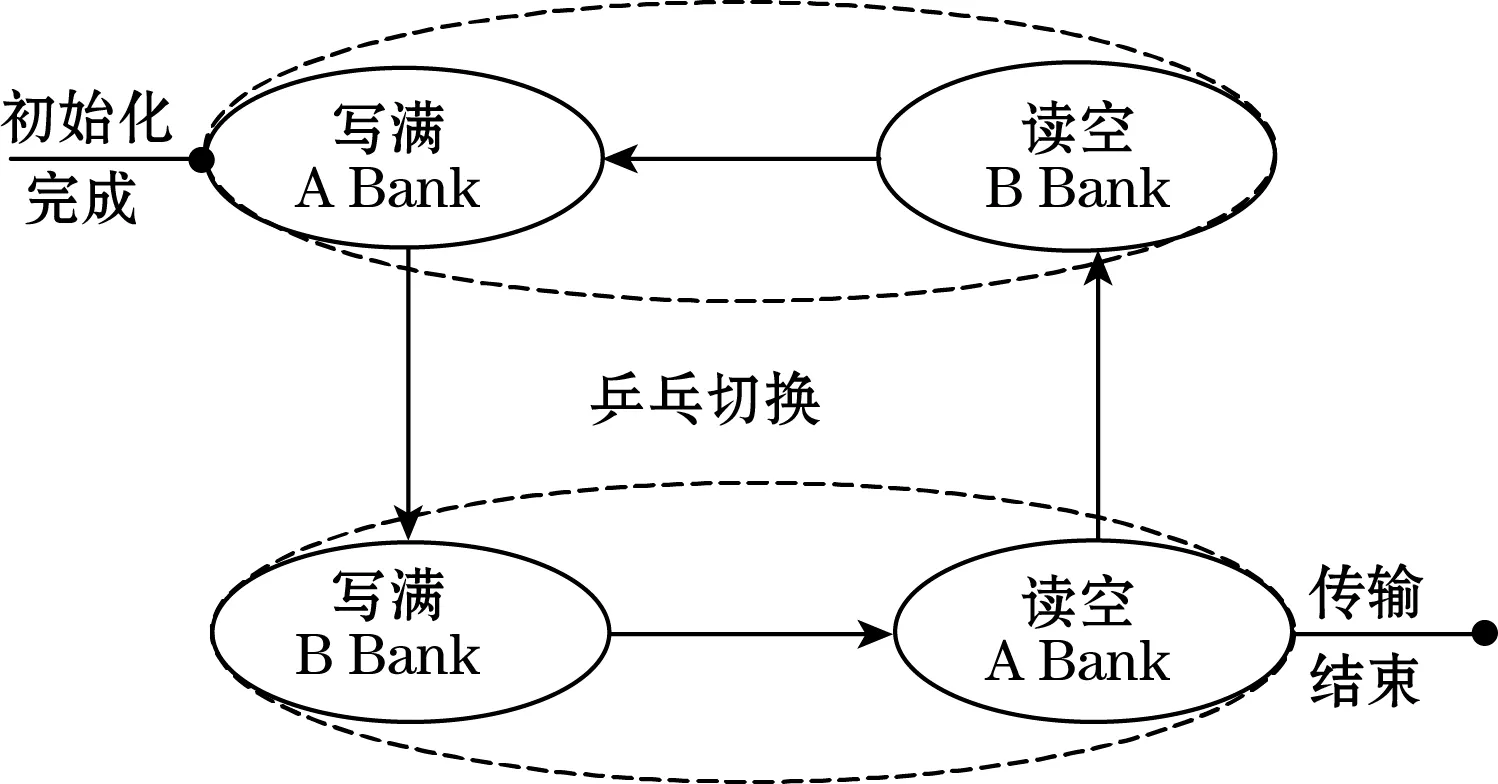

图8 DDR3读写乒乓操作流程

本设计中乒乓操作流程如图8所示,将DDR3分为A、B两个Bank,当初始化完成之后,缓存逻辑以写满DDR3中的A Bank作为开始标志;往B Bank写数据至写满后,并自A Bank读出数据至读空,组成一个乒乓操作;同理,自B Bank读出数据至读空后,并往A Bank写数据至写满,组成另一个乒乓操作,2个操作循环往复;数据传输结束时,缓存逻辑将A Bank中数据读出,作为DDR3中数据缓存结束的唯一标志。另外,由于只是一块DDR3及一个MIG IP来实现乒乓操作,其中命令地址线是共用的,因此该设计利用分时复用的方法来达到读写数据线和地址线的调用。

4 测试验证

为测试系统JESD204B接口单元功能完整性,外部采集板卡选用具有JESD204B接口的ADS54J60EVM采集板,其采样分辨率为16位,采样率设为500 Msps,传输编码方式为8B/10B,则测试链路的线路速率为10 Gbps。由信号源向采集板卡提供2.5 MHz的模拟正弦波信号输入,Vivado软件与ILA核抓取FPGA内部逻辑信号,功能测试结果如图9所示。可以看出,在GTX复位完成及Comma码检测对齐正确后,通道恢复出正确的K码,并按顺序完成码组同步,初始通道同步,用户数据传输各阶段,采集到稳定平滑的正弦波信号,JESD204B链路建立成功。

图9 JESD204B单元板级逻辑验证时序图

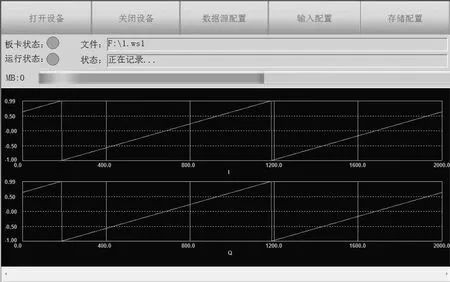

其次,测试系统整体链接传输功能。为方便数据观测,将采集板卡配置为测试模式,发送连续递增数据序列,并将光纤接口单元与外部高速存储测试记录仪互连。序列发送周期为1 000个采样点,双通道数据链路发送,FPGA内部数据抓取结果如图10所示,高速存储记录仪记录数据结果如图11所示。结果显示,采集板数据可通过系统稳定无误的传输至高速存储记录仪。

图10 递增序列板级逻辑数据抓取结果

图11 高速存储记录仪数据记录结果

5 结束语

本文设计了一种JESD204B-光纤传输接口转换器,实现了JESD204B接口与光纤接口的桥接传输,拓展JESD204B信号的通用性与传输距离,使之能与高速数据分析存储设备对接。通过测试,链路传输速率可达10 Gbps,且数据传输稳定无误,符合设计要求。本文为高速数据采集传输领域的提供了一种解决方案,对与JESD204B接口自主化的进一步研究具有参考意义。