一种低成本带吸收电容的防浪涌电路

2021-01-11严利民高文凯

孙 叠,严利民,贾 石,高文凯

(1.上海大学机电工程与自动化学院,上海200444;2.上海大学微电子研究与开发中心,上海200444)

在电路设计中,浪涌是指当刚开通电源的那一瞬间电源内部产生的强力脉冲,以及电源和电路中其他部分受到的外来脉冲,包括浪涌电压和浪涌电流[1].电路很可能在浪涌到来的瞬间遭到损坏,如PN结电容击穿、电阻烧毁等,因此需要在电路中加入浪涌保护结构,利用其结构中的元器件泄放、吸收或消耗浪涌能量,从而保护整个电路不受破坏[2].

目前,电路中的浪涌保护结构主要分为被动式和主动式2种.被动式通常采用二极管来泄放浪涌能量,虽然二极管体积小、响应快,但对电路的硬件性能要求高;主动式采用金属-氧化物半场效晶体管(metal-oxide-semiconductor field-effect transistor,MOSFET)来吸收浪涌能量,虽然MOSFET结构简单、安全等级高,但对元器件功率等级的要求高[3].目前,Texas Instruments,Maxim Integrated,Silergy Corp等国际公司均采用主动式结构进行浪涌保护.

本工作在主动式的基础上提出了一种低成本带吸收电容的浪涌保护电路,将廉价的电容和电阻并联组成吸收电路,避免了浪涌能量瞬间烧毁MOSFET情况的发生,并使用低廉小功率MOSFET替代高价大功率MOSFET,降低电路成本.如果采用同样功率等级的功率MOSFET,所设计的电路可以大幅提升浪涌电压等级,提高整个电路的稳定性.

1 传统浪涌保护结构

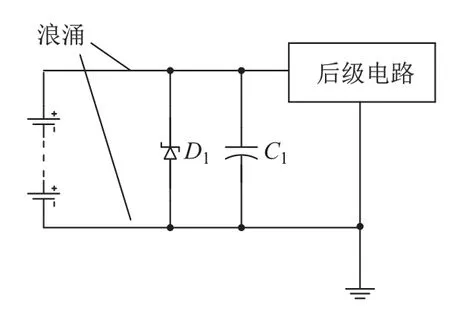

被动式浪涌保护结构通常采用瞬态电压抑制(transient voltage suppressor,TVS)二极管来泄放浪涌能量[4],其具体电路结构如图1所示.图1中,D1为TVS二极管,C1为吸收电容.

图1 被动式浪涌保护电路Fig.1 Passive surge protection circuit

在实际操作中,应使被保护电路的最大安全允许电压Vh高于最大箝位电压Vref.如果采用TVS进行浪涌保护,那么Vref至少比TVS的击穿电压Vb大,后级电路的Vh至少大于1.5倍的Vref.理论上Vb至少是后级电路中负载的最高电压Vs的1.2倍.假设Vs为25 V,Vb最小为30 V,通过运算可得Vh=1.5Vb=45 V.由Vh值可使后级电路的耐压大幅提高,而耐压的提高必然会增加整个电路的硬件成本[5].

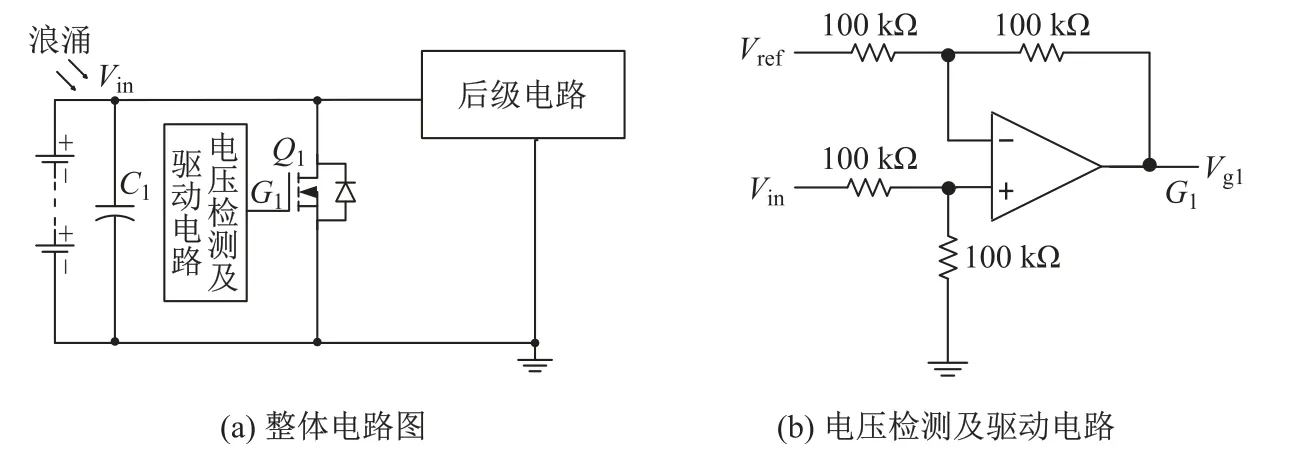

为了降低后级电路的硬件成本,须解决Vh比Vs高的问题.图2给出的由电压检测及驱动电路和功率MOSFET组成的主动式浪涌保护电路结构是由国内外研究机构提出的.如图2(b)所示,电压检测及驱动电路是由运算放大器组成的减法电路[6].

根据电路分析得到MOSFET的导通电压:

在正常工作情况下,浪涌未产生时Vin<Vref=30 V,Vg1=0 V,功率MOSFET的功率管Q1关闭.当浪涌出现时,Vin会上升,但Vg1依旧小于Vth(Vth是Q1的导通阈值),因此Q1仍然没有导通.如果Vin继续上升导致Vg1大于Vth,使得Q1导通,那么浪涌能量通过Q1排出,能达到浪涌保护的效果.

此方案能使Vh大幅度降低,从而降低硬件成本[7],但是这个浪涌保护结构存在一个经济性的问题,因为Q1的规格须很高才足以将瞬间的能量泄放掉,而MOSFET规格越高其制造成本也就越高[8].

图2 主动式浪涌保护电路结构Fig.2 Active surge protection circuit

2 低成本带吸收电容的防浪涌电路工作原理

针对上述传统结构存在的缺陷,本工作提出了一种能达到相同浪涌保护效果的浪涌保护电路结构.该结构中Vh明显降低,整个电路成本也大幅度下降.

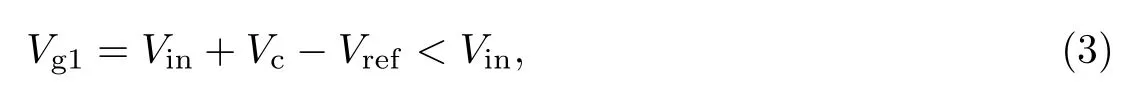

图3为低成本带吸收电容浪涌保护电路结构.图3中,电路结构由主动式模块和缓冲电路组成,缓冲电路由吸收电容C2和放电电阻R1并联构成.低成本电容C2的作用主要是吸收部分浪涌能量,R2则是将C2上的能量慢慢释放出去.该结构在使Vh大幅度降低的基础上采用低成本的小功率Q1吸收剩下的浪涌能量,从而降低整个电路的成本.与主动式保护电路类似,根据电路状态分析得到MOSFET的导通电压:

从式(2)中可以得出,Vg1还与电路中吸收电容的电压相关.

图3 低成本带吸收电容浪涌保护电路结构Fig.3 Low-cost surge protection circuit structure with absorption capacitance

3 仿真分析

本工作通过Saber软件对提出的结构进行了仿真模拟.取C1=1µF,C2=20µF,R1=5Ω,Vref=20 V,Vsurge=60 V,Csurge=5.93µF,这里Vsurge、Csurge为模拟浪涌发生器的电压、电容.仿真结果如图4所示,其中Id是Q1流过的电流;Vc,max为电容两端最大电压;Vin,max为最大输入电压.

(1)0<t≤t1.没有浪涌时,Vc=0 V,Vin<Vref,Vg1=0 V,Q1处于关闭状态.当浪涌来临时,Vin开始上升,在Vin没有超过Vref时,Q1继续保持不变[9].

(2)t1<t≤t2.因为存在浪涌能量,Vin会继续上升,一旦Vin超过Vref,Vg1>0,但此时Vg1-Vc<Vth,Q1依旧没有导通,Id=0 A.

图4 低成本带吸收电容浪涌保护电路仿真结果Fig.4 Simulation results of low-cost surge protection circuit with absorption capacitor

(3)t2<t≤t3.Vin继续上升,当Vg1-Vc>Vth时,Q1导通,一部分浪涌能量由Q1消耗掉,一部分存储到电容C2上,Id开始上升,Vc开始逐渐上升,Vg1也随之上升.由于R1只有5Ω,瞬间放电能力很弱,R1的峰值电流相比Q1的峰值电流要小很多,故此时R1的作用可以忽略不计.

(4)t3<t≤t4.浪涌结束后,Vin和Vg1会慢慢下降,当Vg1-Vc<Vin时,Q1关闭,Id=0 A.同时C2上的能量开始通过R1慢慢释放,放电时间常数T=RC=5×33×10−6=0.165 ms.

(5)t>t4.Vin持续下降,当Vin+Vc=Vref时,Vg1=0 V,Q1继续处于关闭状态,Id=0 A.同时C2上的能量继续通过R1慢慢地释放,放电时间常数T=RC.通过运算可得边界条件

根据电量守恒[10]

通过式(3)、(4)以及前面设定的值可以得到

由式(5)可知:假定Vref=20 V,电容C2的最小值和Vsurge成线性正比例关系;假定Vsurge=60 V,电容C2的最小值和Vref成倒数比例关系;通过数学分析可以得出把Vref设定在10~20 V之间是比较合理的结论.

由式(5)推导出式(6):

从而可以推导出C2上吸收的能量:

从式(7)可知,W与C2的容值成反比关系,因此在满足式(5)的条件下,尽可能减小C2的容值,从而降低MOSFET吸收的浪涌能量[11].

4 实验结果

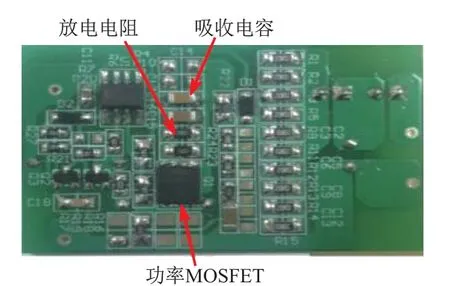

为了验证理论和仿真结果,本工作设计了一个带吸收电容浪涌保护电路的硬件演示板(见图5),电路板上的各个参数如下:MOSFET:Infeon BCS109N10NBS3,100 V/10.9Ω/63 A;2颗陶瓷贴片电容:Murata,GRM31CR61H106 MA12 L,10µF/50 V/X5R/1206;放电电阻:(5±1%)Ω.所有的初始条件(C1=1µF,C2=20µF,R1=5Ω,Vsurge=60 V,Vref=20 V)和Saber中仿真条件一致.

图5 带吸收电容浪涌保护电路硬件演示板Fig.5 Surge protection circuit hardware demo board with absorption capacitor

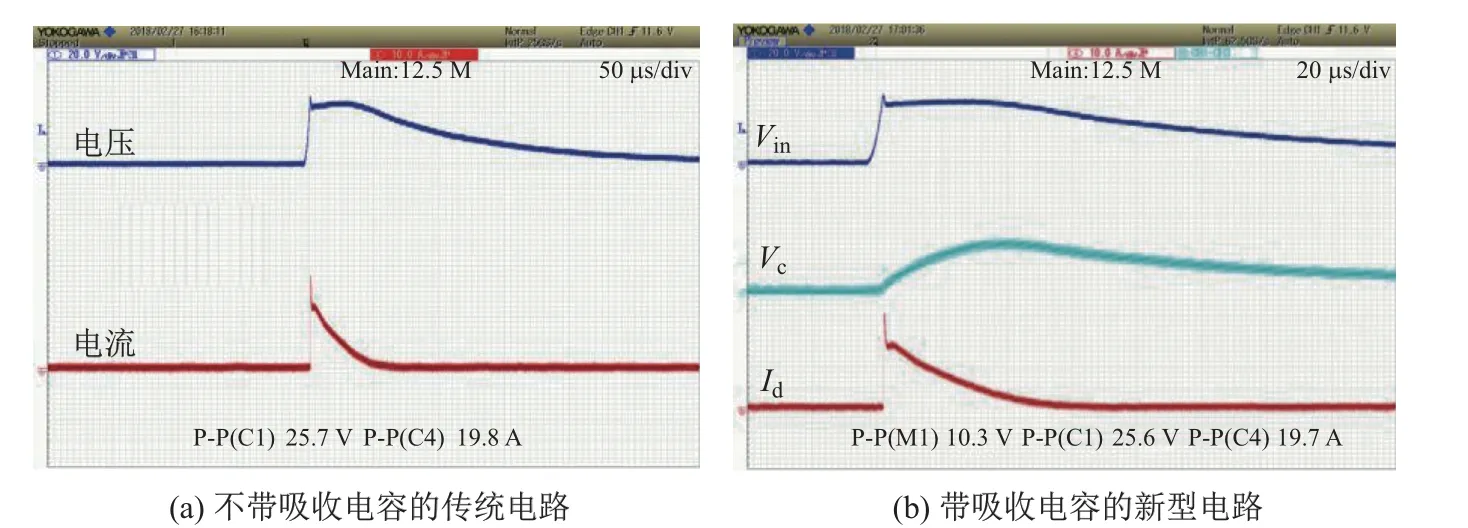

图6(a)显示不带吸收电容的传统电路测试结果,其中浪涌保护电路的电流Id峰值为19.8 A;(b)显示带吸收电容的新型电路测试结果.从(b)中可以看出:Vin、Vc、Id与图4中的理论分析结果非常吻合,增加了吸收电容之后,浪涌保护电路的电流Id峰值为19.7 A.对比可以发现,该浪涌保护电流的Id峰值在增加了吸收电容之后只变化了0.5%,可见增加吸收电容C2,对Id峰值的影响可以忽略不计.

图6 浪涌保护电路测试结果Fig.6 Test results of surge protection circuit

从图6(a)中可以看出,Q1吸收的能量近似为E=(VrefId,max×50µs)/2=6.6 mJ,其中Id,max为最大保护电流.(b)增加C2后,由于C2的电压为10.3 V,吸收了1.06 mJ能量,从而Q1吸收的能量就降低了16%.假设C2=10.9µF,当其电压值达到20 V时,将有2.18 mJ的能量被C2吸收,这样Q1吸收的能量将相应降低33%.

上述实验结果表明:当如(b)所示增加C2之后,新型电路可以在浪涌瞬间显著吸收浪涌能量,大幅提高浪涌电压等级[12];廉价的电容和电阻组成的吸收回路可以大幅降低电路结构对Q1性能的要求,从而使得整个浪涌保护电路的成本显著降低.

5 结束语

本工作提出了一种低成本的带吸收电容浪涌保护电路.通过理论分析、软件仿真以及实验测试发现,在该电路结构中加入缓冲电阻-电容电路(resistor-capacitance circuit)网络可以大幅降低后级电路最大安全允许电压,并且可以降低电路结构对MOSEFT的功率要求,从而降低浪涌保护电路的成本,提高电路的可靠性,具有实际推广应用价值.