基于USB数字电离层斜测接收机设计

2020-12-29赵一超

赵一超

摘要:为了满足电离层斜测接收设备小型化的需求,提出了一种小型化数字斜测接收机的设计方案。该接收机使用16 bit AD 进行数据采集,利用FPGA进行时序控制和实时数据的数字下变频,最后通过CY7C68013A的USB2.0接口与上位机进行数据传输。实测结果表明,该接收机灵敏度,动态范围满足设计指标。USB高速传输速率为480Mbps,且传输稳定。 实测结果与设计预期有较好的一致性。该接收机具有体积小、功耗低、传输稳定以及便于维护的特点,为短波接收设备的小型化提供了一种可行的参考方案。

关键词:电离层斜测;短波接收机;CY7C68013A;数字下变频;高速AD

中图分类号:TN959.1+1,TN859 文献标识码:A

文章编号:1009-3044(2020)32-0001-05

Abstract: In order to meet the requirement of miniaturization of ionospheric oblique receiver, a design scheme of miniaturized digital ionospheric oblique receiver was put forward. The receiver uses a 16 bit AD for data acquisition and FPGA for timing control and digital down-conversion of real-time data. After all above have been done, receiver transmits data with the upper PC by using USB2.0 interface of chip CY7C68013A.The measured results show that its dynamic range and the sensitivity meet the design indicators. It also have a stable transmission rate which can reach almost 480Mbps. The measured results are in good agreement with the design expectation. It provides a feasible reference scheme for the miniaturization of short-wave receiving equipment by the characteristics of small size, low power consumption, stable transmission and easy maintenance.

Key words: ionospheric oblique sounding; short wave receiver; CY7C68013A; digital down converter; Hi-speed AD converter

電离层斜向探测主要应用在研究不同频率传播路径的模式和信道特性,也可应用于对于电子浓度的估算,从而对选频提供参考[1-2]。而斜测接收机作为斜向探测的主要设备,直接影响着整个雷达系统的性能指标,因此其一直是电离层研究的重要组成。传统的斜测接收机通常采用高中频结构,在模拟前端对接收的信号进行放大、预选、滤波,并通过本振进行混频得到中频信号。但由于模拟前端的组成设备较多,使其无法满足小型化、便携化。

伴随着电子技术、数字信号处理技术以及半导体技术的发展,近年来采用数字下变频技术的接收机已经成为一种趋势。与传统的接收机相比,数字下变频斜测接收机因为采用现场可编程门阵列(FPGA),可以将数字下变频这一过程通过硬件描述语言方便的实现。在参数一定的情况下,即保证了接收机系统的通用性以及可拓展性又省去了模拟混频设备。大大简化了模拟前端的设计[3]。USB接口据有通用性好、传输稳定、方便等特性,在近些年被广泛应用于小型化便携式设备的接口[4]。

本文提出了一种基于数字下变频思路,通过USB接口完成数据采集的斜测接收机的设计方法,在满足设计指标的同时,大大减少了设备组成,节约了系统资源。

1 电离层斜测介绍

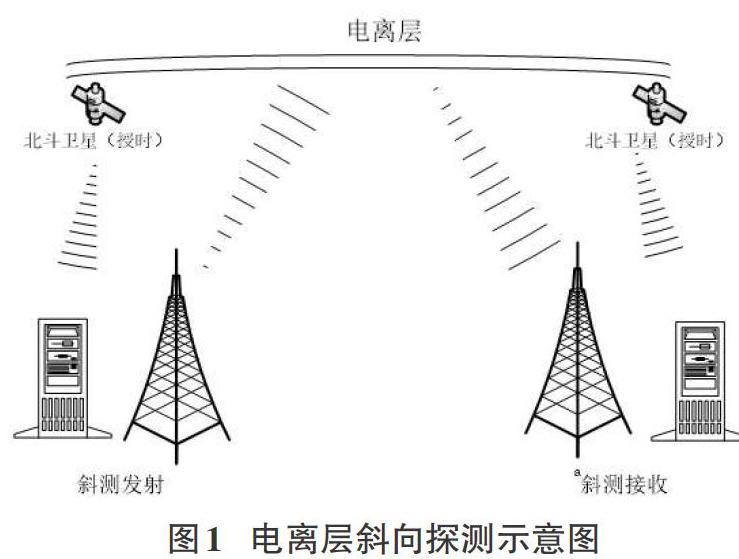

斜测的示意图如图1所示. 将发送设备设备和接收设备至于具有一定距离的A、B两处。收发设备通过北斗进行同步。通过对接收端设备收到实时的数据进行计算,得出电离层反射回波延时随频率的变化。并绘制出电离层斜向电离图[5]。

2 数字下变频

2.1 传统模拟下变频

在雷达系统中,用复信号表示信号,构造解析信号可以减少一半频带是一个优点;用来表示实信号时,运算简便也是一个很重要的优点。

传统的模拟下变频通过模拟移相器移相90°实现的,如图2所示。由于受模拟电路性能的限制,其I/Q两路并不能完全正交,与此同时I/Q两路还存在幅度的不一致性,且不易调校。

我们把由I/Q之间不正交而引起的,与所要的单边带谱对称的频谱分量叫作镜频分量。镜频分量与单边带功率之比定义为镜频抑制比IR。定义如下:

其中,[φ2e] 为相位正交误差,[α]为幅度相对误差,I/Q的正交性和幅度不对称性导致镜频抑制比低[6]。

2.2 数字正交下变频

对于窄带信号:

为解决零中频的正交误差和幅度不平衡,以优化镜频抑制比,而采用数字正交采样技术。即对信号直接采样,然后对变化后的数字信号进行处理,从而得到I/Q两路信号。如图3所示[7-8]。

3 接收机硬件设计

本接收机的硬件组成见图4,它包括模拟射频前端,模数转换电路,FPGA控制接收端以及USB接口电路组成。

如图,斜测信号经电离层反射被接收天线接收,首先经过模拟射频前端的调理以提高其信噪比,随后进入AD完成模数转换。随后该数字信号输入至FPGA中完成数字下变频,最后下变频后的信号按约定时序写入USB接口电路以供上位机读取。

3.1 模拟射频前端

本设计中模拟射频前端采用两级IF 低噪声放大器芯片LTC6433。该型放大器具主要具有以下几种特点:

1) 高功率增益(15.9dB);

2) 低功耗(475mW);

3) 输入/输出在内部实现50Ω阻抗匹配。

斜测探测信号经天线进入两片LTC6433组成的模拟射频前端中网络中,在经过放大后传送至30MHz的低通滤波器中以提高信号的信噪比以及抗干扰性。

3.2 模/数转换

该部分用于将模拟射频前端输出的模拟信号转换为数字信号;

在本设计中模/数转换芯片为AD公司的16bit AD LTC2165芯片。该芯片具有低功耗(最高194mW)、高SNR(76.8dB)、550MHz 满功率带宽 S/H (采样及保持)以及高SFDR(90dB)等特点[9]。

3.3 FPGA主控

在本设计中,选择Xilinx公司低功耗、小体积的XC7A100T作为主控芯片。设计语言为VHDL,主要完成时序产生和外设控制、数字下变频以及数据缓冲FIFO等模块的设计,如图5所示。

3.3.1 系统时序产生、外设控制模块

用于产生斜测接收机的工作时序,并控制外设(如AD、USB接口等)。

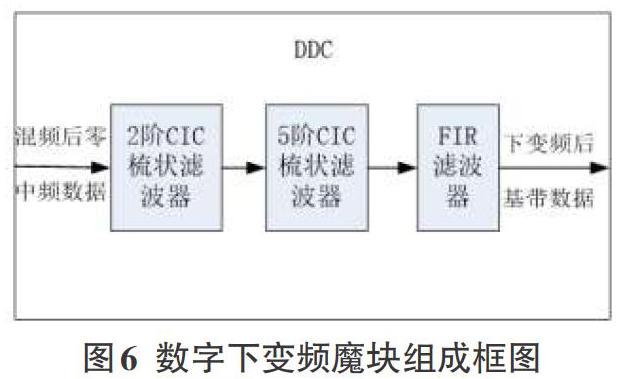

3.3.2 数字下变频模块

在本设计中,由于I/Q两路的数字下变频模块结构组成相同,在这里只列出1路的组成即可。如图6所示,分别为:

1)2阶CIC梳状滤波器;

2)5阶CIC梳状滤波器;

3)FIR滤波器(以下简称FIR)。

由图3可知,由AD采集的高频信号经过正交混频后得到1对I/Q信号。这两对信号同时经过各自的数字下变频模块(DDC)进行降采样。

根据设计DDC模块中的2阶梳状滤波器(以下简称CIC),由VHDL语言编写,抽取系数为5;而5阶CIC、FIR是利用Xilinx ISE的IP核MagiCore例化生成。其中:设置CIC5抽取率为25,FIR抽取率为10,已完成对100MHz采样率的信号的降采样。

3.3.3 异步FIFO

由于降采样后数据率(80kHz)远远小于USB接口的传输速率(12MHz),使用异步FIFO在两个不同的时钟域之间,起到跨时钟域处理的作用。本设计中同样应用MagiCore模块设计异步FIFO异步FIFO为32bit输入(包括I/Q两路数据),16bit输出(先Q后I)。

3.4 USB接口电路

3.4.1 CY7C68013A接口芯片

CYPRESS公司的 CY7C68013A是一款灵活的USB2.0外设控制器。为充分利用USB2.0的480Mbit的通讯速率,CY7C68013A包含了一个专用硬件来缓存USB的数据,以确保和外部高带宽的外部设备(FPGA、ASIC)无缝连接[10]。

CY7C68013A一般有两种方式与FPGA连接,这两种模式分别是可编程接口(GPIF)模式和从设备(SLAVE FIFO)模式。

本设计中应用SLAVE FIFO 模式。在此模式中与CY7C68013A相连的FPGA为主控设备,生成控制CY7C68013A的读、写信号。

3.4.2 USB接口电路的硬件连接

USB接口电路(SLAVE FIFO模式)硬件连接图如下图7所示。

各个信号说明如表1所示。

其中,接口时钟IFCLK有两种提供方式。一种通过CY7C68013A内部的时钟电路提供,另一种由FPGA提供。本设计中使用FPGA提供接口时钟。通过SLAVE FIFO固件中IFCONFIG寄存器bit7进行配(“0”为外部时钟,“1”为内部时钟)。

FADDR 为FIFO的双向数据总线,其寬度由EPxFIFOCFG寄存器的字宽设置位WORDWIDE选择为8 BIT或16 BIT,本设计选择16 BIT模式。

FADDR[1:0] ="00"和"10"分别选中ENDPOINT 2和ENDPOINT 6,通过固件中EP2CFG和EP6CFG寄存器分别配置ENDPOINT 2和ENDPOINT 6输入类型为OUT和IN。并将两者都设置为bulk传输方式,最大512byte,以及4×缓冲区。

FLAGA、FLAGC、FLAGD 引脚可由PINFLAGSAB、PINFLAGSCD配置相应ENDPOINT不同状态。在本设计中将FLAGA配置为ENDPOINT 2 的空状态标识,FLAGC、FLAGD分别配置为ENDPOINT 6的 “满”“空”状态。

SLWR 为ENDPOINT 6数据的写选通信号, SLOE、SLRD为读使能、选通信号均由 FPGA控制。本设计所有电平均由寄存器 FIFOPINPOLAR设置为低电平有效。

3.4.3 USB接口驱动设计与固件程序加载

到目前为止,CYPRESS公司提供可供CY7C68013A使用的最新的驱动为CYUSB3。它由开发套件CY3864安装得到。本设计中只需在cyusb3.inf添加与SLAVE FIFO 固件中对应的VID、PID值和设备描述即可。

设置好的SLAVE FIFO固件程序,需要经过Keil 2软件进行编译,生成hex文件。

本设计中CY7C68013A上电后我们采用C2烧录方式,所以还必须将.hex文件转化成.iic文件。通过CYPRESS官方控制台软件 Cypress USB Console将生成的.iic文件下载至配置CY7C68013A的E2PROM(24LC128)中。这样每次连接上位机即可通过E2PROM完成固件程序的加载。

4 软件设计

4.1 USB固件设计

根据官方说明SLAVE FIFO固件分为以下几个部分。如图8所示。

其中,fw.c 包含main函数。它执行了USB大部分操作,并且当需要自定义时,它将调用slave.c文件中特定的函数。例如TD_Init和TD_Poll。在本设计中不需要修改。

dscr.a51文件是描述文件用于存储硬件描述的数值。USB外设通过CY7C68013A 的Control端点接收枚举和操作等行为。fw.c代码截取这些请求行为,并通过存储在dscr.a51文件中的数值来完成枚举操作。

在本设计中,主要对slave.c TD_Init函数相应语句进行修改即可完成SLAVE FIFO的应用设计。以下进行说明。

IFCONFIG = 0x03; //Internal clock, 30MHz, Slave FIFO interface

SYNCDELAY;

1) 8051内部时钟为30MHz。

2) CY7C68013A 被配置为SLAVE FIFO模式,接口时钟为外时钟(FPGA 提供)

EP2CFG = 0xA0; //out 512 bytes, 4x,bulk

SYNCDELAY;

EP6CFG = 0xE0; //in 512 bytes, 4x,bulk

SYNCDELAY;

EP4CFG = 0x02; //clear valid bit

SYNCDELAY;

EP8CFG = 0x02; //clear valid bit

SYNCDELAY;

将 EP2 配置为OUT 端点,并将 EP6 配置为IN 端点。该两个端点均为四倍缓冲,并使用512 字节的 FIFO。由于本设计中没有使用EP4 和 EP8,所以它们均被取消激活。

EP2FIFOCFG = 0x00;// AUTOOUT=0,WORDWIDE=1

SYNCDELAY;

EP2FIFOCFG = 0x11;// AUTOOUT=1,WORDWIDE=1

SYNCDELAY;

EP6FIFOCFG = 0x0D;// AUTOIN=1,ZEROLENIN=1, // WORDWIDE=1

SYNCDELAY;

1) 复位FIFO。

2) 分别将端点 2 FIFO 和端点 6 配置为自动输出模式和自动输入模式,同时使用 16 位接口。

PINFLAGSAB = 0x08; // FLAGA - EP2EF

SYNCDELAY;

PINFLAGSCD = 0xEA; // FLAGD - EP6FF

//FLAGC - EP6EF

SYNCDELAY;

配置 FIFO 标志输出。 FLAGA 被配置为 EP2 OUT FIFO 的空标志, FLAGD 被配置为 EP6 IN FIFO 的满标志。

4.2 接收机FPGA程序设计

接收机FPGA的程序流程图如图9所示。

如图所示,整个工作流程可分为以下几个部分:

1) 在硬件上电之后,触发信号驱动USB复位;

2)然经过初始化系统变量之后系统进入空闲状态等待上位机的命令;

3) 如果上位机发送指令,则经过分支判断(开始工作、结束工作、寄存器配置)确定下一步工作步骤并生成相应的时序控制信号;

4) 如果開始工作,则开始对换频脉冲个数的判断(如达到预设值则进入步骤2的空闲状态。如未达到预设值,则进行下一步操作);

5) 判断DDC数据是否写满与SLAVE_FIFO EP6是否为空2个条件是否同时满足。如不满足进入等待状态,如满足进入下一步传输过程;

6) 对SLAVE_FIFO传输次数进行计数,如果计数达到预设值,则计数器清零,跳至步骤4等待下一个换频脉冲。如果未达到预设值,则进入步骤5等待。

5 系统验证

5.1 下变频功能

在测试中,将信号源产生频率为5.001MHz的正弦信号接入接收机中,设置接收机数字本振频率为5MHz正弦信号。接收机采集的数据如下图10所示。

由于本设计采样在第一奈奎斯Nyquist区域即整个系统为低通滤波,根据混频原理,只有频率为1kHz差频信号得以保留。而设计DDC的数据速率为80kHz,即一个DDC信号周期有80个采样点。

如图10所示。单周期采样点个数为80(3329-3249),I(n)和Q(n)两路信号相位相差90°。

5.2 接收机性能

测试条件同下变频功能,在输入信号为接收机灵敏度(-113dBm)时测量1MHz、5MHz、10MHz、15MHz、20MHz、25MHz、30MHz、32MHz的信噪比[SNR]。

根据公式:

[Sin]为接收机灵敏度,本设计中为-113dBm。

接收机在该频点处的噪声系数如下表2所示。

可知,满足设计指标[Nf]≤14dB。

5.3 接收机性能

经测量整个接收机系统功耗小于5W,满足低功耗设计要求。

5.4 电离层斜测数据显示

本接收机采集到的电离层斜测数据绘图如图11所示。

6 结论

本设计应用FPGA完成接系统的控制和数据的正交数字下变频功能。利用KEIL软件对CY7C68013A芯片进行配置完成与上位机之间数据接口的设计并搭配MATLAB软件平台对试验数据进行处理。 验证结果表明,本设计具有设备组成简单、输速率高、功耗低以及体积较小等特点。对于电离层斜测数据的采集方面具有较高的应用价值。

参考文献:

[1] 周文瑜,焦培南.超视距雷达技术[M]. 北京:电子工业出版社出版, 2008: 8.

[2] G. G. Vertogradov,V.P. Uryadov, M. S. Sklyarevsky, V. A. Valov. Oblique Sounding of the Ionosphere by Means of an Ionosonde–Direction Finder with Chirp Signal[J]. Radiophysics and Quantum Electronics, 2017.59 (11):888-899.

[3] 杨小勇,葛彦麟,毛瑞娟.基于 FPGA+A/D 的数据采集设计及验证[J].西安邮电学院学报,2011,16(1): 98-102.

[4] 李俊萍, 靳鸿,张艳兵. 基于 CY7C68013A 的存储器测试台的USB 通信设计[J].电子器件,2014,37(2):361-366.

[5] 黄昌里, 罗玉来, 黄汝言.数字式电离层斜向探测系统[ J] .电波科学学报, 1994, 9(4) :81-88.

[6] 苏涛, 何学辉, 吕林夏. 实时信号处理系统设计[M].西安: 西安电子科技大学出版社, 2006: 5.

[7] 杨小牛,楼才义,徐建良.软件无线电原理与应用 [M]. 北京: 电子工业出版社, 2001: 1.

[8] 丁玉美, 高西全. 数字信号处理[M].西安: 西安电子科技大学出版社, 2000: 12.

[9] 薛小刚, 葛毅敏. Xilinx ISE 9.X FPGA/CPLD设计指南[M].北京: 人民邮电出版社, 2007: 8.

[10] 付斌,丁月寧,黄勇,等.基于 USB 的便携式导弹导航遥测舱数据采集系统设计[J].计算机测量与控制,2014,22(3):790-792.

【通联编辑:梁书】