C波段小型化双通道变频收发模块设计

2020-12-25吴元清解效白朱鸿浩

吴元清,解效白,郭 睿,朱鸿浩

(中国船舶集团有限公司第八研究院,南京 211153)

0 引 言

随着相控阵体制在雷达等军用电子装备中的广泛应用,需要研制生产大量小型化、高密度、多功能的微波模块。这对组装和互连技术提出了越来越高的要求。微组装技术(Micro-assembly Process Technology, MPT)以其高密度、高速度、高可靠性的特点成为了当今军品电子技术发展的主流。它是在高密度多层互连基板上采用微焊与封装工艺把构成电路的各种微型元器件组装起来。由于微组装技术采用的芯片大多为无封装的裸露芯片,较封装芯片而言具有体积小、功能全、集成度高等优点,进而极大地提高了微波模块的集成度。由组装技术发展规律来看,组装密度每提高10%,模块体积可减少40%~50%,质量减少20%~30%。[1]因此,微组装技术对于减小微波功能模块的体积与质量,以及满足雷达装备小型化、轻量化、数字化具有重要意义。本文基于微组装技术研制一款应用于XX项目的C波段小型化双通道收发变频模块。

1 链路主要性能指标设计

模块采用二次变频超外差结构实现射频频率与中频频率的相互变换。模块单通道主要链路框图如图1所示,主要包括环形器、限幅低噪放、驱放、功放、第1次混频多功能电路、第2次混频多功能电路,配以相关的放大器与滤波器。

图1 模块单通道主要链路图

1.1 下行增益与噪声系数设计

射频模块多个芯片级联总增益按下式计算:

GRF(dB)=G1(dB)+G2(dB)+…+Gn(dB)

(1)

多个芯片级联总噪声系数按下式计算:

(2)

下行增益分配时主要考虑链路噪声系数和抗饱和干扰能力,将增益均匀分配在每一级链路中,并在末级使用固定1 dB压缩点的放大器对接收支路的压缩点进行固化。由公式(2)可知,模块第1级电路(环形器)的噪声系数对整个链路的噪声大小起着决定性的作用。为了获得较小的链路噪声系数,模块选取了损耗为0.3 dB的环形器作为系统的第1级电路;吸收式限幅低噪声放大器载片作为系统第2级电路,有着1.2 dB的低噪声系数与28 dB的高增益特性,使模块具有较低噪声系数的同时为后级电路提供了一定增益。为了进一步降低系统噪声系数,在第1次混频前系统增加了一级射频放大器。但是,当混频前射频电路增益过大时(一般不超过35 dB),系统受到的外部干扰将会大大提升,继而损失系统的动态范围。因此,增益、噪声系数与动态范围三者必须折中考虑,选取适合系统的最佳值。此外,中频放大器的噪声系数对链路噪声也有一定影响。设计过程中在保证链路增益设计的前提下需要选择噪声系数相对较低的放大器芯片以降低系统噪声系数。

1.2 带内平坦度设计

模块采用MMIC(微波集成电路芯片)在微波多层混压印制板上实现模块小型化与集成化的特性。考虑到频带内平坦度的要求,通过选取高平坦度芯片以降低带内增益起伏;优选多功能芯片以降低芯片种类,减少由于芯片之间金丝互连的装配误差引起的带内及通道间的增益不一致性。对于基于微组装工艺的模块,模块内环形器、限幅低噪声放大器、驱动放大器以及功率放大器均以焊料烧结的形式与模块壳体直接互连。该互连方式既保证了器件的良好接地性能,对于大功率器件其散热效果也远好于螺钉安装方式。但是,在烧结器件与多层混压印制板互连时金丝互连引入的额外电感易导致传输线失配,继而导致链路带内平坦度的恶化。本节采用三维电磁仿真软件HFSS对烧结器件与微波多层板之间的过渡连接进行建模与仿真优化,如图2所示。

图2 烧结器件与微波多层板间互连三维模型

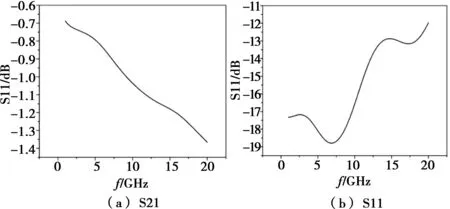

双层印制板选用的是相对介电常数为3.48、厚度为0.254 mm的Rogers 4350B板材。微波多层板选用的8层混压板,其板厚分别为0.254/0.2/0.127/0.12/0.1/0.12/0.254 mm。其中,多层板中第1、2层与第7、8层选取的是厚度为0.254 mm的Rogers 4350B板材,第3、4层选取的是厚度为0.127 mm的Rogers 4350B板材,第5、6层选取的是厚度为0.1 mm的FR4板材。微波信号传输板材与PP片混压成8层印制板,双层板与多层板间采用金丝实现信号互连。全波仿真结果如图3所示。

图3 互连模型S参数

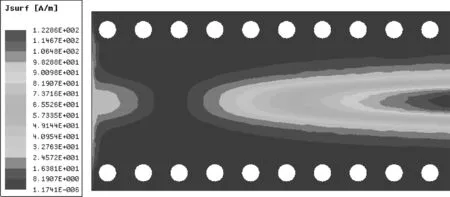

当频率小于7.5 GHz时互连传输性能尚优,而随着频率增加传输性能迅速恶化。图4所示为多层板电流传输性能。多层板回流电流主要通过板边的过孔进行传输,增加了信号回流路径以及平面的寄生电感,导致高频处传输线的互连失配。

图4 多层板电流传输性能

为了改善微波多层板与双层载片互连的传输特性,首先通过在传输线附近引入额外电容以补偿互连时电感失配效应;其次采用板边包金技术,使多层板的回流电流通过良好的宽平面进行传输。优化后仿真模型与电流传输性能如图5所示。

图5 优化后仿真模型与多层板电流传输性能

如图5所示,采用板边包金工艺后电流密度集中在微带线下方直接通过良好的地平面传输,减少了电流回流路径。微带线互连传输优化仿真结果如图6所示。

优化后在DC~20 GHz的频段内插入损耗明显降低小于0.9 dB,在模块需求频段(C波段)插入损耗小于0.3 dB,且带内驻波均小于-20 dBc,有效地提升了传输性能。

1.3 功率输出设计

模块采用3级放大器级联的形式完成模块输出功率大于50 W的技术指标要求,如图7所示。

-2 dBm的射频信号经过衰减器后由第1级驱动放大器饱和放大至21 dBm,第2级驱动放大器由第1级驱动放大器推动饱和放大输出至40 dBm(10 W)。为了改善驱动放大器与功率放大器的级联匹配,选取了输入输出为Langer桥功分合成平衡式功率放大器

图6 优化仿真结果

图7 模块单通道功率放大链路框图

载片。该功放载片无需加入隔离器进行功放输入驻波匹配,节约模块布局空间的同时提高了第2级驱动放大器、功率放大器、环形器三者之间的级联匹配,优化了功率放大器的谐波性能。

模块功率放大链路采用+5 V、-5 V与28 V TTL电源共同供电。为了消除电源级联产生的低频调制信号对主输出功率的干扰,模块对驱动放大器与功放使用的28 V直流信号进行一对一单独调制,实现了高电压电源之间的物理隔离。调制电路具有负电保护功能,避免由于负电掉电后造成功率管的烧毁。对驱放2与功放使用的栅压负电信号,采用栅压稳压芯片对-5 V分别进行稳压,与电阻分压相比能够有效提高栅压的稳定性,从而增加驱放和功放的可靠性。

1.4 组合干扰设计

如图8所示,模块组合干扰主要来源于第1次下(上)混频干扰,第2次下(上)混频干扰以及本振频率间的组合干扰。

图8 模块混频链路图

对于第1、2次下混频干扰与第1次上混频干扰,近端杂散主要由声表面波滤波器、中频带通滤波器进行滤除;对于远端杂散,主要由LTCC低通滤波器与混频器的杂波抑制性能共同抑制。模块采用双平衡混频器,与其他混频器相比具有组合干扰少、噪声系数小、本振与射频、中频隔离度高的优点[2],在后端通过选取合适的滤波器级联可以较好地实现模块带内杂散、镜像频率与中频带外抑制。

对于第2次上混频干扰,通过ADS软件计算,存在2LO1-5IF1杂散落在射频带内。模块选取了对频率为5IF1抑制性能较好的混频1芯片,满足模块带内杂散抑制要求。其余由第1次混频产生的低频杂散、本振频率泄漏与镜像频率,主要由混频器1的杂波抑制性能与选取高选择性的MEMS射频滤波器共同滤除。MEMS滤波器具有高Q值、体积小、易集成与可靠性高等优点。相同结构的MEMS滤波器体积是传统腔体滤波器的1/220[3],有效提升了模块的集成度。

对于下变频本振频率间干扰,通过ADS软件计算,交调信号LO1~5LO2杂散落在中频带内,主要通过混频器1与一中频LTCC低通滤波器对LO1信号共同抑制以降低交调信号干扰。对于上变频本振频率间干扰,存在LO1~LO2信号落在射频带内,无法通过射频带通滤波器滤除。采用声表面波滤波器对LO2信号抑制大于70 dBc,满足模块带内杂散大于60 dBc的抑制要求。

1.5 电磁兼容设计

模块在狭小的空间内完成双通道两次变频上下行发射接收电路,包含射频小信号与射频大功率信号、一中频信号、二中频信号,以及一、二本振信号和来自T/R组件的数字控制信号。其信号种类复杂多样,设计时主要从电源设计、屏蔽设计和滤波设计的方面考虑模块内部的电磁兼容特性:(1)在电源输入处进行滤波,阻止外部干扰信号从电源进入模块;(2)对控制线信号进行RC滤波,防止线间信号相互串扰;(3)发射接收链路分时供电,发射时接收链路数控衰减器全开,避免在大功率信号发射时由于接收链路隔离度不够造成环路自激;(4)一中频、二中频信号分腔设计,本振信号独立隔腔设计,避免不同信号之间的空间串扰;(5)布板电路设计时走线方式上要避免不同信号之间的平行走线,降低走线间的耦合干扰;(6)模块内盖板采用盖板隔墙一体式设计,避免由于加工精度造成模块内部腔体不密闭,继而引起大功率自激震荡;(7)模块内盖板敏感频率与大功率器件上方粘贴吸波材料,有效衰减射频泄漏的能量。

2 实现与测试结果

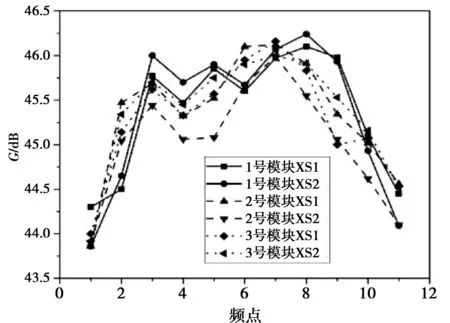

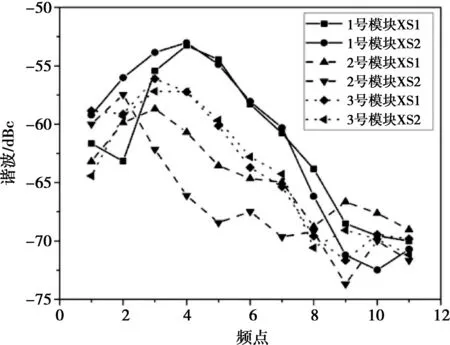

经过对模块的合理布局与设计,模块在55 mm*95 mm*10.8 mm的空间内完成双通道收发变频功能,实物图如图9所示。模块经过高低温、振动实验,测试指标均满足技术指标要求,3只模块6个通道的增益、噪声系数、上行输出功率、二次谐波测试曲线如图10、11、12、13所示。由图10可知,模块增益为45±1.1 dB。根据本文1.2节对模块带内平坦度进行优化。模块下行带内平坦度为±1.1 dB,较模块技术指标±1.5 dB的要求有所提升。模块噪声系数均小于1.7 dB,上行输出功率大于47.6 dBm(55 W),二次谐波抑制大于53 dB,具有一定的设计余量,实测指标均优于技术指标要求。此外,模块在带内杂散抑制可控制在60 dBc以上,带外杂散抑制可控制在65 dBc以上,满足技术指标要求。

图9 C波段T/R模块实物图

图10 增益测试曲线图

图11 噪声系数测试曲线图

图12 输出功率测试曲线图

图13 二次谐波测试曲线

3 结束语

本文介绍了一种基于MMIC与微组装工艺技术的C波段双通道T/R模块的设计方法。MMIC芯片体积小、功能全、集成度高等的优点大大地降低了微波功能模块的体积与质量,有效满足了现代化雷达高密度、轻量化、高可靠性的要求。经过充分的试验验证,模块的性能水平达到了预期的研制目标,满足某C波段旋转相控阵雷达的使用需求。