基于FPGA的激光回波数据采集与传输系统

2020-12-04徐广平张伟健

吴 洋,徐广平,耿 林,张伟健

(华北光电技术研究所,北京 100015)

1 引 言

激光科学技术[1-2]的诞生促进了一批激光领域设备的探索。激光和一般光源相对比,激光具有高亮度、方向性好、单色性好等优点,因此被广泛应用在测距领域。传统的激光测距设备的工作原理是使用激光器将其对准目标后进行操作来发射出一系列的激光脉冲。一段时间后激光脉冲遇到目标反射回来被激光器接收到,然后通过测量激光脉冲到达目标并返射回来被接收设备接收到的回波的往返距离时间差来间接测量出激光器与目标之间的距离[3-4],它没有利用信号的波形信息,本文采用全波形采样的方案,将回波信号采集、传输、存储和处理,可以显著提高接收信号的信噪比,这在半导体远距离测距机中具有明显优势[5],本文内容是这种方案测距机的一部分,主要涉及高速采样、FPGA数据存储、传输等功能。

在信号数据采集系统方面,现场可编辑逻辑门阵列(field programmable gate array,FPGA)与DSP、单片机、CPLD等相比具有以下优点:支持流水线操作,可以同时让多个处理单元工作,可以实现数据采集与实时传输;FPGA 的时钟频率最高可达几百兆,它十分适合作为高速数据采集与实时传输的控制芯片;与其他的可编程器件进行对比可知FPGA还具有很好的灵活性的优势。传统的设计在逻辑接口设计上一般还需要使用相匹配的接口芯片,而这些接口的逻辑设计对于FPGA来说可以通过本身的编程功能来实现,从使得外围电路设计的难度极大的减少。FPGA自身拥有与各种不同级别电平相兼容的特性,因此可以将设计方案的简化变得比较容易并且将设计所存在的无法预知和不确定的风险降到极低的水平。和传统的电平转换器进行比对可知通过使用FPGA芯片能够将电路设计的难度大大在降低。通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART)可以在发送数据时将并行数据转换为串行数据,在接收数据时将串行数据转换为并行数据,并实现全双工发送和接收。UART协议[6]最为基础,电路结构简单、成本也比较低,因此在注重性价比的情况下,UART协议使用极其的广泛。传统的激光测距系统对于回波信号的处理主要是通过模拟电路,然而在信号处理方面模拟电路对于提升测距量程是非常有限的,在远距离测量下回波信号很容易被噪声信号所掩盖无法有效接收到,使得测距量程很难达到更进一步地提升。而采用数字化处理可以增强回波信号的抗干扰能力,更容易达到提升测距量程的目的,数据采集与处理技术则是实现数字激光回波接收的核心部分[7-11]。与传统的激光测距系统相比,使用AD采样芯片可以将模拟信号以更快的速度转化为数字信号,以便于后续使用FPGA对信号进行一系列的自相关与互相关运算和存储处理等操作,来使得激光回波的信噪比可以得到很大的提升,这是传统激光测距系统所无法更进一步达到的,在远距离测量方面由于传统激光测距系统无法更进一步的提高信号的信噪比来滤出回波信号峰值,因此比传统测距系统有更大的发展前途和研究价值。针对激光回波数据采集与实时传输的要求和AD采样芯片的多通道、数据量大、速率快的特点,选用FPGA、FIFO(First-In-First-Out)和RS232接口[12]以Verilog编码进行状态机的设计来搭建数据采集与实时传输系统将回波信息采集存储起来,并对回波信息进行累加平均相关运算以提高信号的信噪比,为后期研究搭建完整的激光测距系统打下基础。

2 系统总体设计

信号前端处理电路限制激光回波信号的幅值在0~1.2 V之间;前端处理电路限幅后的信号经过A/D转换[13],由模拟信号变为数字信号以LVDS[14]形式输出并发送给数据采集和传输系统。数据采集与传输系统以FPGA为控制核心,FPGA内部处理模块提供50 MHz采样时钟、向AD芯片写入配置数据的同时,也接收AD芯片的输出数据并送入到FIFO存储器[15]进行缓存;缓存好的数据由UART异步串行通信RS232总线接口发送给上位机。

3 采集系统的硬件设计

A/D信号采集和数据转换芯片用作数据源,将二进制离散数字信号传递给激光回波数据采集和传输系统。选择Altera公司的EP4CE10F17C8N芯片[16]作为FPGA主控制芯片,它具有丰富的资源可以满足系统设计的需求。ADC 芯片选用的是TI 公司生产的ADC128S102 型 ADC 芯片,该芯片提供一个 12 位采样精度的 ADC 和 8 个模拟输入通道,转换速率最高可达1 Msps,模拟输入信号电压的范围则为0至VA(模拟供电电压)。ADC128S102 对外提供一个标准的 SPI 数字接口,将该数字接口连接到 Cyclone IV E 上,可以通过 Cyclone IV E 来对 ADC128S102进线控制以实现模拟电源到数字信号的转换过程。RS232收发器RS3232,RS232接口作为工业设备的标准接口,目前大多数工业设备中都存在,使用此接口可以实现具有RS232接口的设备的控制。 图1显示了系统的硬件结构图。

图1 系统硬件结构框图

3.1 电源设计

FPGA以及RS232接口芯片的电源电压是3.3 V,锁相环、辅助电压和配置电压是2.5 V,ADC128S102芯片所需要的电压为1.8 V,FPGA核心电压为1.2 V。CH340G是可以用3.3 V或5V 电压供电来实现USB端口转换到串行端口的传输芯片。根据以上所述,本系统要求使用以上提及的四种和其他可能需求的输出电压。于是本系统使用型号为PTH05060W的电源芯片。PTH05060W芯片的输出电压可以在0.8~3.6 V之间进行调节。

3.2 系统通信设计

FPGA对ADC128S102进行配置数据通道的输入,以用于工作方式和芯片的修调。ADC128S102的输出通道的数据则被FPGA所采集。采用12位数据总线与FPGA通信,转换速度为1 Msps。

4 采集系统的逻辑设计

图2是FPGA的内部结构框图。根据功能的不同可分为五个部分:A/D采样控制、FIFO存储缓冲、RS232通信、状态机控制和系统时钟模块。

图2 FPGA 内部结构框图

4.1 基于线性序列机的AD 控制模块

A/D模数转换器采用的是一种低功率损耗的芯片ADC128S102,它是逐次逼近型低功率损耗芯片,用于将已经进行过对比的模拟信号转变成为数字信号。输出的标准值是采用二进制形式来进行表示的。

AD 控制模块的主要作用:对ADC128S102串行写入8路配置数据,速率为1 Msps;接收来自ADC128S102的8路数据;将每个通道接收到的激光回波数据进行串并转换,以8 bit依次并行输出同一个像素单元的数据,每个通道可最多输出 8192个像素单元的数据。FPGA接收的数据进行串并转换后以8 bit输出。利用FIFO将单个像素单元的数据补全至12 bit并在FIFO中暂存,其中高4位默认为0。ADC芯片的控制框图如图3所示。

图3 ADC128S102控制框图

通过ADC芯片的接口时序图,可以按照线性序列机的设计思路来整理得到每个信号发生变化时所对应的时刻以及该时刻计数器对应的值。线性序列机的设计思路就是借助计数器连续进行计数。 当对应于计数值的时间达到设定的要求时,信号将被操作。

4.2 FIFO存储缓冲模块

在FPGA中采用FIFO一般应用于高速异步数据的交互和缓存。FIFO和通用存储器之间的主要不同之处在于,其没有专门的外部读写地址线,这也使得对于FIFO的应用相对容易起来。但是,缺点是只能按顺序写入和读取数据,不可以与普通存储器一样把FIFO写入特意指定的地址之上以供读取的选择。 系统采用的是如图4所示的单时钟FIFO(SCFIFO)。

图4 SCFIFO控制框图

在 FPGA 的控制下从ADC128S102读取到的一连串的数字信号数据,首先被写入到SCFIFO 中,采集完成后从SCFIFO读取数据以 UART 串口波特率将数据依次发送出去直至数据发送完毕为止。ADC128S102的单次读取数据的速度可能很快,但并不是每个时刻都需要采集数据。因此需要将从ADC128S102中采集到的数据首先用 SCFIFO缓存起来,然后再用串口的数据速率较缓慢的发送出去。

在系统设计中所采用的FIFO IP内核是由Quartus II软件供给的免费的已成型内核。该软件可以给使用者供给较为友好的图形操作界面,并且可以很容易地设置其结构以及各种类型的参数。对于已经由软件设计者根据不同功能所生成的FIFO IP内核还可以根据不同系列的Altera器件的结构对其进行有差别化的优化。

系统设计中使用的FIFO IP内核是Quartus II软件提供的自由格式内核。 该软件可以为用户提供友好的图形操作界面,并且可以轻松设置其结构和各种类型的参数。 由软件设计人员生成的FIFO IP内核可以根据不同系列Altera器件的结构进行不同的优化。

这个FIFO IP核是通过Verilog语言进行描述的而且已经提供了几乎大部分的设计所需要的功能。

4.3 UART 异步串行通信RS232发送模块

本系统中使用的UART协议的RS232接口的通信协议必须要用一些硬件才能够加以实现数据传输的功能。在探索阶段所采用的大部分的方法为RS232变换为TTL,这使得数据的转换需要采用SP3232、MAX232或者其他同类型的电平转换芯片才能够实现。其外围电路简单,然而最少需要4个电容才能够正常工作。现在的系统集成度则变得越来越高,DB9的RS232接口占用PCB面积过大,多数系统已经转而采用USB转TTL。用CH340G来实现从USB端口到串行端口的转换,可以用3.3 V或者5 V电压提供电源。它的内部配置有收发缓冲区,并且可以使用硬件全双工串行端口。RS232接口可以由外部电平转换器来供给。CH340G的驱动程序在Windows操作系统下可以模拟标准串行端口,因此一般它无需进行修改就可以与大多数原始串行端口配合使用。图5为串行传输模块的整体框图。

图5 串口发送模块整体框图

4.4 数据采集系统状态机设计

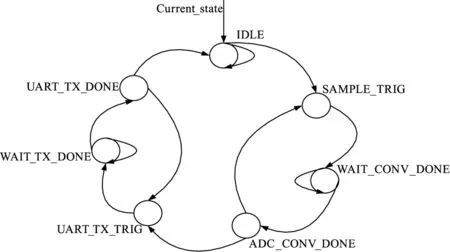

数据采集状态机设计思想为本系统的重点研究部分,状态机用于控制系统的各个模块,将各个模块联结起来。系统使用独热码和一个三阶段状态机进行设计。代码的每个状态都需要使用一个寄存器。只需要一位来比较状态。与其他解码电路相比,它更简单。第一段采用组合逻辑描述状态的转移,此阶段只有状态的跳转,无逻辑的输出,这使得状态机的设计思路十分的清晰。第二段将状态机打一拍,有两个表示状态条件,分别表示当前和下一个状态。第三段为时序逻辑控制所有的输出,并且保证第一段状态跳转的准确度。本系统的状态机设计思路的优点是将状态与输出分开写,更利于软件的分析和综合,能将状态机电路分析优化比较好。与一段式比较减少了软件工作量、运行速度更快、优化的更好。系统状态机跳转的Verilog编写思路则为空闲、连续采集、采集数据完成、串口发送、发送完成5个过程部分:1)空闲状态(IDLE)等待开始按键按下产生key_pressed信号后,才能直接跳转到连续采集状态(SAMPLE_TRIG),否则状态不变。2)连续采集状态(SAMPLE_TRIG)结束后跳转到等待采集完成信号状态(WAIT_CONV_DONE),等待接收到转换完成标志信号(Conv_Done)后,才能直接跳转到采集数据转换完成状态(ADC_CONV_DONE),不满足条件则保持不变。3)采集数据转换完成状态等待累加平均转换完成次数信号sample_times_cnt进入串口连续发送状态(UART_TX_TRIG),否则返回连续采集状态。4)串口连续发送状态结束后跳转到等待串口发送完成状态(WAIT_TX_DONE)。5)等待串口发送完成状态直到接收到一次发送数据完成标志信号Tx_Done后,才能直接跳转到串口发送完成状态(UART_TX_DONE),串口发送完成状态接收到设定的发送次数完成信号Tx_times_cnt进入空闲状态,否则返回到串口连续发送状态。如图6所示为控制状态转换图。

图6 控制状态转换图

4.5 系统时钟模块

以FPGA内部的锁相环来满足整个激光回波数据采集与实时传输系统的时钟需求,系统所提供的时钟是50 MHz。经查阅手册知道器件的工作频率SCLK的推荐范围为0.8~3.2 MHz,在此定义其工作频率为1.92 MHz(周期为520 ns)。并且设置一个两倍于SCLK的采样时钟SCLK2X,使用50 M系统时钟十三分频而来即SCLK2X为3.84 MHz。

4.6 PC程序设计

选择以C sharp语言在Microsoft VS2010中来对PC程序进行设计的,在点击传输的开始按钮后,则会启动数据的接收和存储的线程,数据最终会以文件的形式存储在 PC磁盘之中,流程图如图7所示。

图7 流程图

5 系统仿真实验结果

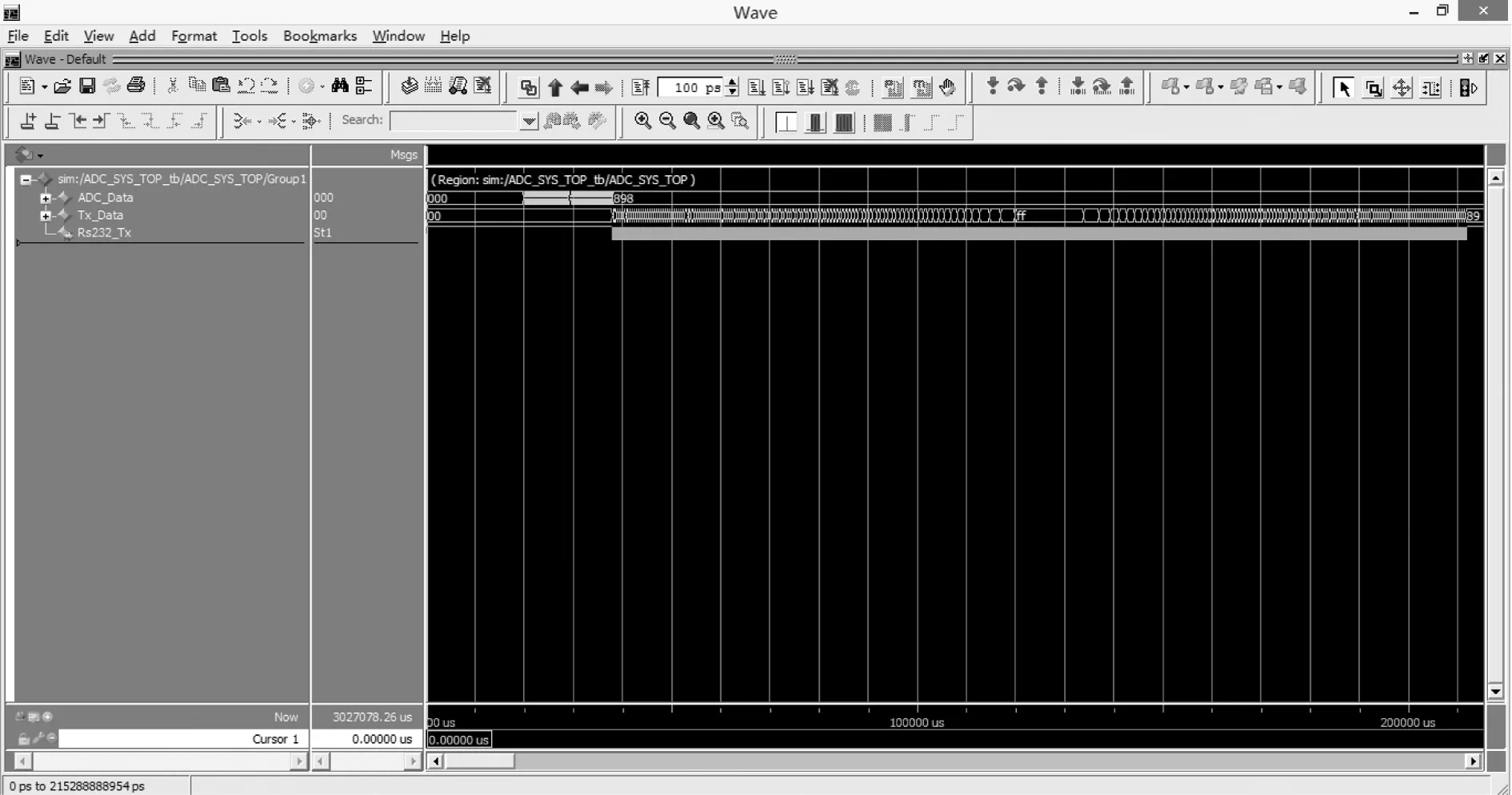

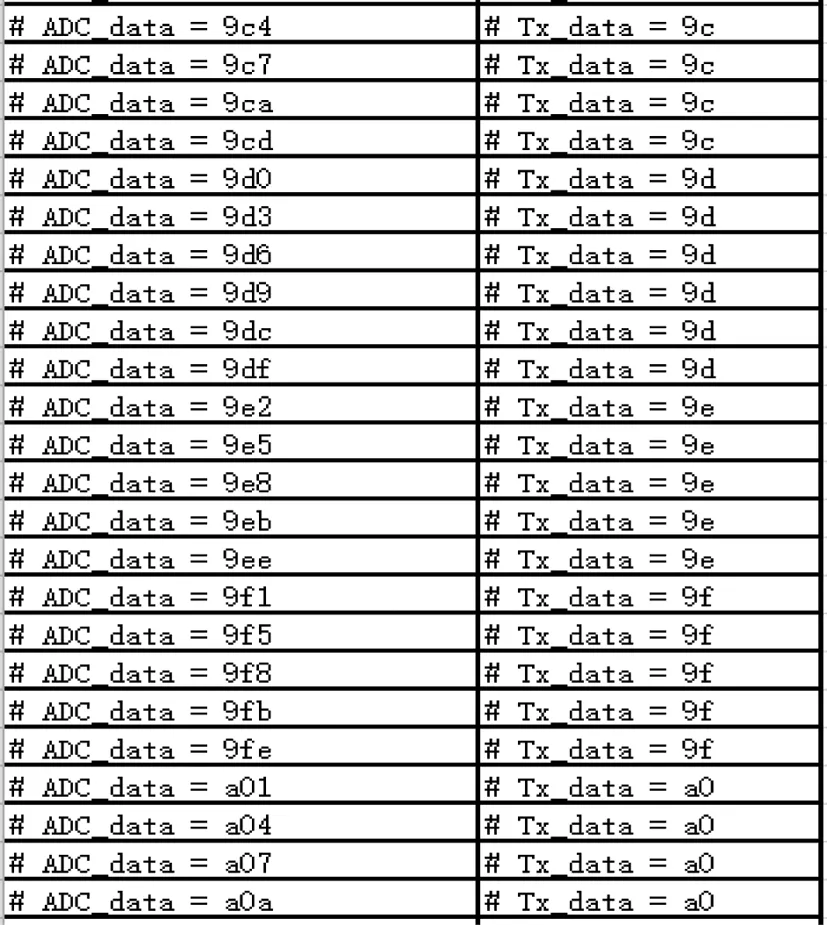

仿真实验采用的软件是ModelSim,实验结果如图8。图中ADC_data信号是AD芯片的12位转换输出数据,传输给FPGA。Tx_data是UART 异步串行通信发送模块RS232接口传输给PC机的8位数据,其中Tx_data截取ADC_data 的高8位数据(Tx_data=ADC_data[11:4])。RS232_Tx是UART 异步串行通信发送模块的输出信号。使用$display()函数将运行数据显示在ModelSim信息窗口,将ModelSim文件下的msim_transcript文件中的ADC_data与Tx_data数据进行比对和分析,没有发现存在误码的情况,图9为选取的部分数据对比表。AD芯片的工作方式正确,配置数据的写入与传输也正确。证明了本文的激光器高速数据采集与传输系统的逻辑的正确性。

图8 仿真实验结果图

图9 部分数据对比表

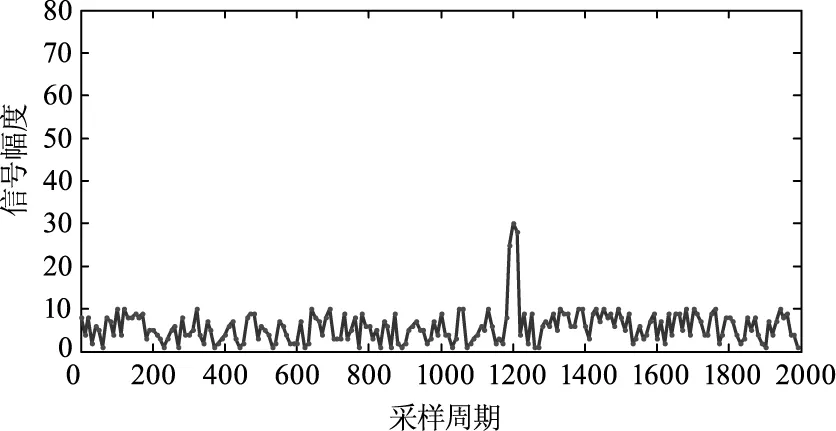

图10 不累加平均波形

图11 累加平均64次波形

6 结 论

介绍了主要以FPGA和FIFO、RS232协议为核心的激光器的回波数据采集与实时传输系统,本设计系统结构比较简单和移植行较好,不仅局限于激光介质还可以采用其他介质进行采集和存储回波的信号,并且具有较高速率、高可靠性、实时性、实用性、准确性较好、成本低等特点,后期可以采用更高速率的AD采样芯片将系统速率进一步提高,以及在远距离测量中加入一些性能更好的信号自相关与互相关算法来更进一步地提高激光回波采集信号的信噪比来更好的提取出信号,使得信号更为准确以便于应用于测距系统之中。仿真测试中未发现有误码现象,表明该系统可以满足激光回波数据采集与实时传输的基本需求,并且可以较好的提取出激光回波波形的信号数据,供后续数据处理部分使用。