FBC 分组密码算法的FPGA 实现*

2020-11-20肖超恩黄胜远李秀滢

肖超恩 黄胜远 李秀滢

北京电子科技学院,北京市 100070

引言

密码算法模块是安全保密系统的重要组成部分,其核心任务是实现重要数据的加解密[1]。分组密码是一种典型的对称密码算法,它采用固定的密码函数,在密钥的控制下对输入的明文消息进行加密得到密文消息,或者对密文消息进行解密得到明文消息,典型的分组密码算法包括美国早期的数据加密标准DES[2]、现行的高级加密标准AES[3-5]、还有我国的商用密码行业标准SM4[6-7]等。 轻量级分组密码是一种特殊的分组密码体制,其主要是指密码算法硬件实现和运行时所占用的系统资源比较少,例如硬件实现资源、运行时所占内存空间大小和能耗[8]等。

为了繁荣我国密码理论和应用研究,推动密码算法技术进步,促进密码人才培养,中国密码学会举办了全国密码算法设计竞赛。 在这次竞赛中FBC 分组密码算法[8]通过了专家组的研究和测试进入了第二轮。 FBC 算法属于轻量级分组密码算法,能够被广泛的应用在密码系统的研制中。 随着电子技术和大规模集成电路的发展,可以通过硬件模块来实现密码算法的功能,有效地避免算法信息外泄的问题,提高加解密的安全性。

为了提高FBC 算法的运算效率,本文基于FPGA 采用状态机设计实现了FBC 算法。 使FBC 算法应用于更多的信息安全应用环境中,满足不同的应用领域需求。

1 FBC 算法简介

FBC 算法属于轻量级分组密码算法,包含FBC128-128、FBC128-256 和FBC256-256 三个版本,分别支持128 比特和256 比特两种明文分组以及128 比特和256 比特两种密钥长度。

FBC 算法采用4 路两重Feistel 结构设计如图1 所示,在结构上通过增加两个异或操作的微小代价提高整体结构的扩散特性。 非线性函数F 用bit-slice 技术[9],其中S 盒基于NFSR 构造,其各项密码学性质达到最优,同时硬件实现代价达到最小,为最轻的S 盒之一;线性变换L 仅由循环移位和异或构成,具有较好的密码学特性的同时兼顾好的软硬件实现效能[10]。 FBC 算法不仅具有结构简洁、轻量化、安全性高等特性,还具有灵活高效的软硬件实现方式,可以满足不同平台的应用需求。

FBC 算法在完成密钥扩展之后,密钥与明文进行子密钥加操作,再进行列变换和行变换,最后输入到加密过程中。 除最后一轮跳过了顺序交换外,其他所有轮的加密过程都进行了顺序交换的操作。

2 FBC 算法的硬件设计实现

根据FBC 算法的原理和基本结构,将整个FBC 算法模块分成4 个相对独立的子模块:输入输出接口模块、控制单元模块、加解密运算模块、密钥扩展模块。 本文设计的密码算法所用的主密钥、明文、密文、控制信号通过输入接口模块由外部输入,加解密运算后的数据经输出接口输出。 结构内部主要信号包括:密钥扩展模块输入信号k0-k3,加解密运算模块输入信号a0-d0和轮密钥k0-k95,加解密运算模块输出信号a48-d48。FBC 算法硬件设计结构框图如图2 所示。

2.1 输入输出接口模块

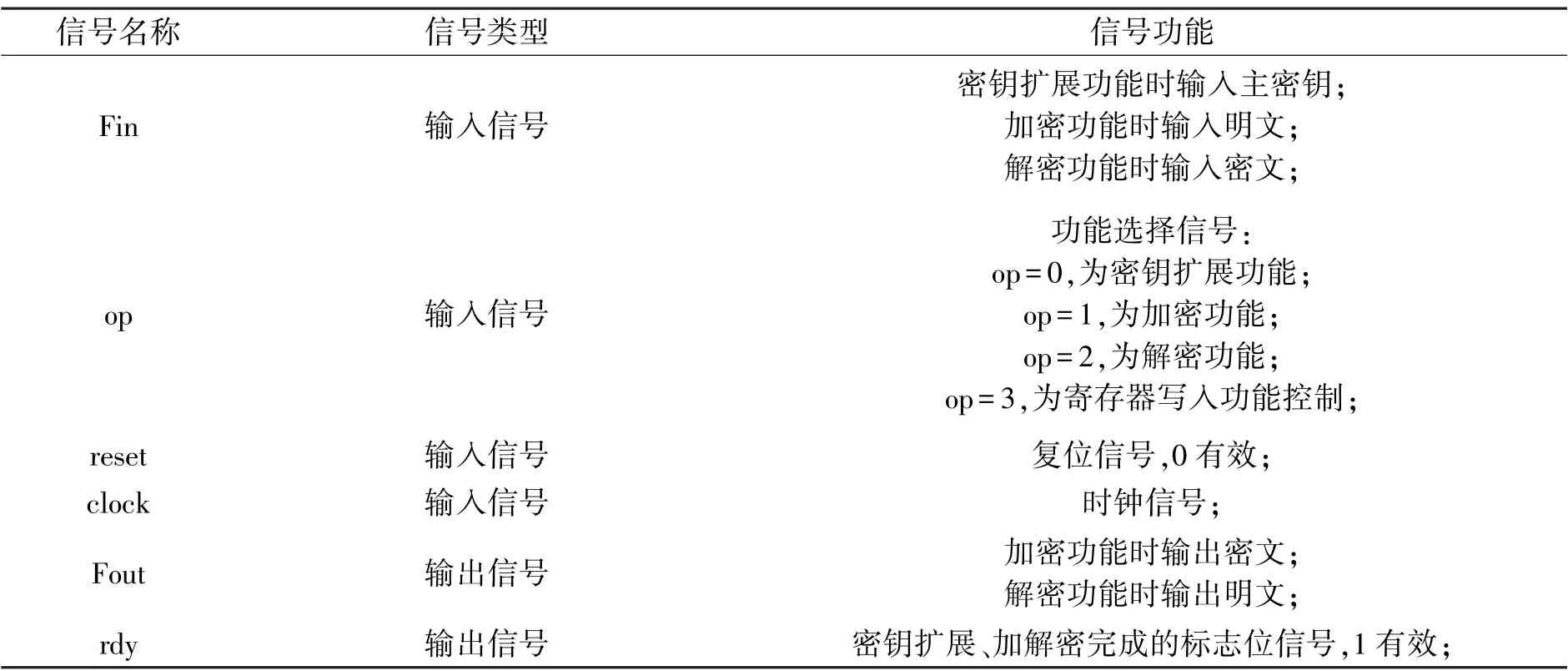

输入接口模块的主要任务是:将明文(密文)传送到加解密运算模块,将主密钥送入密钥扩展模块中。 对明文(密文)和主密钥进行拆分操作,完成小端输入变换。 输出接口模块的主要任务是:输出128 位密文(明文)结果,通过rdy信号反馈密钥扩展、加解密模块完成的标识。 输入输出接口模块的结构图如图3,主要信号及功能如表1 所示。

2.2 控制有限状态机的设计

控制模块的主要任务是实现密钥扩展、加密运算、解密运算等过程的控制,采用的是有限状态机的设计[11],具体状态转换图如图4 所示。其中:

表1 输入输出接口信号及功能

GetReady:准备状态,对输入接口中数据进行预处理;

GetKorD0:密钥扩展状态,进行96 轮密钥扩展,生成96 组轮密钥;

GetKorD1:加密状态1,进行前47 轮加密操作;

GetKorD2:加密状态2,进行最后一轮加密操作;

GetKorD3:解密状态1,进行第1 轮解密操作;

GetKorD4:解密状态2,进行后47 轮解密操作;

GetResult:输出状态,输出结果和状态标识信号。

2.3 轮函数模块的设计

轮函数模块的设计中包含非线性函数F 模块。 非线性函数F 模块的输入包含2 个32 比特的字x 和y,输出为一个32 比特的字z。 其中,x为FBC 算法结构图(图1)中的ai或di,y 为轮密钥k2i或k2i+1。 在轮函数中具有三个过程分别是轮密钥的叠加、列变换和行变换。 非线性函数F模块流程如图5 所示。

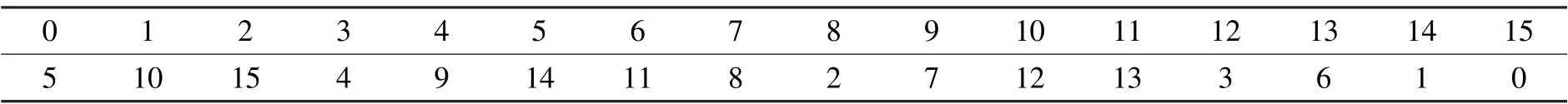

本方案采用并行设计方式,通过组合逻辑电路,非线性函数F 在一个时钟内实现多组数据S盒的处理,极大提高了数据吞吐率,S 盒真值表如表2 所示。 在一轮S 盒处理结束后,将这组处理的数据再次进行拼接整合并存入32 位寄存器v 中。 最后一步采用并行处理的方式,将寄存器v 中的数据分别进行移位,整合输出z。

在完成非线性函数F 的计算之后,结果z 再与上一轮的输出ai、bi、ci、di进行相应运算得到新一轮的ai+1、bi+1、ci+1、di+1。

2.4 密钥扩展模块ExpandKey 设计

表2 S 盒真值表

轮函数加解密运算需要有密钥扩展的支持,而且密钥扩展是整个系统的基础。 密钥扩展的作用就是通过主密钥来进行计算得到加解密需要的轮密钥,FBC 算法的128 位输入和128 位输出模式下,需要扩展出96 组轮密钥来进行加解密操作。 而密钥扩展操作需要对主密钥的四组32 比特的字进行运算。 而首轮密钥扩展则需要将128 比特主密钥分割为4 个32 比特的字k0、k1、k2、k3进行密钥扩展运算。 密钥扩展流程如图6 所示。

算法设计要求密钥扩展进行两步运算,本模块设计采用串行设计,4 组子密钥分别存在4 个32 位寄存器(ki、ki+1、ki+2、ki+3)中,每一次密钥扩展都需要使用当前轮数进行运算,完成运算得到中间态ki+4,在此基础上进行移位和异或操作,得到最终的生成轮密钥ki+4,将轮密钥存入到存器中,迭代生成96 组轮密钥。

2.5 FBC 算法整体流程

根据FBC 分组密码算法的原理和基本结构,FBC 算法整体流程图如图7 所示。 算法开始首先进行工作模式的选择,方案设计三种工作模式分别为:密码扩展、加密和解密工作模式,使算法能够正常工作首先进行密钥扩展流程。 在密钥扩展工作流程中,将主密钥按照算法原理进行拆分,依次迭代生成96 组轮密钥保存到寄存器,最后结束密码扩展工作流程。 加密工作流程中,将明文按照算法原理拆分,依次迭代48 轮加密轮函数,最后生成密文结束。 解密工作流程中,将密文按照算法原理拆分,依次迭代48 轮解密轮函数,最后生成明文结束。

3 仿真验证

根据前述设计思路,系统采用Mentor 公司专门为各逻辑器件制造厂商设计的第三方专用仿真工具ModelSim13.0 进行功能仿真验证。 并使用ISE Design Suite 14.7 软件进行综合测试,分析算法设计性能。

3.1 功能仿真验证

采用FBC 分组密码算法标准测试向量,主密钥“daa69483805fabbd941ad4770a0f37c6”、明文“f01e05ab9863b942f90c9e3c5367918f”和密文“afd197cb7df520ecbdf0fe83e5a79e24”进行功能仿真验证。 进行密钥扩展后加密仿真验证结果如图8 所示、解密仿真验证结果如图9 所示。 从仿真波形图可知,本文设计实现的加解密结果与算法标准测试向量一致。

3.2 算法性能分析

在64bit Windows 环境下,使用Xilinx 公司的ISE Design Suite 14.7 软件工具和Xilinx Virtex 5 FPGA 芯片(XC5VFX100T)对FBC 算法的加密速率和资源利用进行了综合测试。 算法硬件实现性能如表3 所示。 加解密速率=200*128/(48+1)= 522Mbps。 从表中可知,在相同系列FPGA 芯片同样时钟约束下,本文加解密速率与算法作者相同,但是资源占用面积方面减小了5901 个LUTs,减小了约46.48%的资源使用。

表3 FBC 算法硬件实现性能分析

4 结语

研究了FBC 算法的FPGA 设计与实现,整个算法设计按照FPGA 的设计流程,采用了自顶向下的设计思想,使用了状态机的结构,对系统接口及模块进行了独立设计,使算法设计更加高效。 在非线性函数F 的设计中,使用了查找表方法设计和逻辑运算的方式来实现S 盒。 最后,本设计的综合报告反映出了本方案占用的逻辑资源更少,更加适合轻量级密码算法的工程应用。