基于FPGA的直方图均衡图像增强算法设计及实现

2020-11-13焦慧华

焦慧华

(琼台师范学院,海南 海口 571127)

关键字:图像增强;FPGA ;直方图均衡;实时处理

一、图像增强概述

图像增强是按特定的需要突出一幅图像中的某些信息,同时削弱或去除某些不需要的信息的处理方法,也是提高图像质量的过程[1]。图像增强的目的是使图像的某些特性方面更加鲜明、突出,使处理后的图像更适合人眼视觉特性或机器分析,以便于实现对图像的更高级的处理和分析。

目前图像增强处理的应用已经渗透到航空航天、军事侦察、医学诊断、卫星图片的处理等领域。如恶劣天气下飞机的视景增强系统,需要采用图像增强处理方法克服因光线不足、沙尘、烟雾等原因带来的图像模糊,从而为飞行器提供可视化导航。还有对不同时间拍摄的同一地区的遥感图片进行增强处理,侦查是否有敌人军事调动或军事装备及建筑出现。图像增强技术的快速发展同它的广泛应用是分不开的,在未来社会中图像增强技术将会发挥更为重要的作用。

二、直方图均衡算法原理

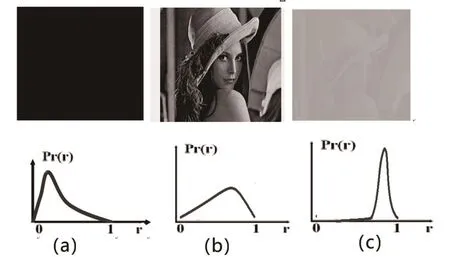

直方图描述了一幅图像的概貌,简单讲,灰度级直方图就是反映一幅图像中灰度级与出现这种灰度的概率之间的关系图。设变量R代表图像中象素灰度级,在图像中,象素的灰度等级可作归一化处理,这样,R的值将限定为0≤R≤ 1。对于一幅给定的图像而言,每一个象素取得[0,1]区间内的灰度级是随机的,也就是说,R是一个随机变量。假定对每一瞬间它们是连续的随机变量,那么,就可以用概率密度函数来表示原始图像的灰度分布[2]。如果用直角坐标系中的横轴代表灰度级R,用纵轴代表灰度级的概率密度函数,这样就可针对一幅图像在这个坐标系中作曲线来。这条曲线在概率论中就是分布密度曲线。不同灰度图像的直方图分布如图1所示,其中,图(a)图像亮度很低,基本分不清其中的图形信息,所以直方图分布都偏向低的灰度;图(b)图像信息清晰,层次分明,所以直方图分布比较均匀;图(c)图像偏亮,但是对比度很低,看不清图像。其直方图分布就是在比较窄的一条带上。

图1 灰度图与灰度直方图示意

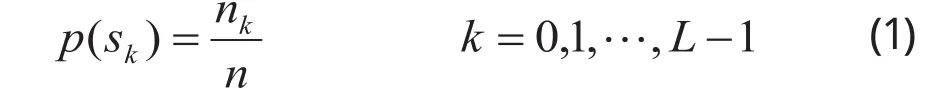

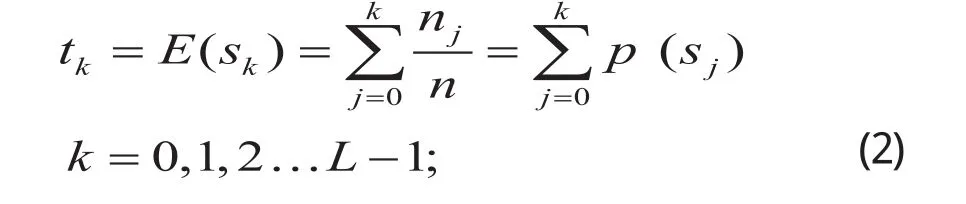

对于实际灰度图像而言,直方图统计分布就是上述灰度概率密度函数的离散化。设图像总的灰度等级为L,图像F(X,Y)的总像素数为N。则图像的灰度统计直方图可以用下面离散函数表示 :

三、基于FPGA的直方图均衡算法设计及实现

(一)直方图均衡算法设计

为了使设计达到实时图像增强的要求,同时考虑到FPGA硬件特点,设计中对算法进行如下处理:

为了保证图像的实时增强,首先在接受图像数据时,计算此场的直方图,由于在FPGA内计算小数通常比较复杂,而且特别消耗逻辑资源,对直方图统计采取的优化如下:

得到累加直方图后,最后将对应的累加直方图转换为直方图映射关系表,转换关系如下式所示:

(二)直方图均衡算法实现框图

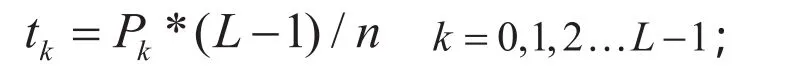

由直方图均衡算法原理,可将FPGA算法实现分为如下3个模块:

1.直方图统计模块 2.直方图累加模块 3.直方图映射模块

视频图像处理时,在场有效期需完成直方图的统计并存储图像数据,场消隐期完成直方图均衡化[5]。最后将存储的图像数据根据均衡化结果映射输出得到增强图像。根据视频图像相邻两帧直方图的高度相似性特点对算法进行改进,在实现视频图像直方图均衡化算法时,将前一场图像直方图统计和均衡化结果作为当前场图像的映射数据输出。以上方法避免了外部存储器的频繁读写操作,简化了系统结构和逻辑设计的复杂度,节省了处理器和存储器存取数据时间,同时节约了视频图像处理系统存储器部分的硬件成本。改进算法的逻辑框图如图 2所示。

图2 直方图均衡算法逻辑框图

首先由直方图统计模块统计完一场图像的直方图后,在场复位未到的时间段里生成直方图均衡映射表,并对直方图缓存双端口RAM和直方图双端口RAM进行清零,在采集完一帧图像后剩余场消隐期的时间生成直方图均衡映射表,映射表生成模块时钟为像素时钟的2倍。设计中利用帧同步信号同步直方图均衡映射表生成模块,驱动时钟为像素时钟,在接受模块统计完一帧图像数据后发一脉冲通知直方图均衡映射表生成模块开始工作,直方图均衡映射表生成模块依次从0到255地址读取直方图双端口RAM中的直方图并累加存入均衡映射表中,读完256个地址后生成直方图均衡映射表,然后通知直方图统计模块对对直方图缓存双端口RAM和直方图双端口RAM进行清零。经过上述处理后,输出的图像数据就是已经经过直方图均衡化后的图像数据,同时将视频同步信号一起同步输出。

(三)直方图均衡的FPGA模块设计

上述FPGA直方图均衡算法主要包括三个模块:直方图统计模块、直方图累加模块和直方图映射模块。下面简要介绍三个模块的实现方法。

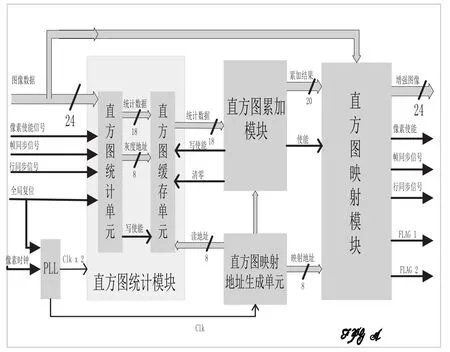

1.直方图统计模块的实现

按照优化的算法的第一步是在FPGA中实现直方图统计,通常在计算机或者DSP上实现时,我们会使用数组结构,但是在FPGA中定义数组是非常消耗资源的,尤其是当数组成员的位宽很大时。而FPGA 器件提供了一个很好的结构,可以处理这类问题,就是Block RAM。在FPGA 器件上都集成了片内存储器,本设计把这种RAM设计成双端口方式,如图3所示,便于直方图统计的实现。

图3 直方图缓存双端口RAM

图4 直方图统计模块实现结构

直方图统计要求对每个像素值出现的次数进行统计,因此可以设计一个256 × 18 bit的双端口RAM作为直方图寄存单元。将输入的像素值作为双端口RAM的写入地址,每次对相同的像素出现的次数进行加1,所以要在每次写RAM之前首先将RAM中的暂存的数据读出,并进行加1处理,然后再写入到RAM中。其实现的逻辑结构如图4所示。

图中另外一个双端口RAM2是用来保存直方图最后统计结果的寄存器。

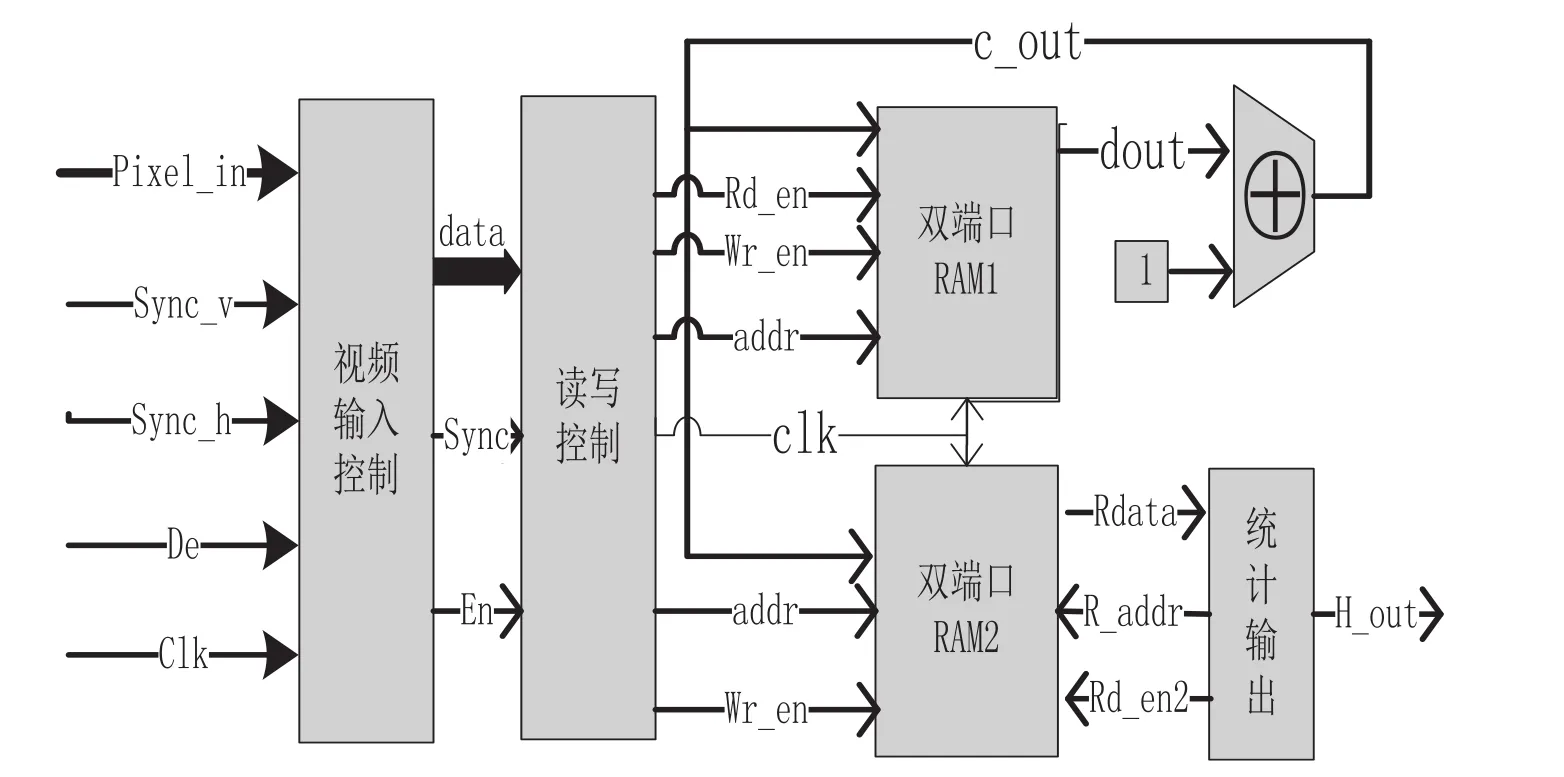

2.直方图累加模块的实现

当直方图统计结束后,需要对直方图统计结果进行累加求和。并将累计结果作为均衡化处理的依据,所以需要将每次累加的和保存在另外一个双端口RAM中。累加的过程是从上面直方图统计模块的双端口RAM2中,依次读出每个数据,并进行累加,累加结果同时存入双端口RAM3中。累加操作是在场消隐期进行,所以每次累加结束后要用场同步信号进行复位。累加操作是由FPGA中的累加器实现。模块的逻辑框图如图5所示。

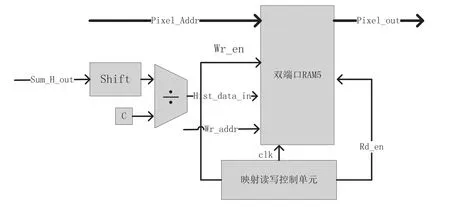

3.直方图映射模块的实现

由前面算法优化可知,在进行直方图映射之前需要对累加直方图的结果进行乘法和除法运算。若直方图均衡图像大小为1024×768像素,而像素级数为256级。所以代入前面算法可知,要对直方图累加结果乘256再除1024×768。经过简化可以将累加结果向低位移10位再除以3,得到的结果便是直方图映射后的像素值。根据上述分析,直方图映射模块可以由如下模块实现,如图6所示。

图6 直方图映射模块实现结构

四、直方图均衡算法仿真与验证

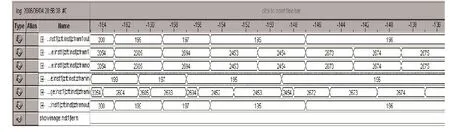

本文采用VHDL设计完成各个模块后,在Quartu II中进行编译,并下载在ALTERA的开发板中进行实验验证,使用Quartus II中SignalTap II逻辑分析仪对直方图数据和均衡表的数据进行观察,表明了进行直方图统计的过程及均衡后的结果,图7为直方图统计的采样波形,其中zfram1out和zfram1为写入直方图双端口RAM中的地址和数据,由实际采样数据可以看出,当写入地址为连续3个196时,写入的数据在进行递增,表明直方图统计正确。 zframo和zframout分别是写入直方图缓存中的数据和地址,在zframin灰度地址为197时,读出的像素数zframi为2693,经直方图统计模块加一后输出zframo像素数为2694。说明直方图统计正确。

图7 SignalTap II直方图统计过程

在算法仿真验证正确后,将主机显卡实时送出一副1600×1200的图像,刷新率设置为60HZ,并将输出连接至开发板的DVI输入端口,输出DVI端口连接另一显示器,图8分别为原图和经FPGA直方图均衡增强后效果图,与原图相比可以看出,直方图均衡增强后的图像展宽了频带,图像的细节更加丰富。

图8. 原图和经FPGA直方图均衡增强后效果图

五、结语

通过上述的设计与验证,采用FPGA实现了实时图像的直方图增强。并且结合FPGA高速并行特性,设计了基于FPGA的视频数据流的直方图增强算法。目前该算法支持分辨率最高达到1600×1200的高分辨率实时视频处理,处理速度在60帧/S以上,可以满足高清视频的实时增强处理要求。该直方图增强方法特别适合于在低照度条件下的视频增强处理,以便获得实时的增强效果。