高精度微弱磁场信号采集系统的设计与实现

2020-11-05葛丽丽任琼英赵华李涛李昊

葛丽丽,任琼英,赵华,李涛,李昊

(北京卫星环境工程研究所,北京100094)

0 引言

随着磁场探测技术的发展,微弱磁场测量成为研究物质特性、探索未知世界的有效手段之一,广泛应用于水下通信、空间磁场探测、水中磁性目标探测、水下警戒与安全防护、地质勘探等军事和民用领域,并取得了丰硕成果[1-3]。目前,随着各种新技术、新材料的发展和应用,微弱磁场测量技术不断发展进步,磁强计种类日益丰富,磁场测量精度也不断提高,常用的磁通门磁强计、磁阻磁强计的测量精度已可达到10-11T量级。而这类磁强计的数据存储和信号处理需要依靠模/数转换器(ADC)来完成,要实现高精度的微弱磁场信号测量则须选用高分辨率的ADC[4-6]。

ADC的作用是将在时域和幅值上都连续变化的模拟信号转换为时域上离散、幅值上量化的等效数字信号[7]。当分辨率很高(16 bit 以上)时,由于前端需要设置抗混叠滤波器、采样/保持电路,增加了采集系统的复杂度,使得传统的奈奎斯特速率ADC的测量精度受限;而Σ-Δ 模/数转换采用过采样技术,对输入的模拟信号以高于奈奎斯特频率若干倍的频率进行采样,随后进行低比特量化,再将这种高采样率、低分辨率的数字信号经数字抽取滤波器进行抽取滤波,最终获得以奈奎斯特采样频率输出的高分辨率数字信号。因此,可以在数字域中适当地运用信号处理技术,以降低对模拟器件匹配精度的要求,从而使Σ-Δ型ADC广泛应用于音频、先进传感器、无线通信等传统领域以及生物医疗和能量采集系统等新型领域[8-10]。

为提高微弱磁场信号的测量精度,要求所选用的ADC位数多、采样精度高,以降低数字采样系统对微弱磁场信号的干扰。例如:在量程为±65 000nT时,若要求分辨率达到0.1 nT,经过计算,所选用的ADC的位数要达到21 bit。综上,Σ-Δ 型ADC更适用于高精度微弱磁场信号采集。

本文设计的基于Σ-Δ 型ADC的高精度微弱磁场信号采集系统,以FPGA 为系统控制器来实现6路高精度微弱磁场信号的采集。主要研究内容包括:系统硬件电路设计;FPGA 对ADC工作流程的控制;ADC输出数据的接收和发送等。

1 系统设计

1.1 关键器件选用

系统的核心控制器选用的是Actel 公司的军用ProASIC3/EL 系列,其功耗较低,是基于可重复编程的Flash 技术的FPGA(A3P1000FG144),系统门级为100万,Flash ROM 存储量为1kbit,RAM存储量为144kbit,支持高达350MHz 的内部时钟频率[11]。

为实现高精度微弱磁场信号的采样,系统选用24位Σ-Δ 型ADC(AD7710)为其6路模/数转换芯片。该芯片集成度高,具有片上微控制器、时钟振荡器、数字滤波器和双向串行通信接口;包含2个增益可编程的差分模拟输入通道,可直接接收来自传感器的模拟量输入;数据的输出可以满足多种符合工业标准的微处理器的串口通信要求,灵活性高;可通过写入控制字方式实现对内部数字滤波器截止频率、增益以及失调量的校准等的软件控制[12]。

1.2 系统硬件电路设计

系统的硬件电路设计框图如图1所示:输入端为6路微弱差分磁场信号,输出端为全双工异步RS422总线接口以及系统的温度和电源状态遥测输出信号。6路微弱差分磁场信号由FPGA 控制6个ADC进行转换。FPGA 不仅控制ADC的工作模式,还负责接收和处理ADC 所输出的等效磁场数字信号。此外,由于FPGA 和ADC 之间逻辑电平不协调,还需要由电平转换芯片进行协调,电平转换芯片的使能和方向控制也均由FPGA 完成。采样数据由RS422驱动器发送。FPGA 的40MHz 晶振供电电压为3.3V,ADC的供电电压为5V,时钟频率为10MHz。

图1 系统硬件电路设计框图Fig.1Block diagram of system hardwarecircuit design

为了提高信号采集的准确度,本设计除了采用高采样位数、高分辨率的ADC外,还采用6路ADC同步采样模式来减小采样误差,因此在布局布线时,需保证FPGA 到6路ADC的控制信号及主时钟信号均采用等长线。

1.3 FPGA 主要功能设计

FPGA 采用自上而下以及模块化的设计原则,顶层文件和下层各模块均采用Verilog 语言设计输入。根据系统的实际需求,将FPGA 的主要功能模块划分为复位信号产生模块,时钟信号发生模块,ADC控制、接收、缓存处理模块以及串口通信模块,如图2所示。其中,复位信号产生模块利用电路复位按键和上电期间产生的低电平为FPGA、6个ADC以及RS422型线驱动器等芯片提供复位脉冲;时钟信号发生模块利用外部晶振提供的时钟源进行分频,为各功能模块提供合适的时钟信号,包括6个ADC 所需的读/写操作的时钟信号以及RS422串口通信时钟信号;ADC 控制、接收、缓存处理模块负责配置6个ADC的寄存器,控制其进行采样工作,并同步读取各ADC 输出寄存器的采样数据,完成串/并转换并缓存;串口通信模块用于将缓存的数据按照RS422总线接口格式要求输出。

图2 FPGA 主要功能模块Fig.2Main functional modulesof FPGA

1.3.1ADC 工作流程的控制

ADC的配置是通过写控制寄存器来完成,写入控制寄存器的24 bit 将决定ADC的下一步操作。6个ADC同步采样方式的操作流程为:芯片上电复位后,进行芯片系统自校准操作,完成后进行6个ADC的系统同步操作,最后写控制寄存器确定ADC的输出数据速率为30Hz,时钟源为外部时钟,极性模式为双极性,选择增益为1,选择模拟通道1,字符长度为24 bit 等信息,控制6个ADC芯片进入采样模式,同时读取输出寄存器串行输出的磁场采样数据。

1)ADC的读控制

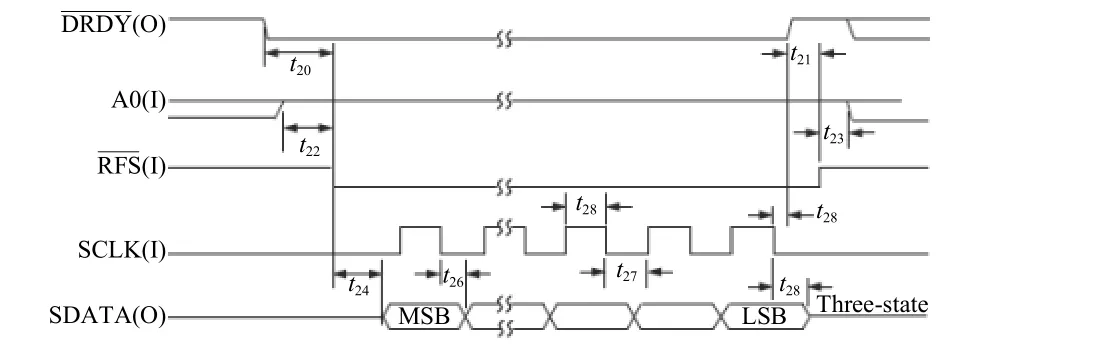

FPGA 同步读出6个ADC的输出寄存器,读取方式为1次“读”操作读取输出寄存器全部24 bit数据。图3为ADC的1次输出数据“读”操作时序图:在数据传输中,“读”有效信号RFS必须保持低电平;当输出信号DRDY 变成低电平时,RFS也变成低电平;在“读”操作和“写”操作之间,SCLK 必须是低电平;当RFS变成低电平时,将串口与MSB(最高位)连接起来,所有的数据将从高到低传送,在最后1位数据输出后,时钟输出最后1个高电平脉冲,当转为低电平时,将使DRDY变成高电平,其上升沿将关闭串口。

图3 外部时钟模式输出数据“读”操作时序Fig.3The Read operation sequence of output data in external clock mode

2)ADC的写控制

同样的,FPGA 在写6个ADC的控制寄存器时也采用1次“写”操作的方式。在对控制寄存器进行“写”操作过程中,不会对DRDY有任何影响,DRDY也不会影响“写”操作。“写”操作时输入的数据必须是24bit 的。图4为控制寄存器“写”操作时序图:在“写”操作过程中,A0必须一直保持有效,并决定是对控制寄存器还是对校准寄存器进行“写”操作;“写”有效信号TFS应为低电平;在外部时钟SCLK 为高电平时,ADC输入的数据必须有效;数据从高位到低位传输。

1.3.2ADC 的数据接收和发送

FPGA 对6个ADC输出寄存器的采样数据分别进行缓存,数据存储之前须首先完成一系列转换工作。ADC 输出寄存器由高位到低位串行输出采样数据,因此在串/并转换的同时还要完成高/低位转换,最终将6个ADC的采样数据转换为24bit并行数据并分别缓存。

缓存的数据经由RS422串口驱动器进行发送。每个采样周期转换完成的6个ADC采样数据按照ADC1、ADC2、ADC3、ADC4、ADC5到ADC6的顺序依次发送,采样数据前面加上16 bit 固定标识和8bit 循环累加计数,共同组成1个数据包,共计256 bit。对于每个数据包,串口通信按照RS422总线接口格式要求顺序发送,串口通信速率为115.2kbit/s,奇偶校验位采用奇校验。

2 系统性能测试分析

高精度微弱磁场信号采集系统设计完成后,进行了采样测试,选择采样频率为30Hz,极性模式为双极性,增益为1。测试过程将A/D转换的模拟信号差分输入端短接后与ADC的参考地接通。上电采样一段时间后,进行采样测试,利用串口RS422将采样数据传输到电脑端,并进行相应数据转换,如图5所示。结果显示,该系统的有效位数基本能够接近理论值(21 bit)。

图6 信号采集系统采样测试结果Fig.6System sampling test results

3 结束语

本文设计的基于Σ-Δ型ADC的高精度微弱磁场信号采集系统,采用FPGA 作为系统的核心控制器,对6路AD7710进行控制,实现微弱磁场信号采集。系统设计实现后进行性能测试表明其能满足微弱磁场测量的高精度要求。同时,本信号采集系统选用军品器件,采用轻小型设计,模拟输入接口适应性强,可以做到通用化。