基于DS100MB203的高速信号开关电路设计

2020-10-26陈旭

陈 旭

(北京航天创智科技有限公司,北京 100089)

0 引 言

现代数字信号系统对信号传输速率的要求越来越高。电路设计中,前期大多采用并行总线传输的方式实现高速数据传输,但并行总线需要大量的数据线、地址线和控制线,并且对时钟同步、对走线等长都有较高要求,增加了电路板的尺寸和布线难度[1]。因此,近些年以SerDes为代表的串行传输方式逐步占据主流。

相对于并行传输技术,串行传输技术的引脚数量少、扩展能力强,采用点对点的连接方式,能提供比更高的带宽,因此广泛用于嵌入式高速传输领域。SerDes(Serializer-Deserializer)是串行器和解串器的简称,串行器(Serializer)为SerDes发送端(Tx),解串器(Deserializer)为接收端(Rx)[2]。SerDes不传送时钟信号,SerDes在接收端集成了CDR(Clock Data Recovery)电路,利用CDR从数据的边沿信息中抽取时钟,并找到最优的采样位置。SerDes采用差分方式传送数据。SerDes需要参考时钟(Reference Clock),一般也是差分的形式,以降低噪声[3]。

在高速数据传输应用中,许多场合需要将一路SerDes信号通过选择开关分别连接到2台设备上,然后通过控制信号,使得SerDes信号在某一时刻与其中一台设备连通。本文介绍的高速信号开关电路,使用TI公司的DS100MB203实现选择开关功能,能够实现数据传输速率高达10.312 5 Gb/s的信号切换。同时,该电路具有去加重和均衡功能,能够在传输信号的同时提高信号的传输质量。

1 开关电路设计

1.1 DS100MB203内部组成

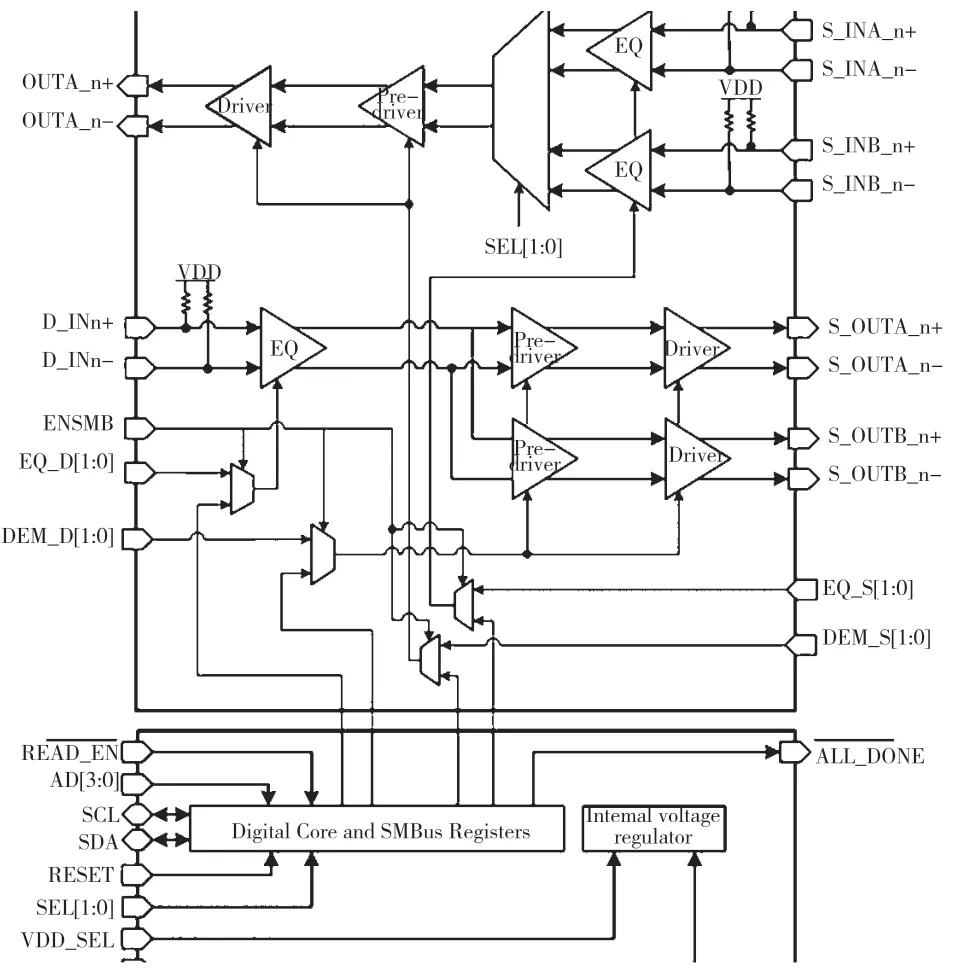

DS100MB203由TI公司推出,支持速率高达10.312 5 Gb/s的高速信号切换开关芯片。每片DS100MB203支持两路serdes信号,工作模式有I2C配置模式和管脚控制模式,功耗仅390 mW,是一款应用广泛的高速信号开关芯片[4],如图1所示。

DS100MB203共有54个管脚,管脚功能如下所述[4]。

(1)D_IN0+/-和D_IN1+/-为芯片一分二通道选择开关的输入端,是CML差分信号,芯片内置50 Ω上拉电阻,输入到该管脚的信号需要通过交流耦合的方式连接;D_OUT0+/-和D_OUT1+/-为芯片二选一通道选择开关的输出端,电平标准也为CML差分信号,差分阻抗100 Ω。

图1 DS100MB203内部组成示意图

(2)S_INA0+/-、S_INB0+/-及S_INA1+/-和S_INB1+/-分别为两路二选一通道选择开关的输入端,是CML差分信号,芯片内置50 Ω上拉电阻,输入到该管脚的信号需要通过交流耦合的方式连接;S_OUTA0+/-、S_OUTB0+/-及S_OUTA1+/-和S_OUTB1+/-分别为两路一分二通道选择开关的输出端,是CML差分信号,差分阻抗100 Ω。

(3)ENSMB为工作方式控制管脚。当上拉为高电平时,工作模式为I2C从模式;当悬空时,工作模式为I2C主模式;当下拉到低电平时,工作模式为硬件管脚控制模式。

(4)RESET为复位管脚,低电平复位。

(5)VDD_SEL该管脚选择芯片的工作电压,悬空时为2.5 V供电模式,下拉为低电平时,工作电压为3.3 V。

(6)AD0-AD3为工作在I2C模式下I2C的设备地址。SCL为I2C时钟管脚,SDA为I2C数据信号管脚。

(7)INPUT_EN为输入使能信号。该信号为0时,FANOUT功能禁用,通过SEL0/1来选择输入输出通道;该信号为1时,FANOUT功能起作用,S_OUT0/1均有输出。

(8)MODE信号选择工作模式,为0时支持传输SATA/SAS、PCIe GEN 1/2和10GE协议信号;悬空时,为自动模式;为1时,支持传输10-KR协议信号。

(9)SEL0和SEL1在硬件管脚控制模式时,分别是LAN0和LAN1的通道选择管脚;当SEL0为低电平时,S_INB0作为输入,S_OUTB0作为输出;当SEL0为高电平时,S_INA0作为输入,S_OUTA0作为输出;当SEL1为低电平时,S_INB1作为输入,S_OUTB1作为输出;当SEL1为高电平时,S_INA1作为输入,S_OUTA1作为输出。

(10)ALL_DONE管脚为输出管脚,为0时标志外部EEPROM加载成功,为1时标志加载失败。

(11)在管脚控制模式时,DEM_S0、DEM_S1、DEM_D0和DEM_D1可以设置芯片输出信号的预加重参数,EQ_D0、EQ_D1、EQ_S0、EQ_S1可以设置芯片输入信号的均衡调节参数。

1.2 开关电路连接

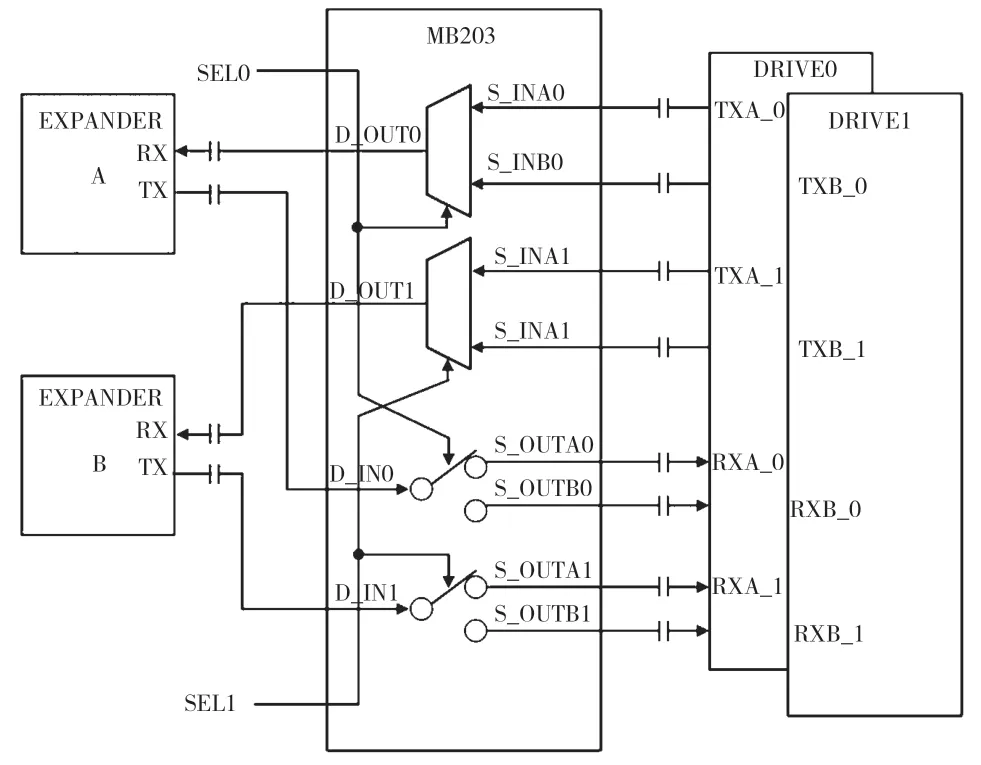

如图2所示,一片DS100MB203芯片可以作为两路SerDes信号的选择开关。两路SerDes分别定义为LANE0和LANE1,芯片左侧定义为D端,右侧定义为S端。设备A的发送信号TX接到LANE0的D_IN0上。I2C模式时,通过I2C总线配置或在管脚控制模式时,通过控制信号SEL0,可以选择D_IN0和S_OUTA0或S_OUTB0连 通。DRIVE0和DRIVE1设备的发送端TXA_0和TXB_0分别接到DS100MB203的S_INA0和S_INB0管脚上,同样通过I2C总线对寄存器配置或通过控制信号SEL0来选择其中一路与D_OUT0连通。B设备和LANE1的连接方式与A设备和LANE0的连接方式一致[5]。

图2 高速信号开关电路图

DS100MB203芯片不仅能够实现高速信号的通道切换,而且具有增强高速信号的驱动能力,同时通过去加重和均衡技术改善信号质量。

1.3 去加重和均衡功能

在高速信号传输中,信号质量主要受到传输线分布参数、介质损耗以及趋肤效应等影响。一般来说,高频信号分量衰减较大,低频信号分量衰减较小。改善信号质量的方法主要包括在发送端进行的信号预加重和去加重,以及在接收端对信号进行均衡处理。

DS100MB203该芯片具备对发送信号去加重以及对接收信号进行均衡处理的功能。去加重技术是高速信号传输中应用广泛的一种信号质量改善方式,基本思想是减弱信号的低频分量,对信号的高频分量部分保持不变[6]。增加信号上升沿和下降沿出的信号幅值,其他地方幅值保持不变。均衡技术主要在信号的输入端实现,实际效果相当于高通滤波器。高速信号传输中,高频信号分量衰减大,低频信号分量衰减小。均衡器作为高通滤波器,通过均衡器后,低频信号分量衰减大,高频信号分量衰减小,正好补偿了传输过程中的损耗,因此能够保证信号不失真。

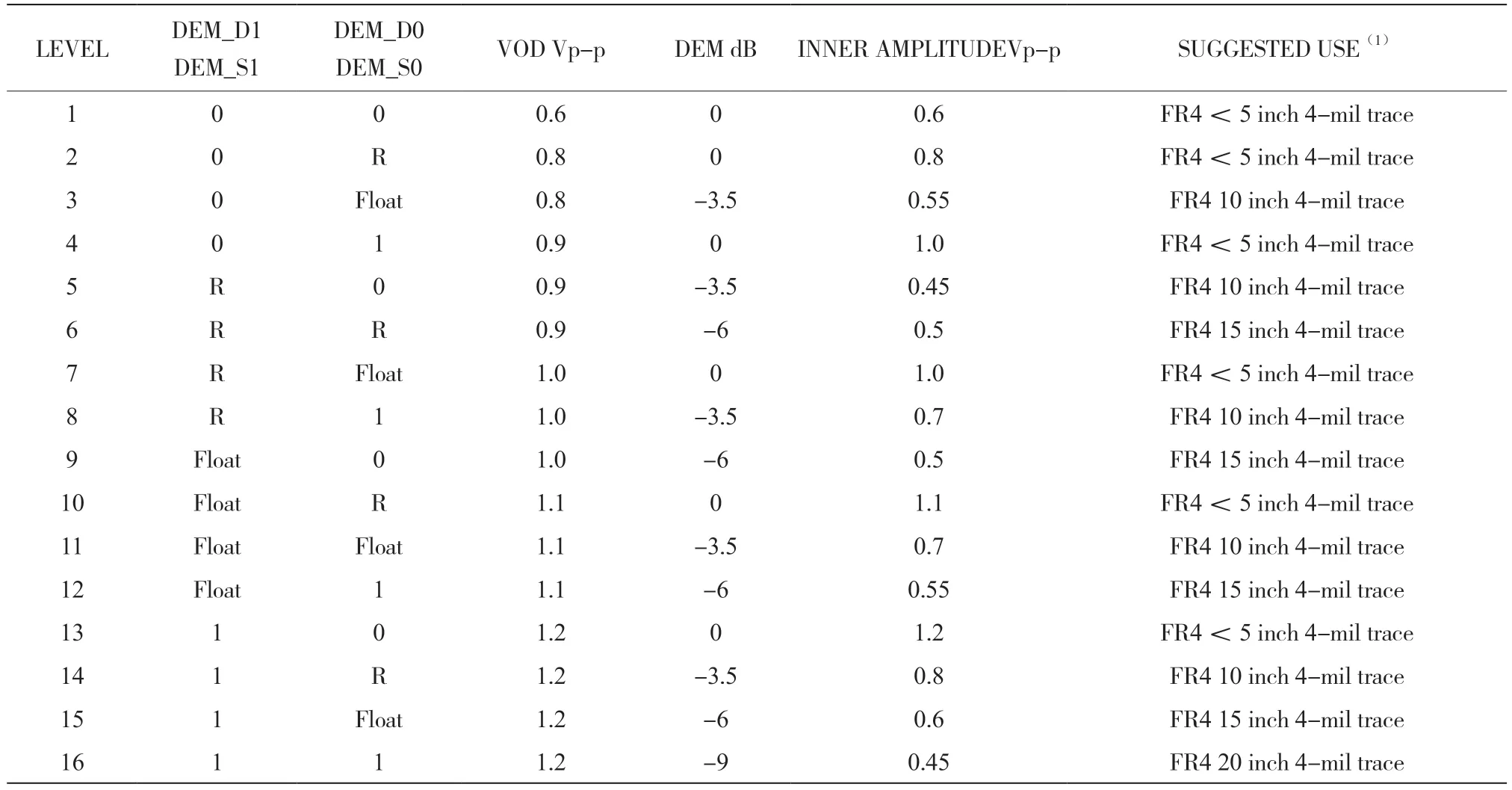

表1列出了DEM_D0/1和DEM_S0/1设置不同值时,对应的去加重参数和输出的差分信号的幅值。最左侧一列是对应参数试用的走线线宽和长度,本文中板卡是FR4板材,5 mil走线宽度,线长约10 inch,因此选用第8行所对应的参数。

表2列出了EQ_D0/1和EQ_S0/1设置不同值时对应的均衡器参数,最左侧一列同样是建议使用场景,本文选用第4行所设参数。

表1 去加重参数设置表

表2 均衡器参数设置表

高速信号在波形无失真的理想情况下,各个码元将重叠在一起。由于示波器余晖效果,最终在示波器上看到的是迹线又细又清晰的“眼睛”,“眼”张开得最大。当有码间串扰时,波形失真,码元不完全重合,眼图的迹线会不清晰,引起“眼”部分闭合。“眼”张开的大小反映了失真的程度和码间串扰的强弱。由此可知,眼图能直观表明码间串扰和噪声影响,可评价一个基带传输系统性能的优劣。

图3是信号速率为8 Gb/s、传输走线为10 inch、线宽5 mil、EQ[1:0]=0、DEM[1:0]=0.1时的实测信号眼图。可以看出,眼图边缘清晰,睁开较大,可见通过DS100MB203芯片改善后的信号质量非常高。

图3 DS100MB203改善后的信号眼图

2 结 论

针对高速信号通道选择切换的问题,提出了一种基于DS100MB203芯片的高速信号开关电路设计,不仅可以实现两路Serdes信号的开关切换,而且具备通过设置去加重和均衡参数改善信号传输质量的功能。该电路设计简单,功耗较低,可以广泛应用于高速信号传输设计。