基于软件定义的多协议控制器架构设计

2020-10-21夏云飞张丽杨堃李沛杰许立明

夏云飞,张丽,杨堃,李沛杰,许立明

(1.天津市滨海新区信息技术创新中心,天津 300457;2.国家数字交换系统工程技术研究中心,河南 郑州 450002)

1 引言

随着新型网络技术的发展,网络应用已经从早期非实时业务,发展到目前以文本、图像、语音、视频综合内容承载为主,并呈现出终端类型多元化、接入方式多元化、设备形态多元化、业务场景多元化等趋势[1]。基于开放架构的软件定义网络(SDN,software defined network)[2-3],更加强调系统的多标准、多协议、高鲁棒、高效能等特性。面对以上需求,现有网络中的交换节点接口标准单一固定,难以满足接入方式与设备形态多元化的趋势[4]。通过调研,国内外还没有能满足多种高速串行通信协议的控制器,无论是国内领先的天河二号超算中心,还是国外领先的Intel极光数据中心,内部都是通过集成PCI-E或光纤等单一协议接口来支撑数据通信网络,因此一个支持多种接口规范的交换器件十分必要。

现有数据中心中被广泛使用的高速协议为:以太网Ethernet 10GBASE-KR(简称Ethernet)、Serial RapidIO(简称SRIO)以及Fiber Channel(简称FC)。Ethernet协议适用于数据中心间的远距传输与网络拓扑,FC协议大多作为数据中心内部的高速存储访问接口,而SRIO协议则大多作为嵌入式系统中拓展高性能DSP或GPU所使用的协议接口,3种协议的应用场景、传输方式以及兼容频点各不相同。而数据中心正以多协议接口设备作为多形态组网的解决方案,但造成系统体积与能耗骤升[5]。随着高性能计算平台对系统架构可重构需求的增加,单纯固化集成多种单一协议的方案不利于构建高性能可重构互联网络[6]。

本文对上述3种高性能串行协议功能进行了分析与归一化整合,并利用软件定义与可编程硬件技术实现了一种基于软件定义的高性能多协议控制器架构,最终利用40 nm工艺实现支持多协议SerDes电路样片配合可编程电路构建了验证系统。

2 多协议控制器架构说明

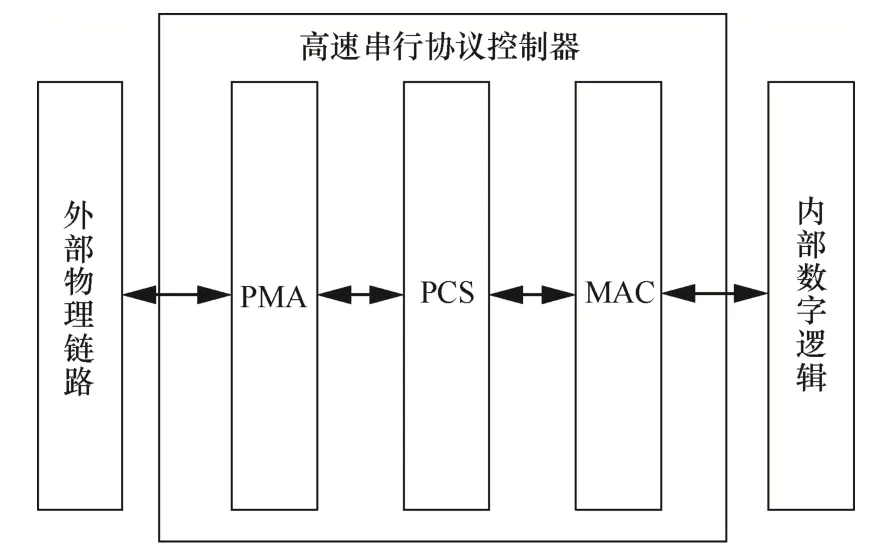

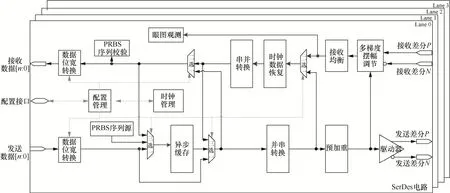

Ethernet、SRIO以及FC这3种高速串行协议控制器的基本结构,均包含3部分电路:物理传输子层(PMA,physical media access)电路、物理编码子层(PCS,physical coding sub-layer)电路以及介质访问控制器(MAC,media access control)电路,其结构如图1所示。

图1 高速串行协议控制器结构Figure 1 The architecture of high-speed serial protocol controller

PMA电路主要完成数据的串/并转换,进而实现高速物理传输[7],本文所设计的多协议控制器中的PMA电路根据3种协议的物理规范、通道绑定与频点等需求,采用软件定义互联思想设计多协议高速串行收发器电路。

PCS电路主要完成数据编解码、通道绑定、位宽转换等功能。本文提取3种协议在PCS子层功能实现中的公共算粒,并将各个协议私有算粒归一为可配置逻辑,最终实现多协议PCS子层电路。

各协议MAC电路主要负责数据包流量控制功能,不会对数据包进行帧解析。而3种协议在流量控制与校验重传处理上差异较大,私有算粒比重高,无法通过复用重构进行归一化。因此,对MAC硬件可重构电路,通过动态加载不同的电路结构,实现多协议异构。

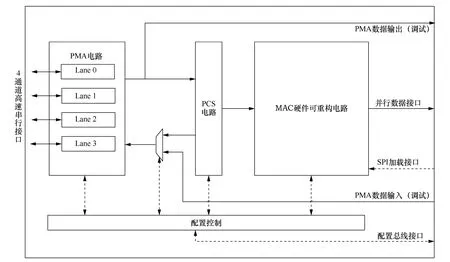

多协议控制器架构如图2所示,其基本工作流程如下。

1)控制器上电,主控根据上层应用,经配置总线接口通过SPI接口加载MAC硬件可重构电路配置,实现对应协议控制器MAC逻辑。

2)MAC电路配置加载完毕后,内部主控通过配置接口,对PMA与PCS电路进行相应模式配置,内部主控监测反馈信息以及链路状态。

3)上层应用通过配置接口轮询确认反馈信息与链路状态无误后,开始数据传输。

所有工作流程均通过内部主控完成软件定义硬件结构配置,内部主控通过内嵌的一个轻量化MCU实现,用于验证软件定义功能。整个协议控制器的工作模式,都可以通过软件定义的形式进行灵活切换,从而满足系统不同应用场景下的异构需求。

图2 多协议控制器架构Figure 2 The architecture of multi-protocol controller

3 多协议控制器架构设计

3.1 可重构多协议MAC

多协议控制器架构主要应用于数据中心软件定义互联的交换设备或芯片中,因此本文多协议控制器MAC电路并不解析数据包,而是实现数据链路层功能。而每种协议MAC电路具体功能各不相同,对于FC协议而言,MAC层处理包括协议数据链路层和交换适配层[8],而其中FC协议的交换适配层是FC的特化处理算粒(简称FC-AE-ASM控制器),无法与其他协议兼容;以太网MAC电路除必要的流控功能外,其特殊设计的数据校验与重传机制[9]都是差异化较大的处理;SRIO协议MAC层采用基于信用的流控处理,而且具备SRIO维护包管理层功能[10],处理复杂且无法与以上两种协议MAC处理兼容。

因此,多协议控制器MAC电路很难采用归一公共算粒的设计方法,并且由于存在不同通道绑定形式下的多种协议应用,单纯并行堆叠不同的MAC电路,势必带来庞大的冗余设计,而且无法适应软件定义互联的灵活多变的应用形态。综上,多协议控制器的MAC电路采用基于软件定义的硬件可重构电路进行实现。

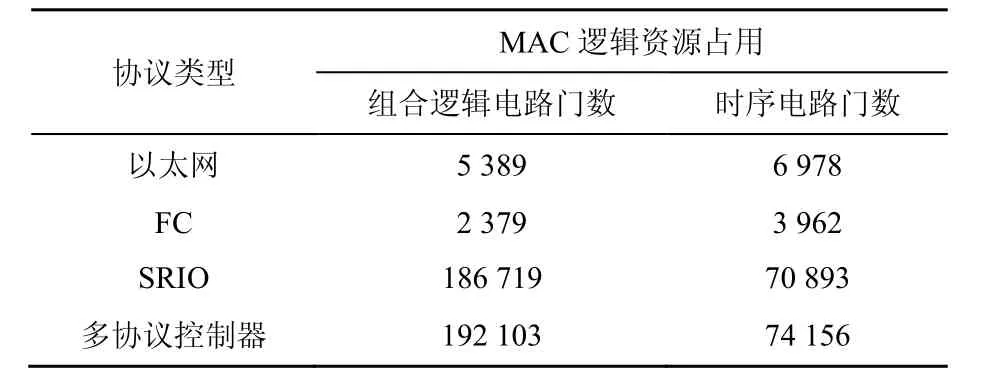

针对3种协议控制器使用电路综合工具进行实现,并根据综合结果统计3种协议MAC部分的逻辑资源,如表1所示。

表1 3种协议以及多协议MAC电路资源统计Table 1 Resource statistics of 3 protocols and multi-protocol MAC circuit

根据以上各电路的资源数据,为了最大限度地复用PCS与PMA电路,从而确定可编程电路的资源要求,可以同时放下4个以太网或FC协议的MAC电路。

然而,SRIO协议控制器MAC电路规模庞大,如果以SRIO资源为依据来确定可编程电路资源,会造成较大的资源冗余。所以,对SRIO协议MAC电路进行功能拆分,将SRIO协议中接口处理部分统一在FC与以太网可重构电路结构中实现,其他功能单独使用专用电路实现。这样既满足FC或以太网协议4个1x通道工作,又支持SRIO协议的功能需求,可以最大限度地完全利用PMA电路的4个Lane通道资源。

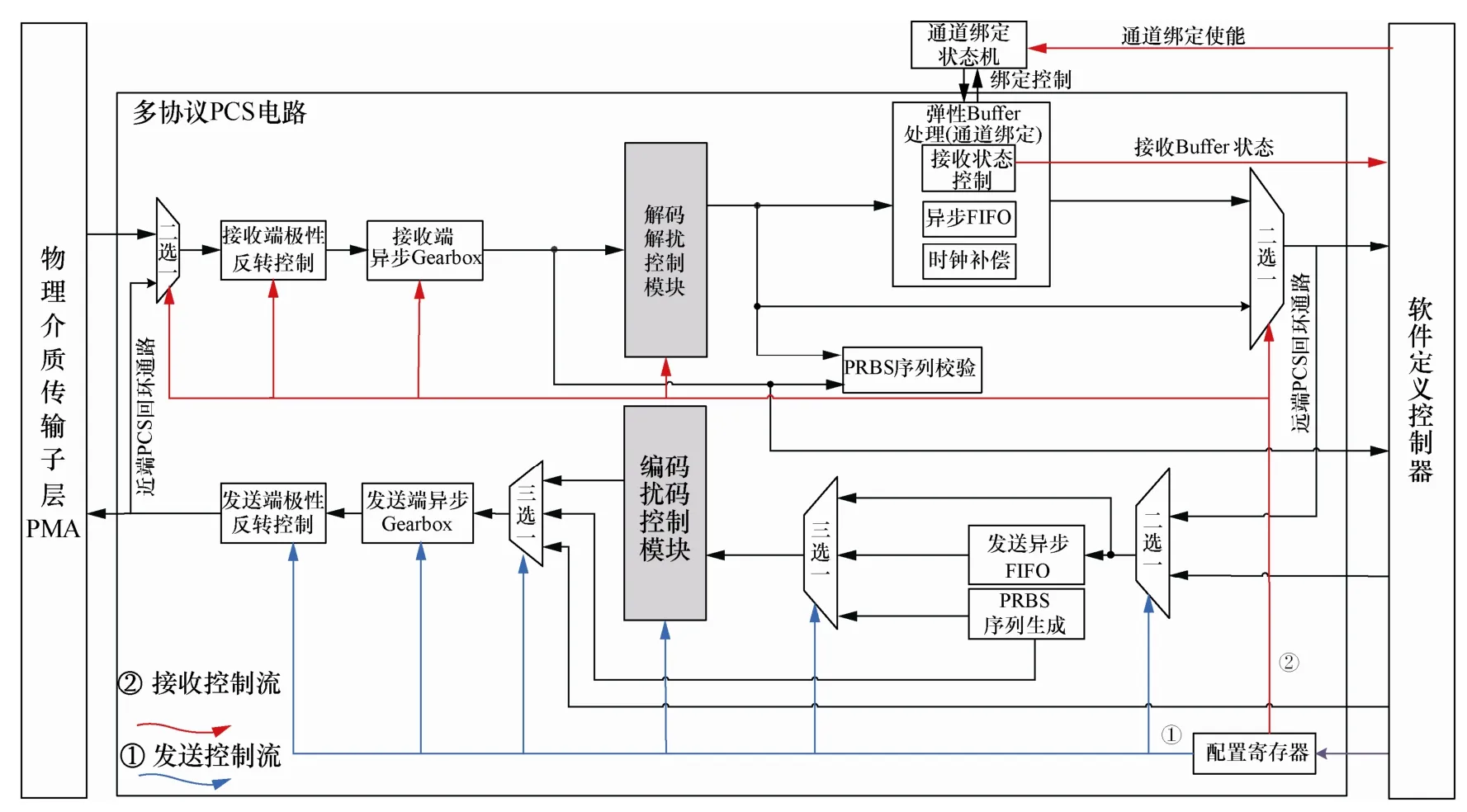

3.2 软件定义多协议PCS电路

本文中的协议控制器支持3种不同协议,如果根据协议种类设计多个完全独立PCS电路,虽解决了多协议的PCS电路需求,但由于电路设计复用度低,导致电路本身面积与功耗开销增加,从而直接影响系统的体积、重量、功耗等指标。

通过对比SRIO协议、FC协议以及Ethernet协议对PCS子层的定义,提取4种协议对PCS子层的功能需求。多协议PCS要求支持包括编解码功能、加扰功能、变速箱功能、极性控制、位序控制、PRBS生成、Comma检测、Headers检测、时钟补偿、通道绑定、PRBS检测等。

提取3种协议在PCS子层中的公共算粒作为通用逻辑,并把差异化私有算粒做成可配置逻辑,从而实现多协议通用的PCS电路设计。PCS电路通过软件配置模式的不同,可以动态支持SRIO协议、FC协议以及Ethernet协议规范数据的正确传输。同时支持与SRIO Controller动态捆绑模式的特殊需求,软件定义多协议PCS电路如图3所示。

编码扰码、解码解扰逻辑以及弹性Buffer逻辑都能随配置模式的改变而进行动态切换;弹性Buffer通过与通道绑定状态机配合能够完成SRIO协议需要的通道动态绑定功能。同时,通过配置模式选择是否使用弹性Buffer。上层软件定义可以通过配置寄存器实现多协议PCS子层工作模式动态切换。

图3 软件定义多协议PCS电路Figure 3 The circuits of software defines multi-protocol PCS

3.3 多协议PMA电路

多协议PMA电路是软件定义互联芯片的关键,是多协议互联的物理层基础,通过分析3种协议的特性可知,其各自物理层的功能结构差异不大。可以通过较为简单的归一化设计,实现同时满足3种协议的PMA电路,表2为不同协议需实现的功能列表。

由表2分析可知,3种协议在PMA层的设计功能基本一致,其主要功能是将数据由并行转化为高速串行信号并发送至信道上(包括其逆过程),同时可以将高速的串行数据从信道上接收并转化为并行信号供上层使用,其电路系统如图4所示。

图4 多协议SerDes设计架构Figure 4 Multi-protocol SerDes design architecture

PMA电路按照功能子模块的方式进行设计,功能模块之间的数据与控制关系如图4所示。由于3种协议对PMA电路的功能要求基本一致,因此将功能相似的部分设计为通用逻辑,电路按照4个Lane一组进行设计,主要由3部分组成:收发主通道、时钟处理模块、配置管理及复位模块。

接收器:包括阻抗校正电路、均衡器(连续时间线性均衡CTLE和判决反馈均衡DFE)、时钟数据恢复电路和逻辑(CDR)、相位差值器、并行数据位宽可配置的串并转换电路、PRBS检测、内建接收通路环回等。主要根据输入数据来调整时钟,保证对数据的正确采样,同时将串行数据转化为并行数据。

发送器:包括并串转换电路、输出驱动器、预加重控制电路、边沿控制电路、阻抗校正电路、PRBS校验生成、内建发送通路环回以及数据位宽可配置的并串转换电路等,完成由并行到串行数据的转化和驱动。

时钟管理:差分驱动模块,主要包括4个Lane共用的锁相环电路QPLL以及各Lane使用的锁相环电路CPLL、时钟选择、分频电路等。该模块可以根据软件配置,为PMA中的SerDes提供3种协议各自频点需求的时钟。

配置管理:主要包括配置总线管理模块、寄存器管理模块,负责对数据路径选择、时钟频率、数据位宽以及子模块工作模式实现软件配置控制。

整个PMA电路通过软件定义可配置电路,可以实现针对不同协议、不同频点的结构切换,从而达到软件定义的协议异构功能。

4 原型实现与测试分析

4.1 系统搭建

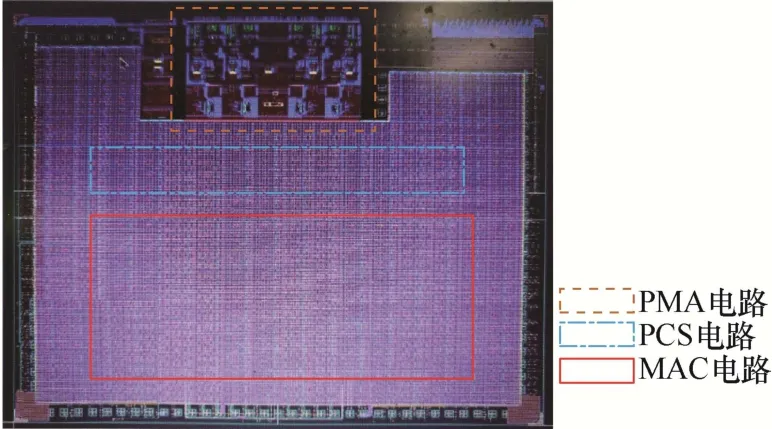

基于本文架构设计的控制器电路,在40 nm工艺节点下进行MPW流片。测试芯片中包括可编程电路与ASIC电路,PMA电路中的4通道SerDes电路,设计可以不经过PCS电路的测试接口,直接进行单独数据测试。图5为多协议控制器测试芯片布局。

图5 多协议控制器测试芯片布局Figure 5 The floorplan of the multi-protocol controller

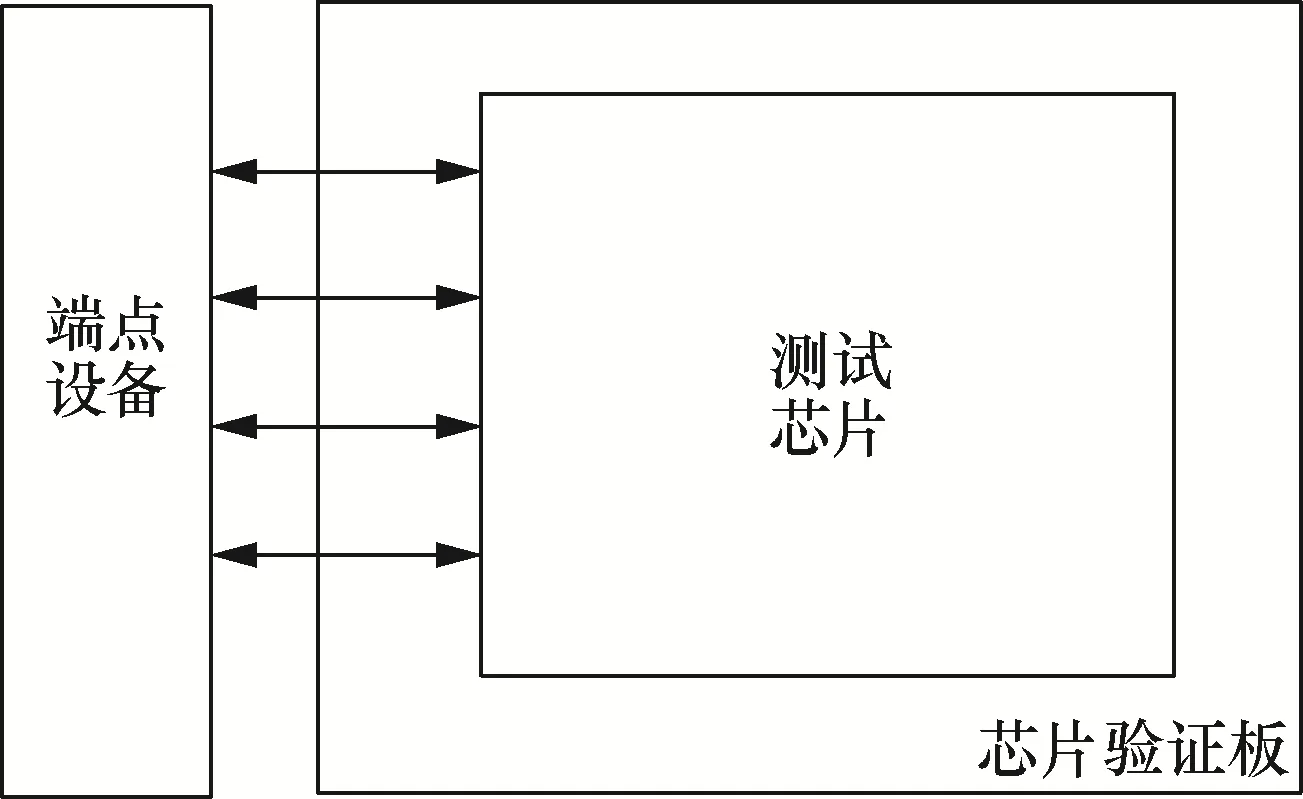

围绕测试芯片,本文构造了一个多协议原型验证平台。验证平台主要由测试芯片验证板与端点设备(第三方标准测试仪或FPGA端点设备),原型验证平台架构如图6所示。

4.2 电气特性测试

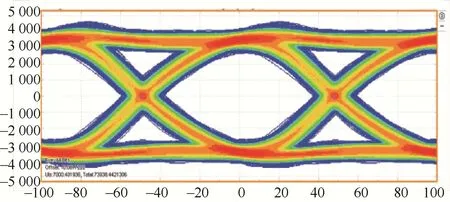

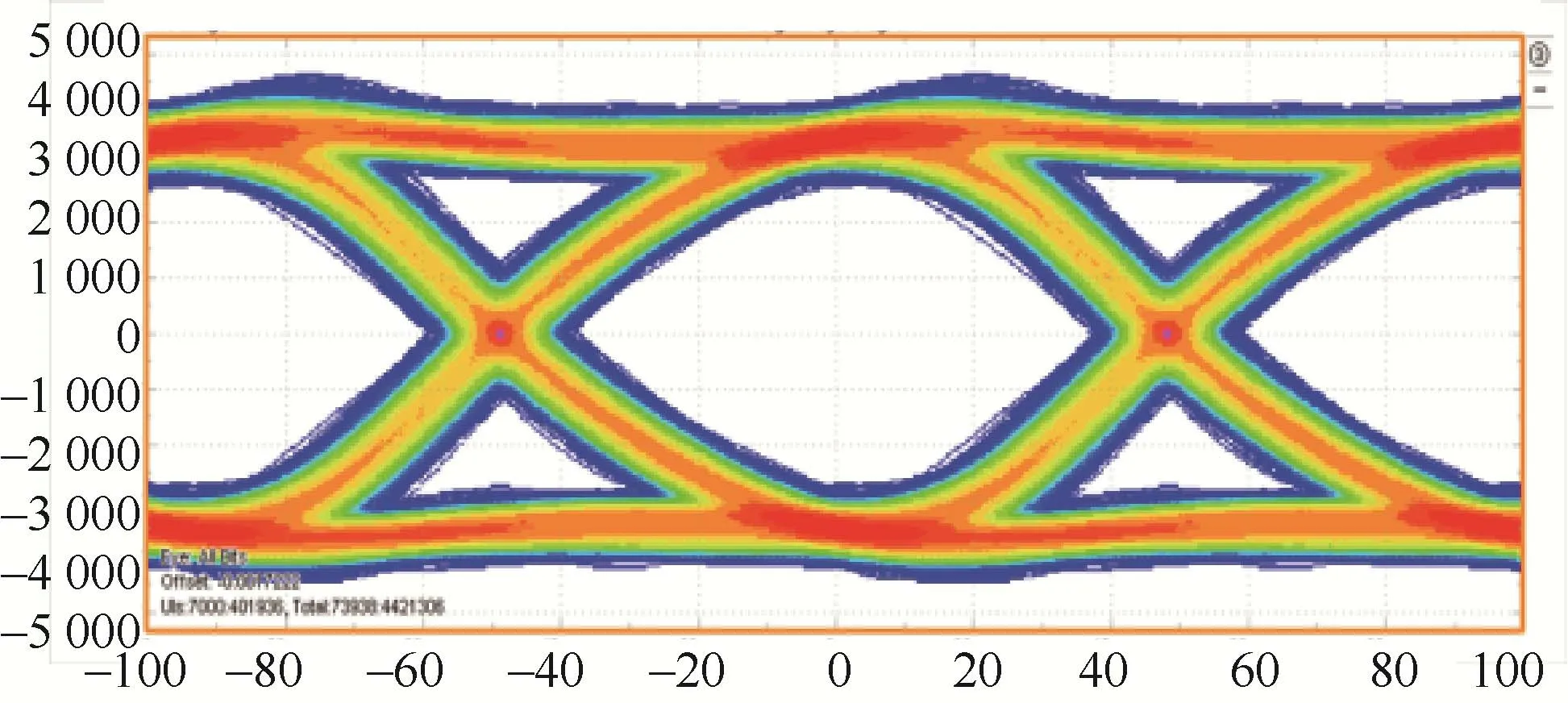

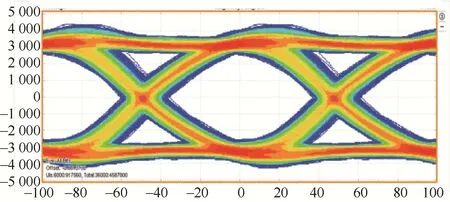

高速协议在进行具体的协议端点设备测试前,需要先确认PMA电路模拟SerDes电路的功能与性能。因此,首先使用高速示波器对SerDes进行测试,确认模拟电路无误后,再展开协议功能测试。图7~图9为针对FC、SRIO以及以太网等协议需要的最高频点下的眼图测试结果,其中横坐标代表测试时间周期,纵坐标代表输出信号电压幅值。

图6 原型验证平台架构Figure 6 The diagram of prototype verification platform

图7 1x通道8.5G频点TX眼图Figure 7 The eye diagram of 1x 8.5Gbit/s TX Channel

图8 4x通道10.3125G频点TX眼图Figure 8 The eye diagram of 4x 10.3125 Gbit/s TX Channel

图9 1x通道10.3125G频点TX眼图Figure 9 The eye diagram of 1x 10.3125 Gbit/s TX Channel

由测试结果可知,输出发送信号均符合相关协议要求,信号随机输出抖动RJRMS参数在1.81~1.95皮秒。同时在以上测试中,不同协议频点使用软件配置,实现动态切换测试。

SerDes功能性能确认后,分别对3种协议进行端点设备通信测试。以太网与FC协议均采用同第三方标准协议分析仪进行数据流量测试,并通过测试仪的上位机调试软件确认链路状态与数据包校验结果。SRIO协议测试使用Xilinx FPGA开发板作为测试端点设备,端点设备实现对应频点速率的标准SRIO协议IP控制器,最终通过读取端点设备数据校验结果确认数据通路完整性。

4.3 协议一致性测试

4.3.1 以太网协议测试结果

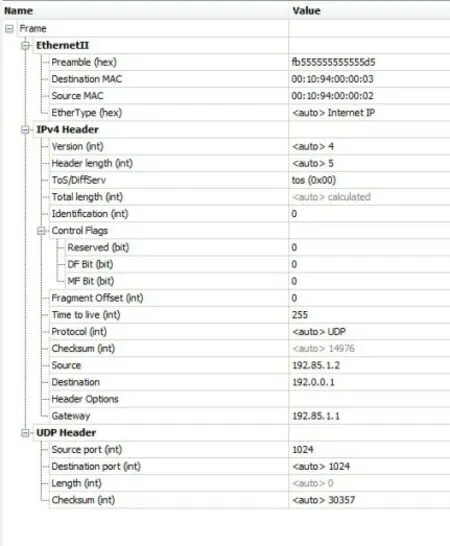

软件配置控制器为以太网协议工作模式(包含MAC可编程电路的加载配置)。完成协议控制初始化后,对以太网协议分析仪配置数据接收/发送为标准Ethernet格式,数据率为10.312 5 Gbit/s,数据包格式配置如图10所示。

图10 Ethernet协议分析仪数据包格式配置Figure 10 The package format configuration of ETH protocol analyzer

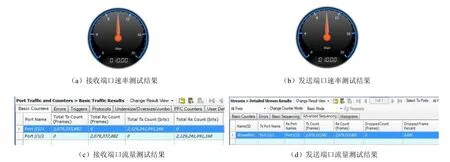

完成配置后启动协议分析仪发送数据包,确认发送与接收端流量与速率,测试结果如图11所示。

图11 Ethernet协议分析仪流量测试结果Figure 11 Test result of Ethernet protocol analyzer traffic

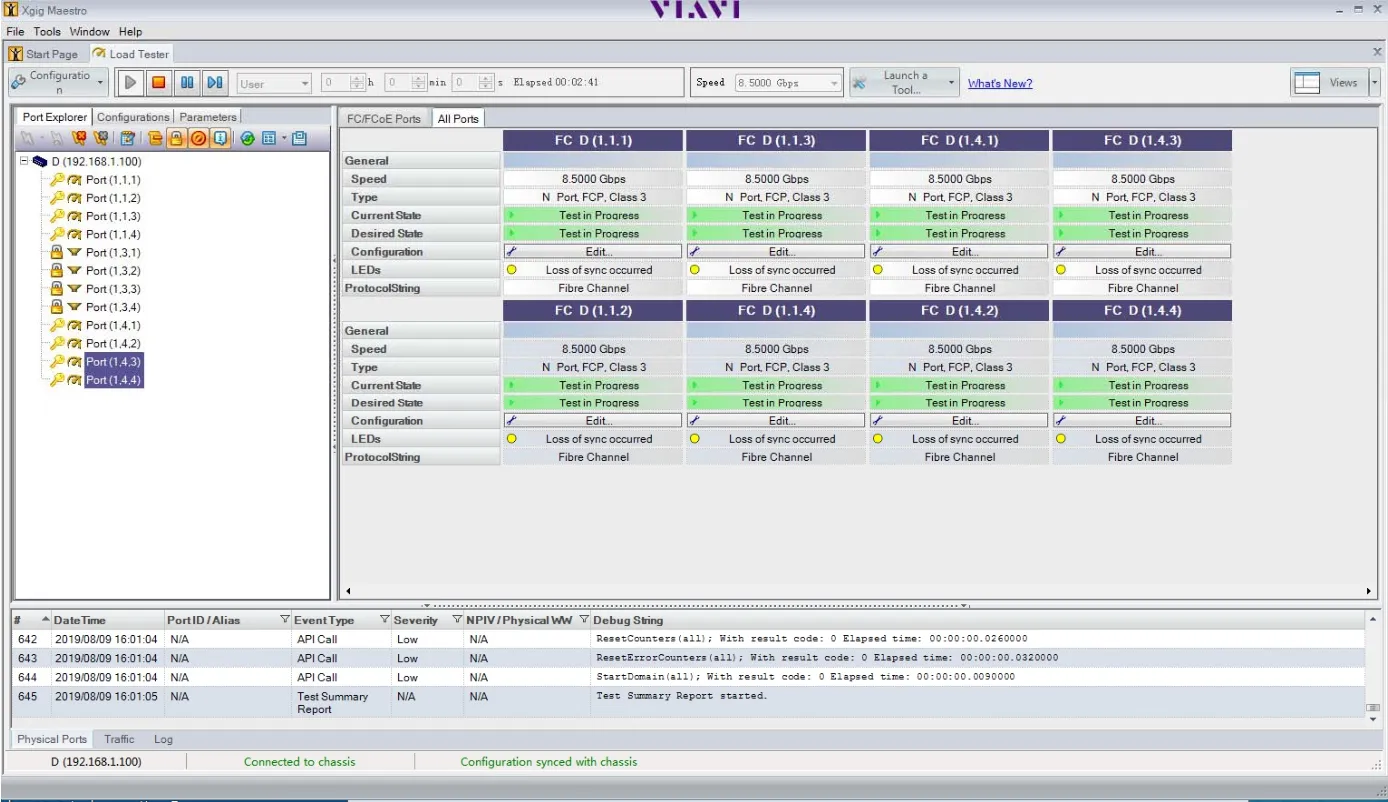

4.3.2 FC协议测试结果

与以太网测试类似,首先软件配置控制器切换为FC协议工作模式,再对FC协议分析仪进行配置,设置数据率为8.5 Gbit/s,测试模式为端点设备与测试设备互发通信,链路与数据测试结果如图12所示。

测试同时4个FC通道在8.5 Gbit/s数据率下,发送与接收端数据传输情况。由结果可知链路建立稳定,无失锁与误码现象,满足FC协议通信要求。

4.3.3 SRIO协议测试结果

SRIO协议测试中的端点使用另一块FPGA平台,利用FPGA端点设备中的Chip scope配合FPGA EDA工具实时抓取数据,以确认测试数据结果。

测试方法是端点设备发送给多协议控制器后,多协议控制器将接收到的数据发回给端点设备确认结果。测试中配置端口设备与测试端频点速率均为10.312 5 Gbit/s,在确认链路锁定成功后,启动端点设备数据通信并实时抓取数据。

经测试,确认SRIO协议在10.312 5 Gbit/s速率下,在1 h连续通信测试中误码率为10−14,满足RapidIO协议误码率低于10−12的要求。测试结果如图13所示。

在以上的所有协议通信测试中,均是通过软件配置实现工作模式、通道数量以及速率频点切换的,确认本文所设计的基于软件定义多协议控制器的功能与性能满足预期。

图12 FC协议分析仪测试结果Figure12 Test result of FC protocol analyzer

图13 SRIO协议数据通信端点设备抓取测试结果Figure 13 Test result of SRIO protocol data communication endpoint device chip-cope

4.4 协议形态测试

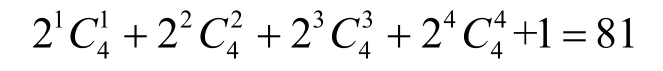

3种协议MAC电路应用形态总结为如下5种场景。

1)实现单一协议控制器,即实现4/3/2/1个以太网控制器MAC逻辑,或者实现4/3/2/1个FC控制器的MAC逻辑。

2)实现4个混合协议控制器,即实现m个以太网控制器MAC逻辑,并且实现4-m个FC控制器的MAC逻辑。

3)实现3个混合协议控制器,即实现m个以太网控制器MAC逻辑,并且实现3-m个FC控制器的MAC逻辑。

4)实现2个混合协议控制器,即实现1个以太网控制器MAC逻辑和实现1个FC控制器的MAC逻辑。

5)实现单一协议SRIO控制器。

多协议控制器对外设计有专门SPI加载总线,用于不同形态电路配置加载。可重构电路的应用形态决定了可支持应用场景的多样性。如上所述,考虑上述5种应用场景,可支持的电路数据计算如下。

对应的MAC电路可实现81种不同的软件定义可重构控制器形态。经过使用原型环境分别加载以上81种软件定义控制器,各种应用形式均通过4.2节与4.3节的电气特性与协议一致性测试,符合支持多协议控制器多形态应用设计预期。

5 结束语

本文设计的基于软件定义的多协议控制器,支持FC、以太网以及SRIO这3种高速串行协议标准,并具备通过软件定义切换不同协议工作模式的功能。为今后拟态计算平台高异构性需求系统的数据互联,提供适合的解决方案。同时,构建的原型验证的测试结果表明,本文提出的基于软件定义的多协议控制器可以满足Fiber Channel、Ethernet以及SRIO协议的要求,满足设计预期。