数字电路时间同步实验设计

2020-10-09穆华俊

杨 静,周 军,穆华俊

(武汉大学 电子信息学院,湖北 武汉 430072)

数字系统的时间同步具有非常广泛的应用,电信系统[1]、电力系统[2]、天文观测[3]、金融[4]、军事[5]等对时间同步精度都有相应的要求[6]。以电力系统的行波测距为例,当时间同步误差为1 ms 时,所测得的故障点与维修人员的距离误差为150 km,这样的结果几乎没有使用价值;但当时间同步误差减小到1 μs 时,距离误差仅为150 m;而巡航导弹的时间同步误差只有在50 ns 以内时,才有精确命中目标的可能性。微小的时间同步误差可以造成很大的测距误差,可谓是“失之毫厘,谬以千里”。一般而言,电力传输、卫星导航、军事等领域对时间同步精度要求较高,通常要达到 μs 乃至 ns 级。

传统的数字电路课程鲜有涉及时间同步的内容,且时间同步的实现还具有以下不同于一般数字电路实验的特征:①数字电路实验的结果一般是确定的,输入输出均为明确的“0”“1”信号,而时间同步的结果具有不确定性,所关注的是同步误差的大小及其影响因素;②数字电路实验多局限于单个独立的数字系统,而时间同步则涉及两个或两个以上的数字系统,必须考虑多系统协同工作问题。因此,设计时间同步实验对于数字电路课程的学习具有很好的补充与深化作用。

将科研融入教学是高校教学改革的发展方向[7],源于科研的实验项目通常具有更好的系统性、完整性以及更明确的工程背景,更有利于培养学生的创新实践能力[8]。我校在高频地波雷达的系统研制和应用方面已有三十多年的历史,积累了丰富的科研成果。其中,多部同频高频地波雷达的组网探测要求雷达之间满足高精度时间同步[9],为此我们研制了雷达同步装置[10-11]。基于此,我们对雷达同步装置进行了简化设计,将其引入实验教学,设计了数字系统的时间同步实验。该实验利用FPGA 芯片、信号发生器、GPS 接收天线、GPS 可驯钟等器件,模拟数字系统的直接同步和间接同步两种方案,并对时间同步误差进行测量分析。在此基础上,还探索了若干工程实际问题的解决方法。本实验有助于学生掌握数字系统时间同步的基本方法,培养在工程背景下进行数据统计分析的能力,锻炼多系统协同工作的意识和思维。

1 实验设计思路

雷达网络中各站点之间的同步方法一般分为直接同步、间接同步和独立式同步三种类型[12]。直接同步是指通过数据传输通道将触发脉冲、频率基准信号和射频编码信号等从一个站点传送至另一个站点。数据传输通道的种类包括微波中继、卫星通信、短波通信和有线传输等。间接同步法是指每个站点设置一个高稳定时钟,用来提供时间、频率以及相位相参的基准信号。这些时钟需定期用同一个更高精度的时间基准来校准。独立式同步主要适用于非合作的机会照射源的情况,接收机利用发射极的直达波信号或者地物散射波来提取同步信息,精度一般不高,只用作粗测和告警。

由于本实验关注的是高精度时间同步问题,因此在设计实验时,仅以雷达站的直接同步和间接同步两种方式为原型,所设计的电路结构框图如图1 所示。

图1 实验电路结构框图

上述电路中,FPGA1 和FPGA2 是两片相同型号的FPGA 芯片,用以代表两个数字系统。两片FPGA的时间同步情况通过其产生的矩形脉冲波来反映。FPGA 以同步控制信号的上升沿为参考时间,延迟一定时间产生矩形脉冲波。两路矩形脉冲波的上升沿时刻、周期均设置为相同的数值。将两路矩形脉冲波接入示波器的两个通道,观察其上升沿时间差,即为两片FPGA 的时间同步误差。

直接同步方案里,两片FPGA 的时钟源由两台信号发生器提供,同步控制信号由 FPGA1 产生并通过一根导线传送给FPGA2。由于同步控制信号由一个数字系统直接传送给另一个数字系统,因而称为直接同步法。

间接同步方案里,时钟源和同步控制信号由两块GPS 可驯钟提供。除了这两路信号外,可驯钟还串行输出时间信息包数据给 FPGA。由于这里的同步是通过可驯钟周期性地使用 GPS 授时信号驯服本地低相噪恒温晶振来实现的,因而称为间接同步法。

GPS 可驯钟主要由GPS 接收机和恒温晶振组成。由于 GPS 地面控制系统是将各个卫星上的原子频标同步于美国海军天文台的原子时从而建立 GPS 系统的,因此GPS 接收机输出的秒脉冲信号的长期稳定性非常好。然而,卫星信号在传输过程中的累计误差使得秒脉冲的上升沿存在随机抖动,在卫星失锁或卫星时钟发生实验跳变的情况下,秒脉冲的误差可能达到数百毫秒[13-15],因此,GPS 接收机输出的秒脉冲信号的短期稳定性较差。与之相比,恒温晶振的短期稳定性非常好,而长期稳定性却由于老化等原因较差。所以,用卫星授时信号对恒温晶振进行驯服,可以得到短期和长期稳定性俱佳的信号,这就是GPS 可驯钟的原理。可驯钟的成本相对于同样精度的原子钟大幅降低,因而得到广泛应用。本实验所采用的可驯钟是Trimble 公司的ThunderBolt GPS 驯服时钟模块,输出信号包括:① 10 MHz 标准正弦波频率信号,此信号作为FPGA 的时钟源;②秒脉冲,作为FPGA 的同步控制信号;③一个RS232 接口输出一周时间内的时、分、秒、年、月、日以及位置/状态等信息,此端口的信号也输入到FPGA。

实验中,要求学生按照图1 所示的结构框图搭建电路,编写FPGA 程序实现输出矩形脉冲波,测量并分析时钟源频率、时钟源频率同步误差、同步控制信号时间同步误差等对数字系统时间同步误差的影响,并提出改进措施。在此基础上,考虑同步控制信号短时间丢失的应对办法,实现两个数字系统在预设时间到来后自动同步的功能,锻炼学生解决实际工程问题的意识和思维。

2 实验内容的设置

2.1 实验电路设计

本实验的主要设计工作是在FPGA 中完成的,实验的具体实施方案如图2 和图3 所示。

图2 直接同步方案FPGA 内部电路原理图

图3 间接同步方案FPGA 内部电路原理图

在直接同步方案里,FPGA 内部包括矩形脉冲波产生模块、双口随机存储器(DRAM)模块。FPGA1比 FPGA2 多了一个同步控制信号产生模块。其中,DRAM 模块存储微处理器写入的参数,包括矩形脉冲波相对于同步控制信号的延迟时间、周期等;同步控制信号产生模块产生同步控制信号;矩形脉冲波产生模块根据DRAM 中的参数,以同步控制信号的上升沿时刻为参考,产生矩形脉冲波。

在间接同步方案里,FPGA 内部包括串口通信模块、时间信息提取模块、矩形脉冲波产生模块和DRAM 模块。其中,串口通信模块读取可驯钟RS232接口输出的数据;时间信息提取模块提取其中的年月日时分秒等当前时间信息;矩形脉冲波产生模块根据当前时间、DRAM 中的参数,以可驯钟输出的秒脉冲为参考,产生矩形脉冲波。

2.2 测量与分析时间同步误差

利用示波器可以测量两片FPGA 所代表的数字系统的时间同步误差,即两个矩形脉冲波的上升沿时刻之差,如图 4(a)所示。根据矩形脉冲波的产生方法,可以简单分析其时间同步误差来源。图4(b)是矩形脉冲波产生方法的示意图。其中tin1表示FPGA1 使用的同步控制信号的上升沿时刻,tout1表示FPGA1 产生的矩形脉冲波的上升沿时刻,T1为 FPGA1 使用的时钟源周期,矩形脉冲波相对于同步控制信号延迟nT1时间产生(n为整数),即:

同理,FPGA2 产生的矩形脉冲波的上升沿时刻可以表示为:

将式(2)减去式(1),得到两个矩形脉冲波上升沿时刻之差Δtout的表达式:

其中,Δtin是两个同步控制信号的上升沿时刻之差,ΔT是两个时钟源周期之差,f1和f2分别是两个时钟源的频率。

图4 时间同步误差的测量与分析

从式(3)可以看出,矩形脉冲波的时间同步误差与两个同步控制信号的时间同步误差、两个时钟源的频率同步误差以及时钟源频率值有关,对实验数据的统计分析应能得到近似相同的结果。实际上,影响时间同步误差的因素还包括时钟源的相位同步误差、同步控制信号的检测时间差等因素,虽然这些因素难以量化,但分析实验数据时应当考虑进去,这样才能对实验现象进行正确的解释。

2.3 同步控制信号短时间丢失的应对办法

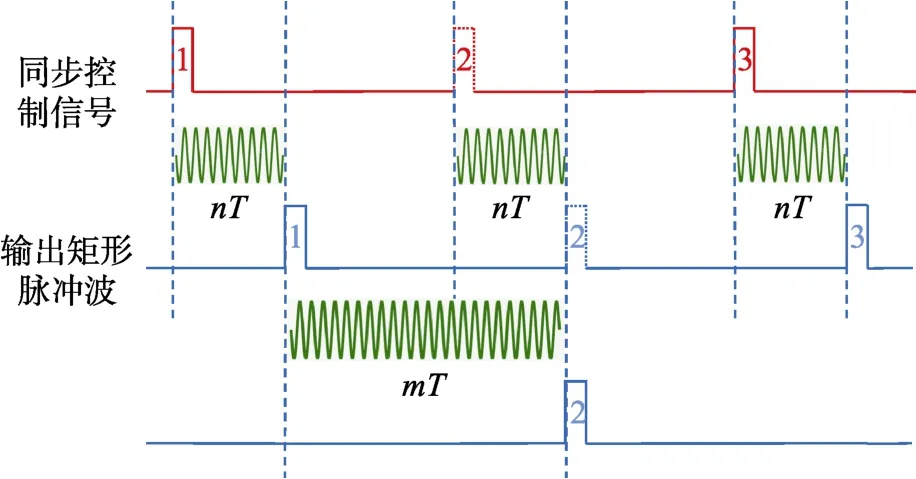

实际工程中,可能会出现同步控制信号丢失的情况,例如在直接同步方案里,数据传输通道的干扰可能会导致同步控制信号丢失。如果不采取应对措施,以同步控制信号为基准的矩形脉冲波也将丢失。在图5 中,输出矩形脉冲波的1 至3 号脉冲分别以同步控制信号的1 至3 号脉冲为时间基准,延迟nT时间产生,如果同步控制信号的2 号脉冲丢失,则矩形脉冲波的2 号脉冲也将丢失。

图5 同步控制信号丢失的处理方法示意图

一般来说,同步控制信号短时间丢失时,时钟源的频率不会发生很大偏移。如果继续按照矩形脉冲波的设定参数产生脉冲,仍然能够保持时间同步。在图5 中,以矩形脉冲波的1 号脉冲为时间基准,延迟mT产生新的脉冲,则可以补上矩形脉冲波的 2 号脉冲。本实验要求学生通过设计FPGA 程序来实现此功能。设计的核心思想是在同步控制信号丢失和未丢失时给减法计数器设置不一样的计数初值,当减法计数器计数到0 时产生下一个脉冲。该实验内容有助于加深学生对计数器设计的认识。

2.4 自动化同步

此项实验内容仅针对间接同步方案。自动化同步的含义是多个数字系统在约定时间到来以后自动实现时间同步,如果某个数字系统因故障等原因没有同步,待工作正常后可以自动恢复同步。在图 6 中,两片FPGA 约定在同步控制信号的 1 号脉冲到来后延迟t0开始产生周期为T0的矩形脉冲波,但是当1 号脉冲到来时,FPGA2 未能检测到此脉冲,只是FPGA1 按时产生了矩形脉冲波。同步控制信号2 号脉冲到来时,FPGA2 恢复正常工作,它产生的矩形脉冲波的第一个脉冲是3 号脉冲,此脉冲相对于离它最近的前一个同步控制信号脉冲(2 号脉冲)的延迟时间为(同步控制信号的周期是1 秒):

从式(4)和式(5)可以看出,在不同的时间产生矩形脉冲波,其相对于离它最近的前一个同步控制信号脉冲的延迟时间一般是不同的。要实现自动化同步功能,必须知道最新收到的同步控制信号脉冲所对应的时间,计算出它与约定起始同步时间的间隔时间,然后再计算出矩形脉冲波相对于此脉冲应当延迟的时间。

图6 自动化同步原理示意图

在间接同步方案里,可驯钟通过串口输出每个秒脉冲对应的时间信息。本项实验内容要求学生通过设计FPGA 程序读取串口数据并提取其中的时间信息,即实现图3 中的串口通信模块和时间信息提取模块,再在此基础上实现自动化同步功能。本项实验内容较为复杂,有助于锻炼学生基于硬件描述语言进行电路设计的能力。

3 实验效果分析

从实验效果来看,该实验达到了预期目的。首先,实验内容涵盖了基于硬件描述语言的时序逻辑电路设计、基于示波器的信号测试、串口通信等知识,加深了学生对于已经学习过的电路课程的认识。第二,通过该实验,学生掌握了数字电路时间同步的基本方法,包括直接同步法和间接同步法,是对传统的数字电路学习内容的补充。第三,实验内容对于培养学生在工程背景下进行数据统计分析的能力、锻炼学生多系统协同工作的意识和思维具有积极作用。此外,实验结束后还提供若干开放性问题供学生思考,例如当两个系统相距较远时如何测试时间同步误差、已知时间同步误差值后如何消除其影响等。这些问题激发了学生进一步学习的兴趣,提高了通过查阅资料解决问题的能力,有助于学生早日参与到大学生科研活动中去。

4 结语

时间同步在数字系统中具有广泛的应用,但在传统数字电路课程中没有相关内容。本实验通过对高频地波雷达同步装置进行简化设计,将科研成果引入实验教学,帮助学生掌握数字系统时间同步的基本方法,加深对已经学习的时序逻辑电路的硬件描述语言设计、串口通信等知识的掌握,培养在工程背景下进行数据统计分析和电路设计的意识和能力。实验效果表明,该实验达到了预期目的。