激光测距仪时序发生器设计

2020-10-09赵昊晨肖鹏程张荣福

赵昊晨,熊 淳,肖鹏程,张荣福

(1.上海理工大学 光电信息与计算机工程学院,上海 200093;2.复旦大学 微电子学院,上海 201203)

引 言

现代自动化技术中少不了距离测量仪器,激光测距仪利用激光对目标位置进行测量从而实现精准定位[1],在军事、民用和工业各领域都有重要的应用。激光测距为主动式测距,其原理是主动发射激光,测量从激光发射到接收反射激光之间的时间间隔,从而将距离的测量转换为时间的测量[2],显然,测时的精度会直接影响最终的结果。时序发生器应用于激光测距仪,可对输入的参考时钟信号进行可编程延时,根据控制信号产生相应的时序信号,提供激光测距仪所需的高频率与高分辨率,从而提高测量精度。

时序发生器主要使用专用集成电路(ASIC)设计方法,也有少部分基于进阶精简指令集机器(ARM)微处理器的设计方法[3],随着现场可编程门阵列(FPGA)技术的发展,出现了基于FPGA的设计方法,虽然性能远比不上ASIC 设计,但具有开发周期短、可重复编程、制造成本低、可实时在线检测等优点,适用于集成电路(IC)开发与验证阶段的测试。

早前有人使用Xilinx 的Virtex-4 芯片作为时序发生器核心控制器[4],采用多路复用并由外部时钟芯片提供2.5 GHz 的时钟,实现了400 皮秒(ps)的分辨率,但具有高速时钟抖动较大、速率不能改变的缺点。相比之下,较为成熟的ASIC设计方法很容易实现100 ps[5]甚至几皮秒的分辨率[6-7]。文献[8]基于Altera 的Cyclone系列FPGA,实现了100 Mbit/s 的数据速率与20 ps 的分辨率,文献[9]则实现了最小13 ps 的分辨率。

近几年,FPGA 性能逐渐提升,使用Xilinx Spartan-6 芯片实现了3.2 Gbit/s 的数据速率,分辨率达到了35 ps[10],文献[11]同样使用该芯片实现了200 ps 的时序分辨率。最近我国学者提出了一种称为“时间折叠”的新方法,使用高性能的Xilinx Virtex-7 芯片实现了5 ps 的分辨率[12],经过进一步研究后又将分辨率提升至3 ps[13]。

本文基于FPGA 开发激光测距仪的时序发生器模块,并进行了性能测试与分析。

1 设计方案

已有的一些基于FPGA 开发的时序发生器主要对FPGA 内部资源进行编程,作为时标电路的延迟线,已经能实现几百皮秒甚至几十皮秒的分辨率,但容易受温度和干扰等影响,精度无法进一步提高。可见,想要利用FPGA 的资源实现更高的分辨率是有一定界限的,虽然有提升时钟频率的方法,但FPGA 在时钟频率方面同样会有限制。本文设计的时序发生器关键在于使用外部延迟链芯片作为延迟线。这种延迟线位于FPGA 芯片外部的方法,能降低一部分温度、串扰等因素对延迟线精度的影响,同时这一类专用延时芯片能达到很高的分辨率。

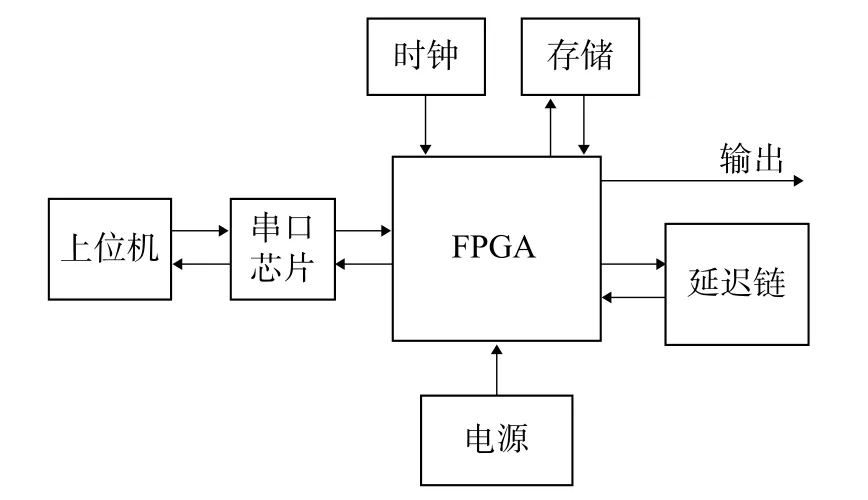

时序发生器的系统硬件架构如图1 所示。FPGA 作为核心控制器,连接各部分外围电路。以外部的高精度晶振作为参考,在FPGA内部产生初始时钟信号;外接延迟芯片提供最小延时,由FPGA 将原始信号输出至延迟芯片后再返回;通用异步收发传输器(UART)串口芯片使得FPGA 能够与上位机(PC)进行通信,通过传送延迟数据可以实时地改变信号的延时。

图1 系统硬件架构Fig.1 System hardware architecture

2 硬件实现及主要电路设计

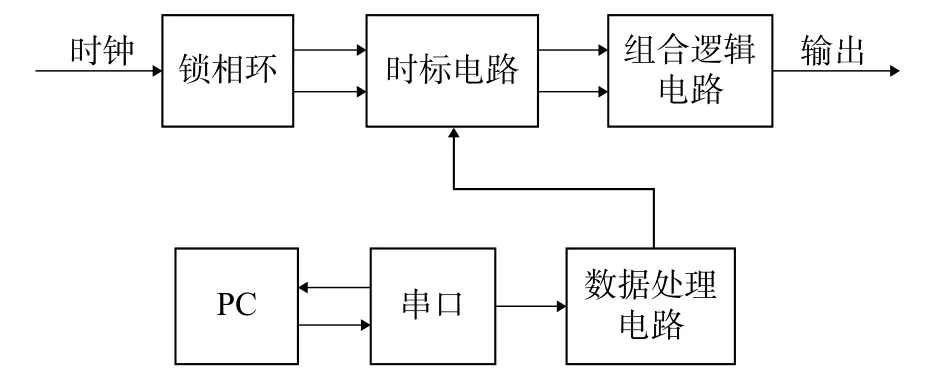

图2 所示为时序发生器电路设计简化框图,主要由锁相环、时标、数据处理电路和组合逻辑电路组成。晶振的时钟信号输入锁相环后,经过倍频输出至时标电路;数据处理电路在接收到PC 经由串口传送的延迟数据后,生成控制信号;时标电路在接收到控制信号后改变延时,最后通过组合逻辑电路输出。

图2 电路设计简化框图Fig.2 Simplified block diagram of circuit design

2.1 锁相环

锁相环电路与传统结构基本相同,主要由相位频率检测器(PFD)、电荷泵(CP)、环路滤波器(LF)和压控振荡器(VCO)构成。PFD 比较输入时钟和反馈时钟的上升沿的相位和频率,生成与两个时钟之间的相位和频率成比例的信号。这个信号用于驱动CP 和LF 为VCO 生成一个参考电压,以确定VCO 是否应该以更高或更低的频率运行。在两路信号进行比较前各有一个分频器M0和M1,其作用是使输出信号的频率达到分数倍的倍频,扩大了可变频率范围。当相位、频率一致时,锁相环进入锁定状态,输出变频变相的信号。

2.2 时标电路

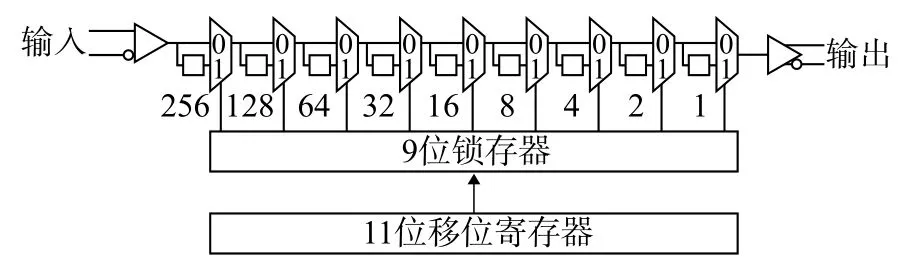

所设计的时标主要由可编程延迟线与电平转换电路两部分组成。延迟线部分使用ON Semiconductor公司的NB6L295M 延迟芯片,该芯片具有两个通道的延迟线,分辨率为11 ps。芯片内部主要电路如图3 所示,一共有9 阶延迟,对应9 位锁存器,通过改变0 或1 决定是否选通来改变最终对信号产生的延迟,移位寄存器则用于存放接收的11 位延迟数据,除去9 位剩下的2 位为模式选择与通道选择。该芯片有两个工作模式:双通道模式下,两条延迟线互相独立,为两个通道的信号分别提供延时;扩展模式下,将两条延迟线级联,以扩大可变延迟范围,但只能用于一路信号。

图3 延迟线电路图Fig.3 Delay line circuit

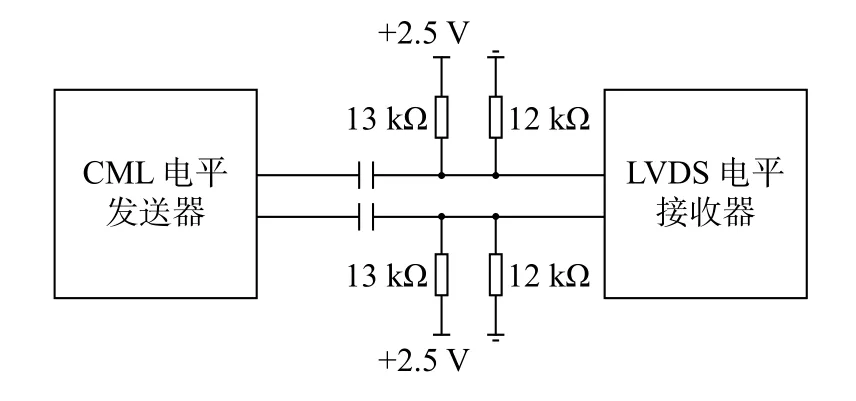

信号经延迟芯片输出后需要传送至FPGA进行下一步处理,该芯片的输出信号为CML 电平,需要将其转换为FPGA 支持的LVDS 电平。不同电平标准之间的区别在于电压所在区间范围的差异,主要由该电平的直流分量决定。电平转换电路如图4 所示,采用交流耦合,用电容隔去直流分量后,经电阻网络分压提供LVDS电平所需的+1.2 V 直流分量。其中,使用阻值较大的电阻以减小电阻网络对100 Ω 差分阻抗线的影响。

2.3 数据处理电路

图4 电平转换电路Fig.4 Level conversion circuit

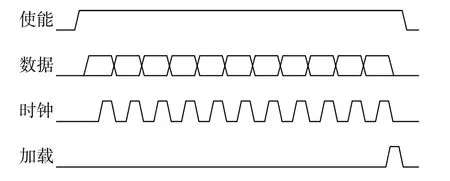

经串口接收的延时数据需要根据一定的时序传送至延迟芯片,控制芯片延时数据加载的一共有4 路信号:使能信号/EN、时钟SCLK、串行数据SDIN 和加载信号SLOAD,其时序关系如图5 所示。

图5 控制信号周期时序图Fig.5 Period sequence diagram of control signals

1)/EN 置高电平,芯片进入数据读取状态,开始接收SCLK、SDIN 和SLOAD;

2)在每个SCLK 的上升沿保存1 位数据,经过11 个SCLK 周期后,延时数据全部保存至芯片内的11 位移位寄存器;

3)SLOAD 置高电平,选定工作模式与通道,把9 位延迟数据D0~D8 赋值给控制通道延迟的锁存器,信号的延迟立即改变;

4)SLOAD 置低电平,/EN 置低电平,延迟数据加载完毕,进入等待状态,准备加载下一组延迟数据。

2.4 组合逻辑电路

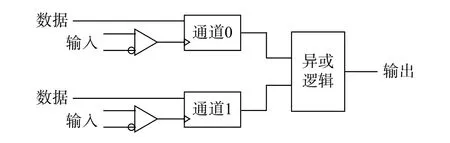

组合逻辑电路的作用是组合输出延时信号。传统方法使用的是多路器,使用异或逻辑门电路是另一种方法,其优点在于不需要时钟信号且电路简单,对原信号的影响较小。图6 所示为信号组合输出的简化电路图,设计为单沿触发。

3 测试与结果分析

图6 组合逻辑电路Fig.6 Combination logic circuit

本文设计的时序发生器通过Xilinx Spartan-7 芯片实现,使用Vivado 设计套件对制作的FPGA 开发板进行编程并下载,分别对200,400,600 Mbit/s 三种速率下的延时、抖动(Jitter)、分辨率、线性度(Linearity)等指标进行测试,并对测试结果进行分析。

3.1 延时与抖动

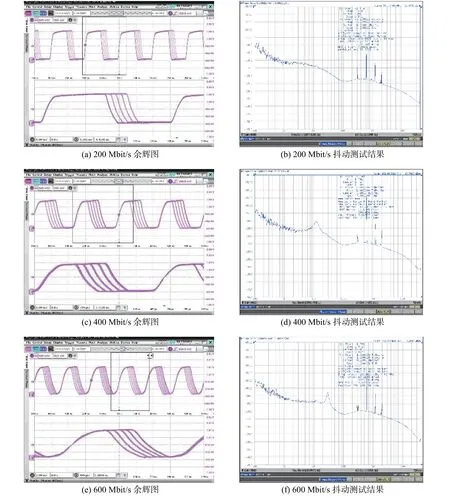

图7 所示为延时与抖动的仪器测试结果,其中,图7(a)、7(c)、7(e)分别对应200,400,600 Mbit/s 的时序信号波形图。在示波器余辉模式下对信号进行若干次等间距延时。根据测试结果,在三种数据速率下都明显实现了延时的功能。

图7 时序信号波形图与相位噪声频谱图Fig.7 Timing waveform and phase noise spectrum

抖动与相位噪声实际是对同一种现象在时域和频域的两种不同定量方式,通过对选定的区间进行积分能将相位噪声转换为抖动[14]。抖动是体现时序发生器性能的重要指标之一,它描述了信号边沿实际位置与理想位置之间的偏差。图7(b)、7(d)、7(f)分别对应使用信号分析仪测得200,400,600 Mbit/s 时的相位噪声频谱图,取积分区间100 Hz 至40 MHz,得到抖动结果分别为7.4,8.9,9.1 ps。经多次测量对比三种情况分析得出:不同数据速率情况下,速率越快,相位噪声与抖动越大;相同数据速率的情况下,不同时延下的抖动结果也会有差异,特别是当两个边沿相距很近时抖动会大幅增加,造成这个现象的原因是此区域为非线性区,信号还未从低电平上升至高电平便开始下降,与理论位置产生很大偏差,降低驱动电压的幅度和增大驱动电流可以改善该现象。

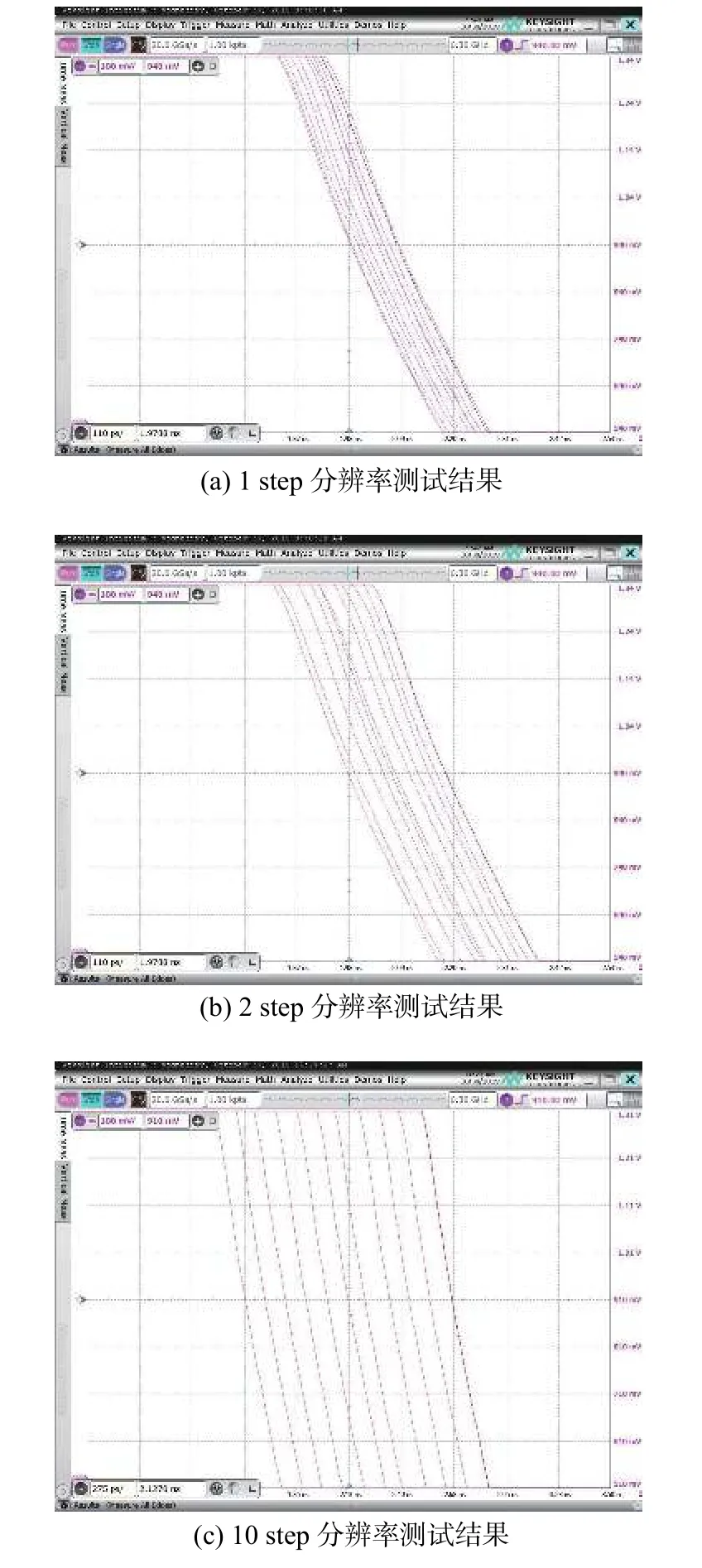

3.2 分辨率

分辨率是时序发生器另一个重要的指标,如图8(a)、8(b)、8(c)所示,分别对应间隔1、2、10 step 情况下的测试结果,其中,1 step=11 ps。综合多次测量对比分析得出:在1 step 情况下两个边沿之间距离明显粗细不均匀,且会出现下一个边沿出现在上一个边沿之前的情况。结合抖动测试结果来看该情况只可能发生在1 step 情况下,这种现象从2 step 开始起没有再出现,相邻边沿之间的距离逐渐趋于均匀,直到10 step,相邻边沿间距均匀,差异不明显。

3.3 线性度

线性度体现了实际曲线偏离理想曲线的程度,常用积分非线性(INL)表示,其表达式为

式(1)表示第i+1 个点与理想曲线的偏差。 τi为第i+1 个点的值; τ0为第1 个点的值;LSB 是单位,为最低有效位,τLSB为LSB 对应的具体数值,表示两个相邻点之间的理想差值,即1 LSB= τLSB。

图8 分辨率测试结果Fig.8 Resolution test results

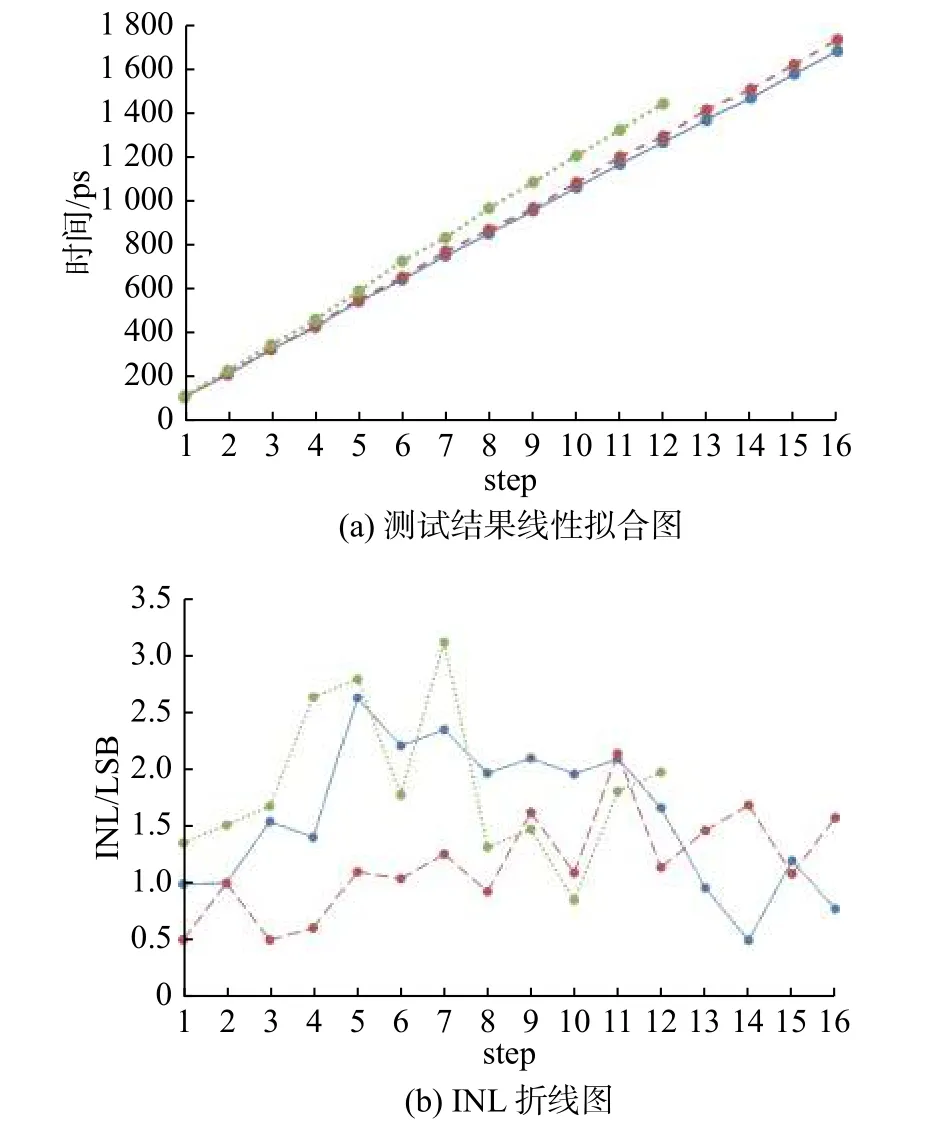

图9 所示为线性度的测试结果,其中,点线、短划线和直线分别对应200,400,600 Mbit/s 下的测试结果,1 step=110 ps,图9(a)为测试结果的线性拟合,图9(b)为INL 测试结果的折线图。 τLSB取对实际测试数据进行直线拟合后的斜率值,测得其结果分别为最大2.6 LSB,2.2 LSB,3.2 LSB。

4 结 论

图9 线性度测试结果Fig.9 Linearity test results

本文提出了激光测距仪时序发生器的一种设计方案,对方案进行仿真与验证,制作了FPGA 开发板并进行测试。测试结果表明,设计的时序发生器具有11 ps 的可变延时分辨率与最高600 Mbit/s的数据速率,具有一定的可靠性与稳定性,实现了预期功能。但在噪声的抑制和印刷电路板布局以及电路的优化等方面仍有可改进的地方,还能进一步提高精度,是后期继续着重研究的方向。