软件无线电接收机的AGC 信号处理算法及控制模型的设计与实现

2020-09-02施扬喜赵利梁仪庆唐俏笑

施扬喜,赵利,梁仪庆,唐俏笑

(广西精密导航技术与应用重点实验室,桂林电子科技大学,桂林 541004)

0 引言

在无线通信系统中,接收信号容易受障碍物、发射机功率大小、发射机与接收机之间距离及接收机位置变化等多因素的影响[1],使得天线接收到的信号强度出现较大的起伏变化,以致信号过小造成有用信号丢失,过大会过载失真,接收机可能无法正常解调信号,降低了接收机的性能。因此,为提高接收机信号接收及解调性能,接收机必须具有自动增益(AGC)调控功能,随输入信号强度变化自动调整,使输出基带信号强度稳定在目标阈值。

传统的无线电接收机一般采用模拟射频电路完成AGC 电路设计[1],存在调试复杂、精度不高及控制不灵活等问题。而在目前软件无线电技术应用的背景下,运用数字信号处理技术在数字基带完成数字AGC 的设计实现,具有调整灵活、稳定性好,得到广泛关注。

现有的数字AGC 算法往往采用非线性AGC 控制,算法复杂,需要通过ROM 存储的相关参数查表来输出控制数据,工程实现需要消耗较多硬件资源[2],且与不同的射频前端电路匹配性不好。本文采用软件无线电设计思想,针对LMS6002D 射频前端电路,在对射频前端大量分析测试的基础上,采用合适的信号处理算法,建立近似线性化的AGC 控制模型及控制机制,并在FPGA 基带信号处理平台上,设计完成相应的AGC 功能,实现接收信号的高动态和快速的AGC调整。

1 AGC信号处理算法的设计

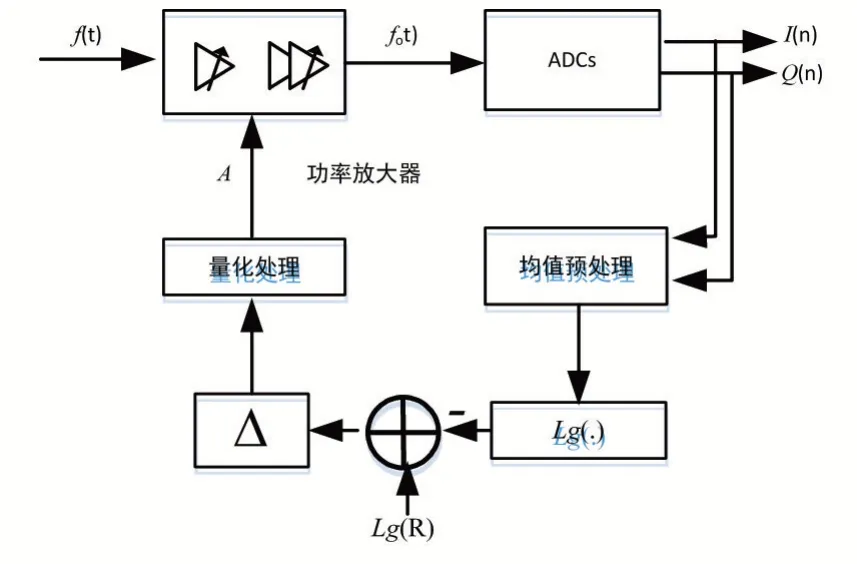

接收信号的自动增益控制AGC 采用闭环负反馈控制结构[3],实现信号电平幅值的自动调整。结合采用LMS6002D 射频前端电路的软件无线电接收机的结构,为了实现AGC 控制模型的线性化,采用幅值对数数字AGC 方法,AGC 信号处理算法结构如图1 所示。其中,f(t)为射频前端电路下变频后的中频(或基带)信号,I(n)、Q(n)为经过基带滤波和可编程增益放大等操作后作模数量化(ADC)处理得到的数字中频(或基带)信号。AGC 基带信号处理算法是对I、Q 路数字采样信号先做均值,后做平方和处理获得基带信号功率,再取对数运算,从而获得与接收信号功率具有近似线性关系的检测信号。在建立相应AGC 控制模型的基础上,把检测信号值与目标阈值做差,并将差值量化后,作为调整功率因子A,动态调整可编程放大器增益,以闭环负反馈的形式,周期性持续调整,实现AGC 功能。

图1 数字AGC信号处理算法结构框图

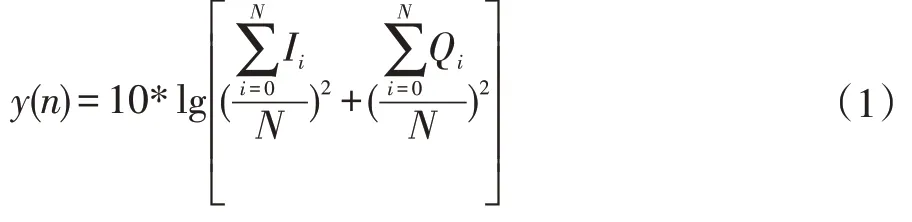

为了提高AGC 的调整性能,使输出信号更加平稳,取I、Q 路的平均能量作为比较参数,即采样N 点作均值处理。为了降低计算的复杂度,方便FPGA 算法的设计,首先分别对I、Q 作均值运算,在作平方运算,最后取对数,其基带检测信号功率y(n)计算为:

为了实现AGC 控制,需要设置控制参考阈值yref。当y(n)<yref时,需要增加射频前端可编程放大器的增益。同样地,当y(n)>yref时,需要降低射频前端可编程放大器的增益。

为了运算和控制方便,可以进行如下操作。首先,按照式(2)计算误差信号,用于确定相对于参考信号的信号增益误差。然后,按照式(3)计算增益补偿因子a(n),用于确定需要补偿调整的增益值。其中,k 为控制模型的线性斜率值,c 为量化系数。

最后,按照式(4)调整可编程放大器增益。

由此,AGC 输入端的信号fo(t)由下式(5),通过负反馈循环调整,实现AGC 控制功能。

2 AGC控制模型的建立

目前,FPGA 对AGC 数字化程序设计主要采用查表法来调整功率因子A,即作对数处理后的差值Δ 存入ROM 中,通过建立映射关系查找A,此类方法需要消耗较多的硬件资源,并且调整的功率范围越大及采集的数据量与ROM 的资源消耗成正比。为了提供控制效率,节约ROM 硬件资源,可以在对接收信号功率与检测信号大小进行大量测试和分析的基础上,建立近似线性化的AGC 控制模型,来简化AGC 的设计与实现。

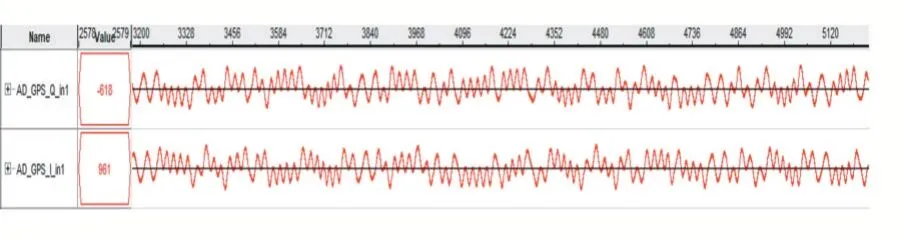

首先,确定射频前端电路的ADC 变换器输入信号的动态范围,通过实验测试分析,在合适的参数配置下,ADC 在输入射频信号功率为-58dBm 到-38dBm时,可以保证正常的工作状态。然后,为了观测输入射频信号x(n)功率与基带检测信号y(n)大小的关系,发射端信源可以逐次设置-58dm 到-38dBm 且间隔为1dBm 的传输信号。软件无线电接收机经馈线接收高频测试信号,由射频前端完成信号下变频及模数转换,分别得到I、Q 两路数字中频(基带)信号,并送至FPGA信号处理器,完成对I、Q 信号的采集处理及提取。由此,可以通过Quartus II 13.0 的在线逻辑分析仪观查并保存提取采样信号数据,发射功率为-44dB 时,接收机获得的I、Q 两路数字中频信号的采样观测信号如图2所示。

图2 I、Q采样信号波形图

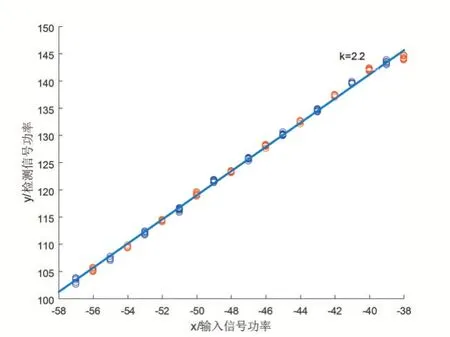

同时,也可以生成数据文件,采用MATLAB R2016b 软件处理,按照AGC 信号处理算法,由式(1)分别对这21 组采样数据做均值、平方及取对数运算,获得到输入信号功率与检测信号功率关系曲线,如图3所示。

图3 输入信号功率x(n)与检测信号功率y(n)关系曲线

由图3 可见,曲线呈近线性且均匀分布在斜率为k的斜线附近,其中,k=(ymax-ymin)/(xmax-xmin),由此可以获得近似线性化的AGC 控制关系。为获得最大的线性控制范围,选择AGC 调整控制参考点为曲线中心位置(-44,134),即调整接收机输出中频信号检测值稳定在134 附近。由式(2-5)可建立AGC 控制的线性数学模型,如式(6)。

按照实验测试数据分析,上式中k 取值为2.2,yref取值为134。

3 AGC硬件结构

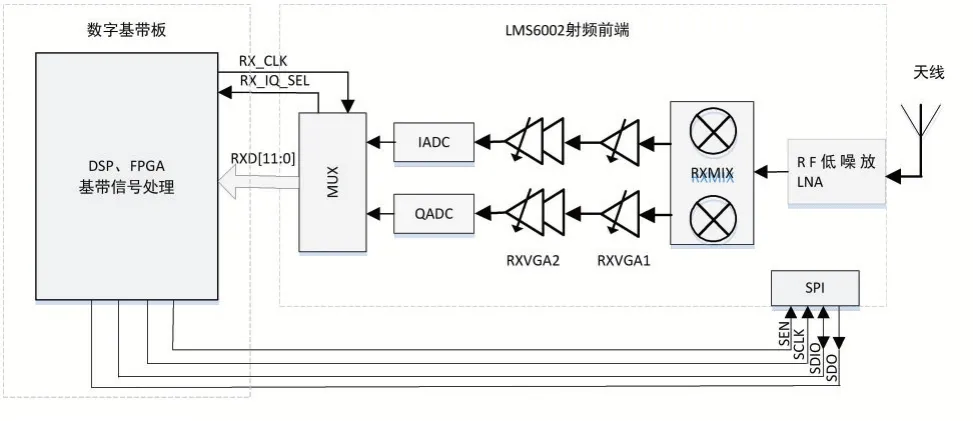

软件无线电接收机由数字基带板(DSP+FPGA)和射频前端(LMS6002D)两部分组成[4],可以采用已建立的AGC 控制模型和设计的信号处理算法,在软件无线电接收机的FPGA 上完成AGC 硬件的设计[5],AGC 硬件结构如图4 所示。其中,数字基带板的FPGA 完成信号处理算法的运算,并按照AGC 控制模型获得需要调整的增益参数,通过SPI 接口快速反馈控制射频前端LMS6002D 的增益放大器完成AGC 的功能。

现场可编程逻辑门阵列选用Altera 公司Cyclone II系列,型号为EP2C70F672 的FPGA 芯片,有丰富的门资源、运算快、时序性强及低功耗等特点,满足AGC 系统高动态快速调节的要求,主要完成数据采集、基带信号处理、射频前端的通信配置等操作;射频前端选用Lime 公司的可现场编程的单芯片收发器,多标准多宽带射频端的LMS6002D 模块,该模块高度集成了数模/模数转换、低通滤波、中频信号放大、低噪放大、混频器及频率合成器等模块[6],且有3 个输入通道,完成高频信号低噪放大、数字下变频、滤波、功率放大及模数量

化为数字中频信号等接收射频处理。

图4 AGC硬件结构

LMS6002D 的模数转换ADC 为12 位,最高采样率为50MHz,有61dB 的接收功率调整范围,包括6dB 低噪放RXLNA、25dB 的中频放大器RXVGA1 及30dB 的二级中频放大器RXVGA2,RXVGA1 有5dB、19dB、30dB 三种功率设置,RXVGA2 功率控制步长为3dB,即量化系数c 为3。可通过RXLNA、RXVGA1 的配置完成AGC 的初始化设计,在通过RXVGA2 完成AGC的微调整,完成AGC 的总体设计。

FPGA 与射频前端连接完成数据通信与配置,连接信号主要有接收时钟RX_CLK、I、Q 路信号采样时钟RX_IQ_SEL,其中RX_IQ_SEL 时钟是RX_CLK 内部电路二分频产生的,12 位复用数据总线RXD[11:0],及LMS6002D 寄存器配置串行端口接口SPI 线,包括输入/输出SDIO、输出SDO、使能SEN(低电平有效)及时钟SCLK(上升沿触发),其中最高时钟频率为50MHz且完成一次指令操作需要16 个时钟。其中RX_CLK驱动LMS6002D 完成ADC 采样并通过内部MUX 模块电路将模数量化后的I、Q 路数字信号以IQ 或QI 顺序传送至总线RXD[11:0],FPGA 通过RX_IQ_SEL 对总线RXD[11:0]的IQ 数据采样提取,然后完成数字信号基带处理,并将处理好的AGC 相关参数通过串行端口接口SPI 配置LMS6002D 的相关寄存器。

4 AGC控制功能的设计与实现

对AGC 系统进行数字逻辑设计[7],并在软件无线电接收机上完成软件设计实现高动态AGC 快速调整设计。为保证接收机AGC 的高动态、快速调整性,并保证每次均值处理能完成至少一次SPI 指令配置,需要计算均值处理采样点数N,鉴于软件无线电接收机的系统时钟RX_CLK 为39MHz,可以设置基带信号采样时钟RX_IQ_SEL 为19.5MHz 及SPI 配置时钟为5MHz,即SPI 完成一次指令操作为3.2us,为方便硬件描述语言Verilog HDL 除法操作,N 值可取128,即每次均值处理采样时间约为6.56us。

FPGA 通过RX_IQ_SEL 边沿触发,驱动ADC 采样,获得I、Q 路信号数据I(n)和Q(n),并存在12 位的寄存器中,然后分别累加N 次采样值,再通过移位的方法求I、Q 路信号的采样均值。之后对均值做平方运算,经过整型转浮点型IP 核和处理送入以10 为底对数IP 核完成对数处理并将结果以浮点型存在32 位寄存器中。为了能满足处理精度要求,保留一位小数,并得到平均幅值对数值,即检测信号采样序列y(n)。按照AGC 控制机制,检测信号采样序列y(n)与控制参考阈值134 做差,并线性解算求出此刻的增益调整值a(n),并做量化系数c 为3 的量化处理,最后通过SPI将调整值配置到地址为0x65(RXVGA2)或0x76(RXVGA1)寄存器中完成增益调整。若调整值较大,则优选配置第一级可编程放大器RXVGA1 做粗调,再做第二级可编程放大器RXVGA2 细调;若值较小,则保持RXVGA1 不变,直接调整RXVGA2。只要AGC 控制电路不断周期性高速循环更新调整可编程放大器,即可完成AGC 功能。

软件设计采用自底向上层次化设计方法[8],将系统分为若干个子模块,在Quartus II 13.0 软件环境中完成算法、电路及布线等设计,总体的寄存器传输级电路(RTL)电路结构如图5 所示。

图5 AGC寄存器传输级电路结构

整个系统主要由基带信号处理模块、整型转浮点型处理模块、对数处理及射频前端配置模块这5 个模块组成,程序算法设计与IP 核协同控制射频前端的可变增益放大器完成中频信号电平的调控,满足ADC 对输入信号幅度的要求。

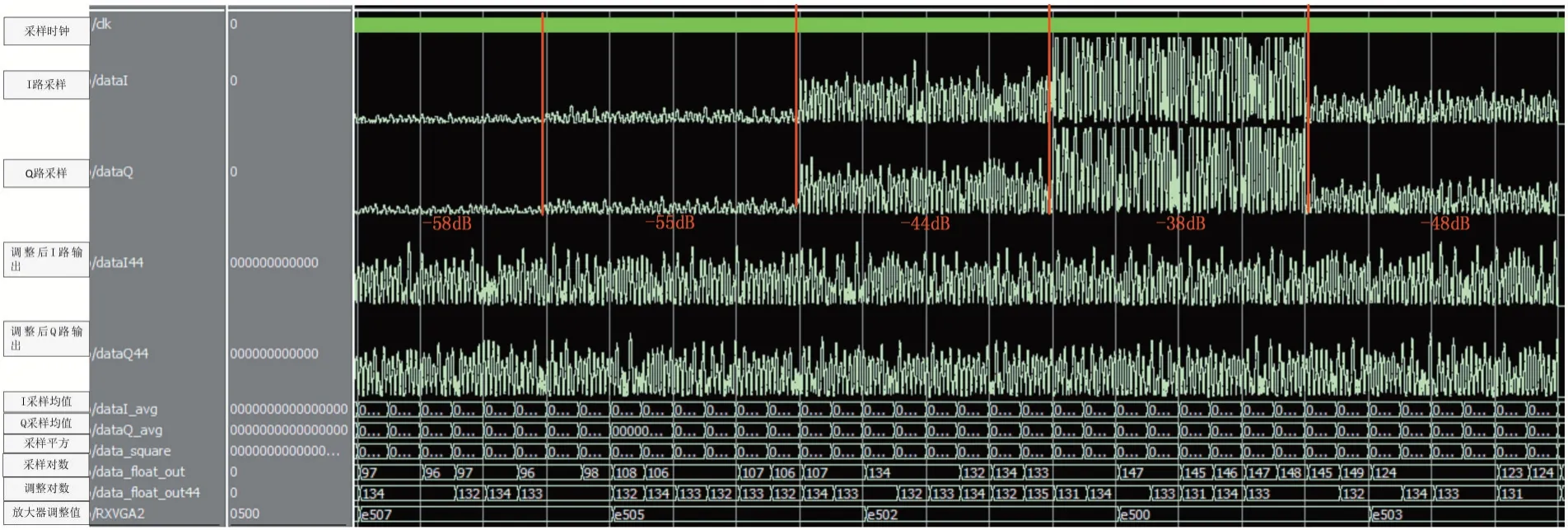

为了更直观地验证基于控制模型和算法以及AGC硬件设计的正确性,在Modelsim-Altera 10.1d 仿真环境对RTL 电路进行功能仿真验证,AGC 电路的仿真输出结果如图6 所示。其中,dataI、dataQ 为待调整的IQ路采样信号,分别对应发射功率为-58dB、-55dB、-44dB、-38dB、-48dB 的采样信号,-58dB 对应信号电平强度较小,-38dB 对应信号电平强度较大,已出现部分失真。clk 为IQ 采样时钟,data_float_out 为待调整信号的检测功率,RXVGA2 为地址0x65 寄存器的微调写入值,dataI44、dataQ44 为调整至检测功率yref附近的IQ路采样信号,由data_float_out44 可知,调整后信号检测功率在134 左右。

仿真验证结果表明,信号电平强度较小时增大RXVGA2 增益,强度过大降低RXVGA2 增益,系统时序逻辑设计正确,达到快速稳定动态输出信号的目的。

图6 AGC系统建模的FPGA仿真输出结果

5 结语

本文完成了一种AGC 控制算法和控制模型以及软件无线电接收机高动态、快速AGC 调整电路的设计。首先FPGA 对总线RXD[11:0]的I、Q 路数字信号采样,在对I、Q 采样幅值做均值、平方、对数预处理,然后根据建立的控制模型量化处理增益调整值,最后通过SPI 配置射频前端放大器完成AGC 调整。通过设计采样时间6.56us 及SPI 配置时间3.2us 实现系统高动态、快速处理,并根据AGC 控制模型完成FPGA 数字逻辑设计,很大简化了FPGA 的设计且节约了硬件逻辑资源。最后通过采样数据仿真实验表明,基于AGC 模型的设计能高动态、快速调整并稳定输出信号,提高了接收机的动态性能。