以太网IP核的FPGA验证

2020-08-24蔡玉辉

蔡玉辉

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引言

随着网络技术的高速发展,以太网已在通信、控制、传输领域得到了普遍的应用。目前对集成网络功能的SoC(System on a Chip)芯片的应用需求量也在快速增长。在实际的科研与应用中,FPGA验证被广为采用,因其可以快速定位SoC芯片的设计缺陷,同时兼能进行软件程序开发,进而缩短整个项目的开发周期[1-2]。在此,首先介绍基于FPGA的以太网验证平台的软硬件架构,然后详细阐述基于该平台的以太网IP核的验证工作过程。

2 以太网IP核验证平台系统架构

以太网基于TCP/IP协议[3],其参考模型如图1所示。其中数据链路层和物理层由硬件实现;应用层、传输层、IP层则由软件实现。数据链路层分为逻辑链路控制层LLC和媒体访问控制层MAC。此处需要验证的IP核为MAC层的功能。对MAC控制器的功能验证采用软硬件协调验证的方法[4]。该验证系统的硬件平台及软件平台架构简介如下:

图1 TCP/IP协议参考模型

硬件平台:该以太网硬件平台采用母板+子板的结构。母板采用Xilinx公司的Kintex-7 325T FPGA,最大容量是325万门。子板主要集成以太网的PHY芯片、JTAG调试接口、串口、LED、按键等功能。PHY芯片选用的是DAVICOM公司的DM9161芯片。子板与母板之间是通过接口FMC-HPC连接,连接结构框图如图2所示。

图2以太网FPGA验证平台结构框图

软件平台:该软件平台主要是基于轻量级的TCP/IP协议族——LWIP。LWIP的主要目的是减少存储器利用量和代码尺寸。LWIP更适合应用于小的、资源有限的嵌入式系统。该验证系统是基于LWIP协议开发的软件验证程序,测试代码使用嵌入式C语言[5-6]编写。

3 以太网IP核验证

系统采用硬件描述语言Verilog HDL实现逻辑功能[7],以Xilinx Vivado 2016.4为电路开发运行环境,以VCS为软件仿真环境完成系统的功能设计。网络通信的链路一端为Kintex-7 325T FPGA,另一端为PC机。PC端使用WireShark软件抓取链路上收发的以太网数据。

以太网IP核的功能验证按照以下步骤进行调试验证:

(1)寄存器验证

首先对MAC控制器所有寄存器进行复位值、读写寄存器的验证。

(2)MDIO接口控制

MDIO是MAC控制器和PHY之间的管理接口。该接口是通过时钟MDC和数据MDIO两根信号线来访问PHY寄存器。验证第一步首先是要保证该接口时序正确,通过该接口完成对子板上PHY芯片的控制。通过MDIO接口访问PHY芯片的总线接口时序如图3所示。

图3 MDIO接口时序

(3)数据链路建立

当完成PHY寄存器的初始化后,FPGA端与PC端进行自协商,确定通信模式及通信速率,由于设计的网卡是10M/100M以太网,因此自协商结果一般为100MHz、全双工的工作模式。

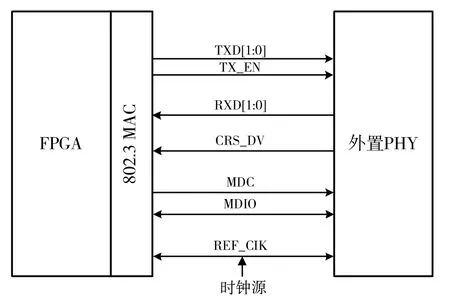

(4)RMII接口通信

精简独立介质接口RMII相比于独立介质接口MII,减少了以太网模块和外部PHY之间的连接引脚数。以太网的MAC与PHY通过RMII接口连接,如图4所示。编写不含网络协议的软件测试程序,其目的是测试MAC层收发帧的时序是否正确。RMII接口的以太网时钟信号频率为50MHz,数据帧通信的波形如图5所示。

图4 RMII接口

图5 RMII接口通信波形

(5)PING程序调试

在完成MAC帧收发调试后,基本可证明MAC IP核硬件平台功能正确,基于此,编写基于LWIP协议的PING程序,此程序基于ICMP(Internet Control Message Protocol,因特网控制报文协议),通过ICMP发送请求和回送应答来验证整个网络的连接性。

(6)UDP收发测试[8]

完成IP层测试后,可证明MAC控制器的功能及硬件板卡的设计基本正确。基于此,开发UDP的测试程序,完成传输层数据的收发测试。PC机使用周立功的TCP&UDP测试工具,其运行结果如图6所示。

图6 UDP测试结果界面

(7)典型应用协议调试

在完成以上所有测试工作后,编写基于Telnet、Http、FTP等协议的应用层的程序,最终完成典型的应用协议的测试。

4 结束语

在网络技术高速发展和物联网兴起的背景下,研究了以太网IP核基于FPGA的验证工作,基于该平台,完成了对以太网MAC控制器的功能验证,同时进行了软件程序开发,大大缩短了项目开发周期。