面向宇航应用的高可靠SoC异常处理系统设计*

2020-07-22孙川川高瑛珂李圣龙赵云富梁贤赓

孙川川,高瑛珂,李圣龙,赵云富,梁贤赓

0 引 言

随着空间技术的发展,面向宇航应用的电子系统朝着小型化、集成化、高性能、低功耗等方向发展[1].片上系统(SoC,system on chip)是一种系统级集成化设计方案,即在单芯片上集成处理器、存储器、外设控制器、IO接口等模块,在集成度、性能、成本、功耗、可靠性等方面具有优势,良好地契合了空间电子产品的发展需求,得到了广泛研究和应用[2-3].与商用SoC应用相比,面向宇航应用的SoC由于复杂的空间环境等因素,对可靠性提出了更高的要求,需要进行可靠性设计[4-5].处理器在程序正常执行过程中,需要处理外设中断请求以及程序执行时出现的各种异常、错误情况,可以将复位、外设中断请求、存储器数据访问中止、指令执行异常等统称为异常.随着片上系统功能、复杂度增加,高效、可靠地处理各种异常,对于提高SoC性能及可靠性具有重要意义[6].

本文实现了面向宇航应用的高可靠SoC异常处理系统设计,为提高系统可靠性,一方面处理器及异常处理系统寄存器进行冗余设计;另一方面在SoC片上SRAM及各外设存储模块引入硬件EDAC检错/纠错(纠一检二)机制[7].采用中断控制器统一管理众多的外设中断请求,通过软件配置中断源的使能、禁止、判优、屏蔽等功能[8].对存储模块EDAC校验逻辑产生的一位错和二位错异常采用不同的硬件处理机制,一位错通过中断控制器以异步异常方式处理,二位错通过总线反馈信号以精确异常方式处理,保证了异常响应的效率和系统可靠性.

1 异常/中断处理基本机制

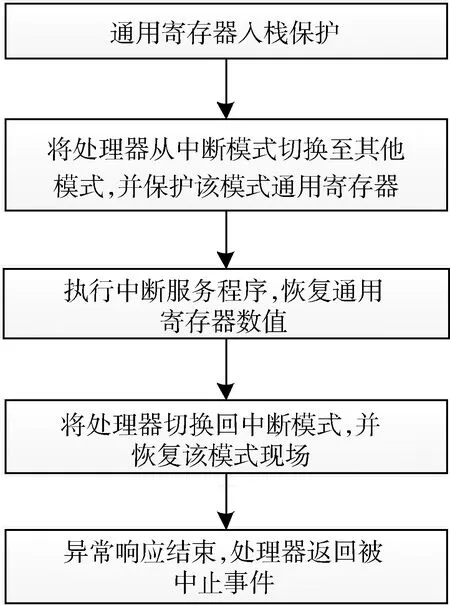

SoC系统中存在不同类型的异常,例如数据访问异常、指令访问异常、指令执行异常、外设中断请求等.外设中断请求又可根据响应速度分为普通外设中断和快速外设中断,快速外部中断优先级更高、响应速度更快,常用于对实时要求高的外设中断.数据访问异常是存储器数据访问出现的异常,例如地址未对齐、地址不存在、地址不允许方问等;指令访问异常是取指令时产生的异常,在相关指令的执行阶段将异常信息传递给处理器.指令执行异常是在协处理器指令不可用、协处理器指令执行时产生异常、执行一条没有被定义的指令(指令集之外的指令)或者被除数为零时产生的异常.通常采用中断控制器负责管理众多的外设中断请求,并最终将有效的中断信号以普通外设中断或者快速外设中断传递给CPU.处理器对不同异常的响应过程是相似的,如图1所示,都要经历保护现场、执行异常服务程序、恢复现场与返回的过程.CPU开始响应异常时,中止当前正在执行的事件,由硬件自动切换到响应异常的模式,硬件自动将程序计数器和程序状态字寄存器的值保存.然后根据异常响应程序的入口地址,自动跳转至异常响应程序.在异常响应程序的入口地址由软件实现通用寄存器的入栈保护,然后跳转到异常服务程序.异常服务程序执行完后,由软件恢复程序计数器、程序状态信息和通用寄存器的值.异常响应结束,CPU继续处理被异常响应中止的事件.

图1 异常响应基本流程Fig.1 Basic exception handling procedure

在本文的设计中,采用中断控制器统一管理众多的外设中断请求,中断控制器可实现各个中断源的使能、禁止、判优、屏蔽等管理功能[8].在片上SRAM、外部存储模块(EMIF)、外设控制器RAM等存储模块引入硬件EDAC逻辑,实现存储单元的检错和纠错功能,产生数据/指令的EDAC校验一位错和二位错异常信号,对一位错和二位错引入不同的硬件处理机制,以兼顾异常响应的实时性和效率.由于硬件EDAC逻辑具有纠正一位错的功能,一位错不影响处理器正常运行,将一位错异常通过中断控制器以外设中断方式传递给CPU处理;二位错不能通过EDAC逻辑纠正,影响处理器指令执行,二位错异常通过总线实时反馈给处理器,以精确异常方式处理.

2 中断控制器及仿真验证

本文异常处理系统设计中采用中断控制器管理众多的外设中断源,除了外设发起的中断请求,还包括各个存储模块引入EDAC逻辑后产生的一位错信号,例如SDRAM一位错、EMIF一位错、1553B一位错等.为提高可靠性,本文将中断控制器的寄存器进行了冗余设计.

图2 采用中断控制器的中断处理架构Fig.2 Interrupt handling model using interrupt controller

每一个连接到中断控制器的中断源都有一个唯一的中断号,处理器通过中断号识别连接到中断控制器的中断源模块,然后通过各个模块内部的中断状态寄存器查找具体的中断源,并进行相应的中断处理.采用中断控制器的中断处理架构如图2所示.中断控制器可通过软件配置将众多的中断源以普通外设中断或者快速外设中断的方式传递给CPU.其中快速外设中断的优先级高于普通外设中断,并且响应速度更快,通常用于对响应实时性要求高的中断请求.在设计中,通过软件配置中断控制器实现各个中断源的使能、禁止、优先级判定、屏蔽等管理功能.

根据图1的异常响应流程,在响应异常时,硬件根据异常类型自动跳转至异常响应程序执行,在异常响应程序的设计中,需要考虑异常嵌套的情况[9-10].以外设中断例,当处理器响应外设中断请求时,硬件自动将处理器切换至相应模式并跳转至外设中断入口地址开始执行.将通用寄存器压入堆栈保护后,由于响应中断时硬件自动保存程序计数器数值,函数调用时的返回地址和中断的返回地址保存在同一寄存器中,为防止函数调用时产生中断嵌套,将函数返回地址覆盖,导致程序不能正常返回,保护现场后将处理器模式切换至其他模式进行中断处理,跳转到中断服务程序后打开相应的中断屏蔽位使能中断嵌套,中断服务程序完成后再切换至中断模式,完成现场恢复后,CPU返回被中止的事件继续执行.

图3 考虑嵌套的中断响应程序设计Fig.3 Interrupt handling program design considering interrupt nesting

处理器在接收到中断控制器有效信号后,并不会立即终止指令执行,而是执行完后续流水线中的指令后,再响应中断请求,这种机制保证了处理器的执行效率.数据/指令的EDAC校验一位错可以由硬件逻辑自动更正,不需要cpu立即响应,因此可以通过中断控制器处理.中断控制器相关功能经过VCS仿真和FPGA板级验证,结果验证了设计的正确性.外设中断请求嵌套的VCS仿真波形如图4所示,图中所示为EMIF区EDAC校验一位错中断(single_err_int)和向OR区写入数据中断(wr2or_err_int),后者的优先级比前者高,实现了中断嵌套.clk为系统时钟,mode_i为处理器的模式标志信号,9代表管理模式,8代表中断模式.中断控制器在接收到外设的中断信号后,经过1~10个clk后将有效的中断请求信号传递给处理器,处理器在接收到有效信号后并没有立即响应,而是继续执行了流水线中的指令.将已经预取的指令执行完毕后,再响应中断请求,保证了处理器指令执行的效率.在产生中断的指令后设计了标记程序,结果表明后续标记指令在中断响应前已执行.过了约400个clk后,切换处理器状态开始响应中断.在中断的服务程序中,将标志位清除,外设撤销中断请求信号.仿真结果表明,整个中断响应过程正确无误.

图4 外设中断嵌套响应仿真波形,图(b)为图(a)中实线框中放大部分Fig.4 Simulation results of peripheral interrupt nesting. Figure (b) is enlarged view of figure (a) marked with solid wireframe.

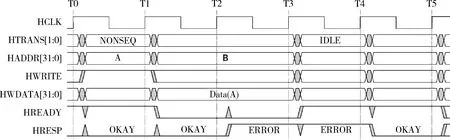

图5 总线RESP错误信号时序示意图Fig.5 Timing diagram of bus RESP error signal

图6 数据校验双错响应仿真波形,图(b)为图(a)中实线框中放大部分Fig.6 Simulation results of EDAC double error handling. Figure (b) is enlarged view of figure (a) marked with solid wireframe.

3 EDAC二位错处理及仿真验证

为提高系统可靠性,在SoC的各存储模块引入EDAC校验(纠一检二)逻辑.与数据/指令EDAC校验产生的一位错不同,二位错异常不能被硬件逻辑自动更正,会直接影响处理器指令的继续执行,需要被立即响应,而经过中断控制器传递给CPU中断请求不会被CPU立即响应,因此二位错异常不能通过中断控制器传递给处理器,否则CPU使用了取回的错误指令或数据,会导致程序出现错误结果.CPU及各片上模块通过总线互连,总线提供了从设备传输反馈信号RESP.从设备可用RESP信号告知主设备传输的正确与否,该信号可用于表示向只读区的写保护错误等.图5所示为总线RESP信号反馈ERROR的时序示意图,T1时刻传输地址A及其控制信号,T1-T2为插入的等待状态,T3时刻检测到反馈的ERROR信号,T4时刻主设备将总线传输状态更改为IDLE,取消地址B的传输,并将READY信号置为有效.

在硬件设计中,将片上SRAM、EMIF、1553B总线、SPW、SD RAM等存储模块的校验错误信号通过总线RESP信号传递给处理器.对于数据和指令访问的二位错异常,处理器分别以数据访问异常和指令访问异常进行处理.对于不同区域的数据访问异常,设计了一个寄存器用于查询发生多位校验错的地址,异常服务程序中根据校验错地址分别进行处理.

采用VCS仿真和FPGA板级验证的方法验证了设计的有效性.图6所示为处理器响应EMIF存储空间EDCA校验双错异常的仿真波形图.clk为系统时钟,mode_i为处理器的模式标志信号,9代表管理模式,a代表数据数据访问异常模式,异常响应前处理器运行在管理模式,开始响应数据异常时,处理器自动切换至数据异常模式.数据访问异常的产生是随机的,因此数据访问异常的响应程序必须考虑异常嵌套的情况.具体的响应程序结构与外设中断类似,都是在对应的异常模式下保护现场后,切换到管理模式进行异常响应,异常响应结束后,再切换回数据异常模式恢复现场.数据访问异常和指令访问异常的响应过程是类似的,不同之处在于异常响应程序的入口地址不同,具体的异常处理由软件实现.仿真验证中,在数据访问指令后设计了标记指令,产生数据异常后,CPU没有执行后续指令.从图中可以看出,从EDAC校验二位错信号产生到处理器切换到数据异常模式处理该异常,只经过了不到40个时钟周期.数据访问异常产生后,处理器立即进行响应,并没有继续执行后续指令.这种精确异常处理机制,保证了指令和数据校验二位错的有效性和实时性.

4 结 论

本文基于一款面向宇航应用的高可靠SoC,实现了其异常处理系统设计.采用中断控制器处理众多的外设中断请求,为提高系统可靠性,对SoC的存储资源引入了硬件EDAC检错、纠错机制,产生校验一位错和二位错异常信号,将不影响处理器运行的一位错异常通过中断控制器以异步中断方式传递给处理器;将影响程序执行的二位错异常通过总线反馈信号以精确异常方式处理.仿真结果表明,该异常处理系统可正确处理各种处理器内部及外设异常.