130 nm加固SOI工艺的抗辐射控制芯片设计

2020-07-10常永伟刘海静董业民

常永伟,余 超,2,刘海静,王 正,董业民,2

(1. 中国科学院上海微系统与信息技术研究所 信息功能材料国家重点实验室, 上海 200050;2. 中国科学院大学, 北京 100049)

随着网络及通信技术的迅速发展,实时通信、定位导航等领域对航天器如卫星通信的依赖度越来越高,同时也对航天器中电路系统的稳定性和精确度提出了更高的要求。而地球周围复杂的空间辐射环境使得电路系统的可靠性逐渐成为航天技术进一步发展的瓶颈。

绝缘体上硅(Silicon-On-Insulator, SOI)器件与体硅器件相比,由于其埋氧层实现全介质隔离的特殊结构,其在空间抗辐射领域具备一定的先天优势[1-3]。另外,SOI互补金属氧化物半导体(Complementary Metal Oxide Semiconductor, CMOS)器件还具有寄生电容小、高速、低功耗、集成度高、适用于小尺寸器件的优势[4]。

然而,总剂量电离辐射会在氧化物中产生陷阱电荷和界面态。SOI器件由于其埋氧层的存在,总剂量辐射效应更加复杂[5]。对 SOI 器件以及电路的抗总剂量辐射加固需要首先深入研究其总剂量辐射损伤的机理,在这个基础上对器件及电路从各层次上进行加固设计。

本文应用总剂量辐射加固SOI晶圆材料及中国科学院上海微系统与信息技术研究所开发的130 nm部分耗尽绝缘体上硅(Partially Depleted Silicon-On-Insulator, PD-SOI) 抗辐射标准单元库设计了一款基于比例、积分、微分(Proportion, Integral and Differential, PID)算法的专用集成电路(Application Specific Integrated Circuit, ASIC)控制芯片,所用单元库在版图上使用H型栅进行总剂量辐射加固。芯片规模约80万门,采用CQFP164陶瓷管壳封装,在基础功能测试通过后进行总剂量辐照试验。试验在模拟空间辐射的环境下进行,结果表明被测试芯片的总剂量加固能力达到300 krad(Si),可以完全满足空间应用的需求。

1 基于PID控制算法的芯片设计

1.1 PID控制算法分析

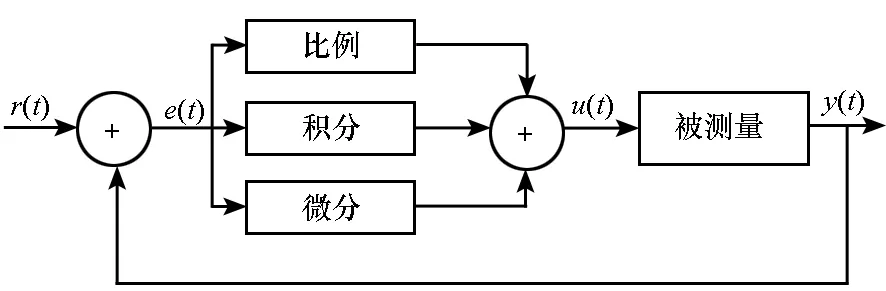

图1为PID算法的原理示意图,PID控制采用比例、积分、微分方法进行闭环控制,具有架构简单、易于实现、鲁棒性强等特点[6]。比例控制是控制器输出与输入之间呈现比例关系,比例系数的大小可以决定偏差调节的快慢;积分控制是控制器输出与输入误差信号的积分成正比关系,积分项的引入会使极小的稳态误差随着时间的积累显现出来;微分控制的作用是控制输入信号的微分与输出成正比,避免被控制量在调控中出现严重超调[7]。

图1 PID控制原理示意Fig.1 Principle diagram of the PID control

PID控制有模拟和数字两种,其中模拟PID控制的计算式为:

(1)

式中:Kp为比例系数;Ti为积分时间常数;Td为微分时间常数;u(t)为PID控制器的输出信号;e(t)为比较模块反馈的误差量。

由于是采用数字集成电路的方法实现PID算法,所以,需对模拟PID算式进行离散等效,离散等效中应用求和替代积分,向后差分代替微分[8],即:

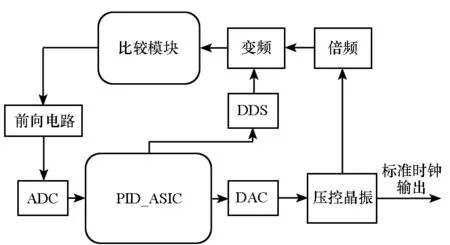

(2)

(3)

根据式(2)~(3)可以得到数字PID计算式为:

(4)

进一步有:

(5)

其中:

(6)

(7)

Δu(k)=u(k)-u(k-1)

=Kp[e(k)-e(k-1)]+Kie(k)+

Kd[e(k)-2e(k-1)+e(k+2)]

(8)

从而,只需要知道增量信号即可进行相应的控制,这样在实现上更加简单易行。

1.2 基于PID控制的系统架构

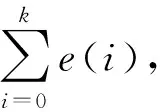

控制芯片基于闭环的反馈系统,其主要任务是通过闭环调节压控晶振,最终向外界输出高精度、高稳定性的标准时钟。如图2所示,反馈系统中,PID_ASIC为算法实现芯片,负责接收由比较模块产生及模数转换器(Analog to Digital Converter, ADC)处理后的误差信号,经过算法计算后产生调节信号,再经由数模转换器(Digital to Analog Converter, DAC)处理产生压控模拟信号对压控晶振进行调节。同时,芯片向比较模块分时输出两组频率字,经直接数字频率合成器(Direct Digital Synthesizer, DDS)合成以及变频转换与压控晶振倍频后的信号合成,作为测试信号输入比较模块与比较模块内的标准信号进行比较,分离误差信号输出。反馈系统设计准确度≤5×10-12,稳定度≤1×10-12。

图2 基于PID控制的系统架构Fig.2 System architecture based on PID control

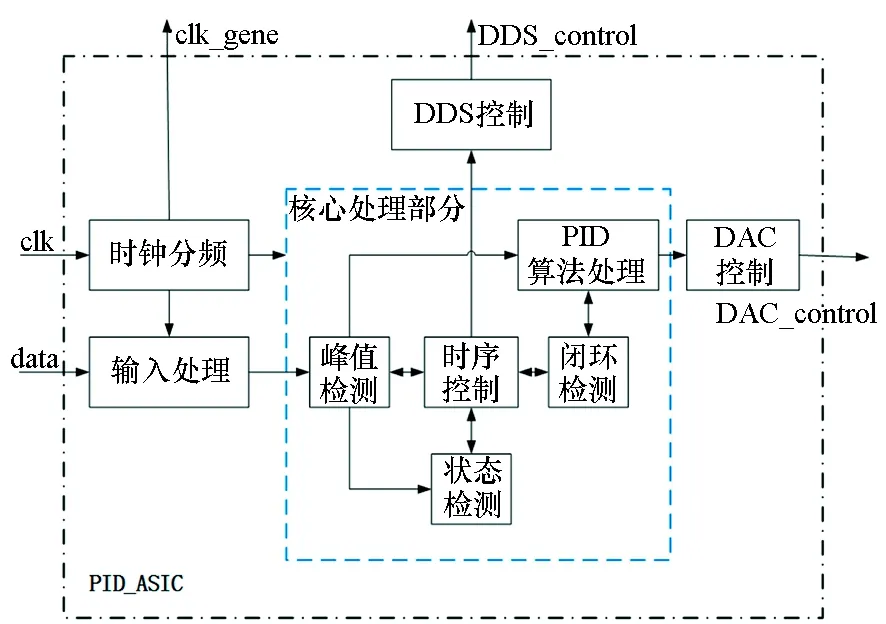

1.3 基于PID控制算法的ASIC设计

图3所示为ASIC系统框架,时钟分频模块的输入clk由反馈系统的压控晶振引入,分别向芯片、外部DAC、外部ADC输出频率相同、相位不同的分频时钟信号;输入处理模块针对误差信号进行时序控制和数据处理;DDS控制模块由核心处理部分控制产生探测信号的频率字;DAC控制模块接收经PID算法处理后的数据并产生对外部DAC的控制信号;核心处理部分主要负责对系统状态的检测、反馈闭环的检测以及增量式PID算法的处理,其时序由核心的时序控制状态机调节控制,其中状态检测模块可实现针对异常状况的自动处理,控制状态机复位重新搜索检测。

在PID算法处理部分,将误差信号进行比例、积分计算,积分项由积分寄存器针对差分值,在每个时钟进行累加并定时输出,其积分值与比例项求和后判断是否越界,并输出数据与相应处理信号,由DAC控制模块根据输入数据及处理信号产生外部DAC调控信号。

图3 芯片内部模块划分Fig.3 Chip internal module partition

2 总剂量效应及加固方法

2.1 总剂量效应机理

总剂量辐射在氧化层中产生电子-空穴对,由于栅氧化层中的电子在室温下是可动的,因此,一部分电子和空穴会发生复合或被其他复合中心捕获,另一部分电子则在电场作用下离开SiO2层。这样,在SiO2层中剩下的是不可移动的空穴,这些空穴陷在SiO2层中产生正的氧化层陷阱电荷Qot[11-12]。式(9)表示了阈值电压Vth的变化量ΔVth的计算关系式:

ΔVth=-e·ΔQot/Cox+e·ΔQit/Cox

(9)

式中,ΔQot为SiO2层中产生陷阱电荷的电荷密度,ΔQit是产生界面陷阱电荷的电荷密度,Cox是氧化层电容,e是电子常数。在空间辐射环境中,虽然辐射剂量率非常低,但MOS器件在空间环境下进行长时间工作时,陷阱电荷的累积会使其性能不断下降甚至失效。

2.2 SOI晶圆的总剂量加固

SOI材料和器件的总剂量辐射效应与辐射感生的氧化物电荷积累有关,其中氧化物主要包括栅氧化层、浅沟槽隔离场氧和绝缘埋层。SOI 器件与体硅器件相比,两者在制造过程中采用了类似的栅氧化层和场氧化层工艺,主要的差别在于是否存在绝缘埋层。显然,SOI 中绝缘埋层是导致SOI 器件的抗总剂量辐射能力不如体硅器件的关键因素。

抗总剂量辐射加固SOI 晶圆的加固方法依赖于Si+离子注入改性工艺,主要利用Si+离子注入在绝缘埋层中嵌入纳米晶,而纳米晶作为电子陷阱能够俘获辐射感生的空穴正电荷或者增加复合中心辐射感生电子-空穴对的复合[13],通过降低辐射产生的净正电荷的累积,来实现绝缘埋层的抗总剂量辐射加固。

本文所用的SOI晶圆采用了目前先进、成熟的注氢层转移技术,该技术将改性离子注入技术整合到注氢层转移技术制备SOI 晶圆的过程中,在键合加固前完成离子改性,从而可以有效地避免顶层硅晶格损伤,可以制备出高质量、高抗总剂量辐射加固SOI晶圆[14]。

2.3 加固晶圆总剂量辐射效应验证分析

为了评估加固SOI晶圆的抗总剂量辐射能力,实际需要将加固SOI晶圆制备成各类MOS 器件,然后对其常规电学特性和辐射环境下的电学性能进行表征和测试。

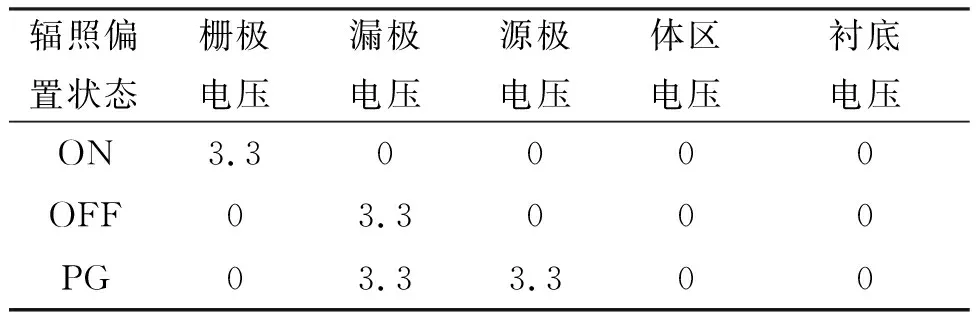

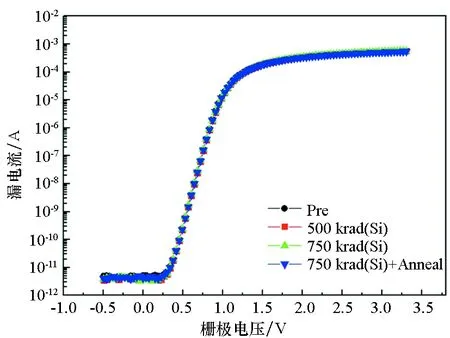

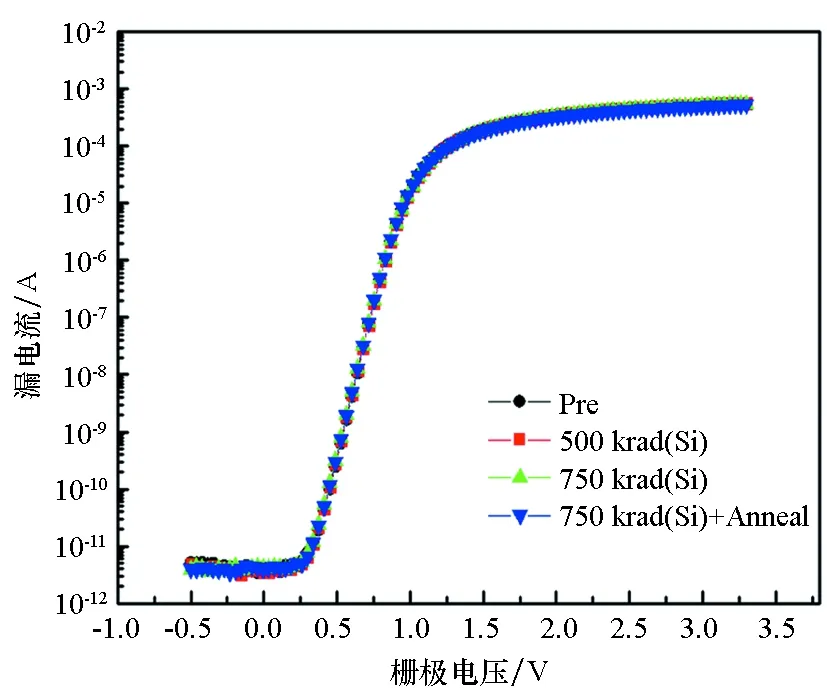

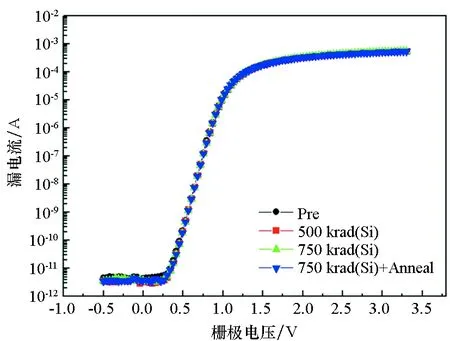

本节主要通过Co60γ 射线辐照实验研究加固SOI晶圆制备的H型栅 3.3 V NMOS器件(宽长比W/L=10 μm/0.35 μm)在不同偏置条件下的辐照效应,主要有开态(ON)、关态(OFF)、传输态(PG)三种偏置态,具体的偏置条件如表1 所示 。

表1 器件的辐照偏置条件

在辐照之前和每一步辐照之后,均采用Keithley 4200SCS 半导体参数分析仪对器件的IDS-VGS 特性曲线进行测量,漏端电压保持为0.1 V。

总剂量辐照实验在中国科学院新疆理化技术研究所开展,辐照源为Co60γ射线,选择的辐照剂量率为200 rad(Si)/s,总剂量范围在500~750 krad(Si),达到设定的剂量点后对器件进行移位测试。退火时温度为100 ℃,退火时间为168 h,退火时加的偏置与辐照时的偏置相同。各个偏置条件下的H型栅3.3 V NMOS器件辐照前后的转移特性曲线如图4所示。实验结果表明:

(a) ON偏置(a) ON-state bias

(b) PG偏置(b) PG-state bias

(c) OFF偏置(c) OFF-state bias图4 加固SOI晶圆制备的H型栅3.3 V NMOS器件辐照前后的转移特性曲线Fig.4 Transfer characteristics of H-Gate 3.3 V NMOS fabricated on the radiation hardened SOI wafers before and after irradiation

在不同偏置条件下,辐照后器件的阈值电压和漏电流与辐照前基本相同。本文所用的SOI晶圆材料总剂量加固水平可以达到500 krad(Si)。

2.4 芯片版图规划

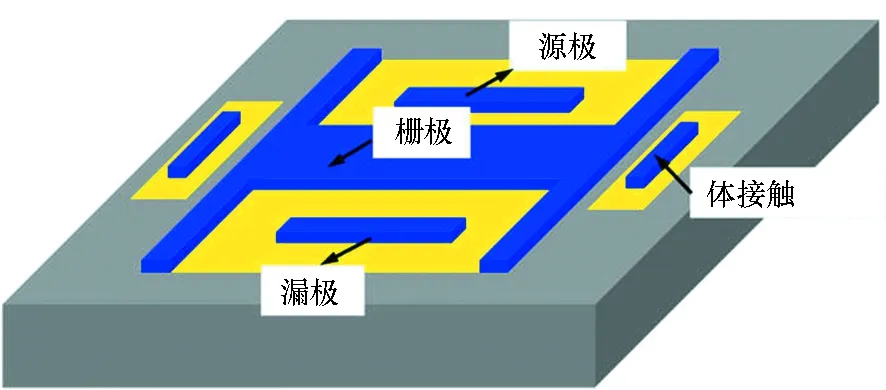

寄生的源漏电流是总剂量效应的最主要表现,H型栅能够将体有效地引出,阻断源漏之间的漏电通道,避免寄生晶体管的开启,同时阻断器件边缘漏电通路,减小漏电流,以增强抗总剂量辐射能力[15]。为此电路单元在版图上使用带两个P+体引出端的 H 型栅进行抗总剂量辐射加固,其结构如图5所示。

图5 H型栅结构示意Fig.5 Schematic of H gate

3 芯片测试结果

3.1 芯片功能测试结果

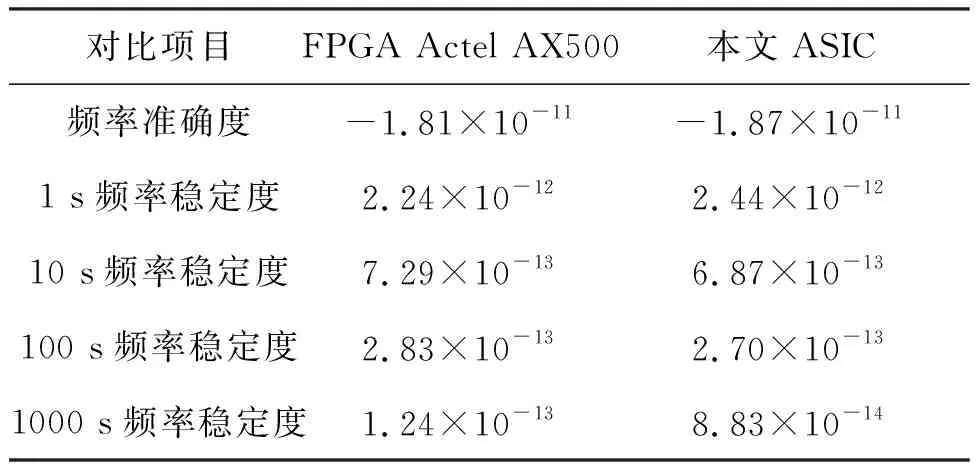

芯片在总剂量加固SOI晶圆上进行流片,一次流片成功,流片后采用CQFP164封装,并进行了功能测试。功能测试主要是让芯片在闭环系统进行工作,作为核心处理部分调节系统误差。测试结果表明:芯片的功能正确,且调节的精度可以达到5×10-12,与国外进口的Actel反熔丝型抗辐射现场可编程门阵列(Field Programmable Gate Array, FPGA)AX500相近;在长时间频率稳定度方面,芯片优于国外FPGA,对比结果如表2所示。

表2 FPGA Actel AX500与芯片测试结果及比较

3.2 芯片总剂量测试结果

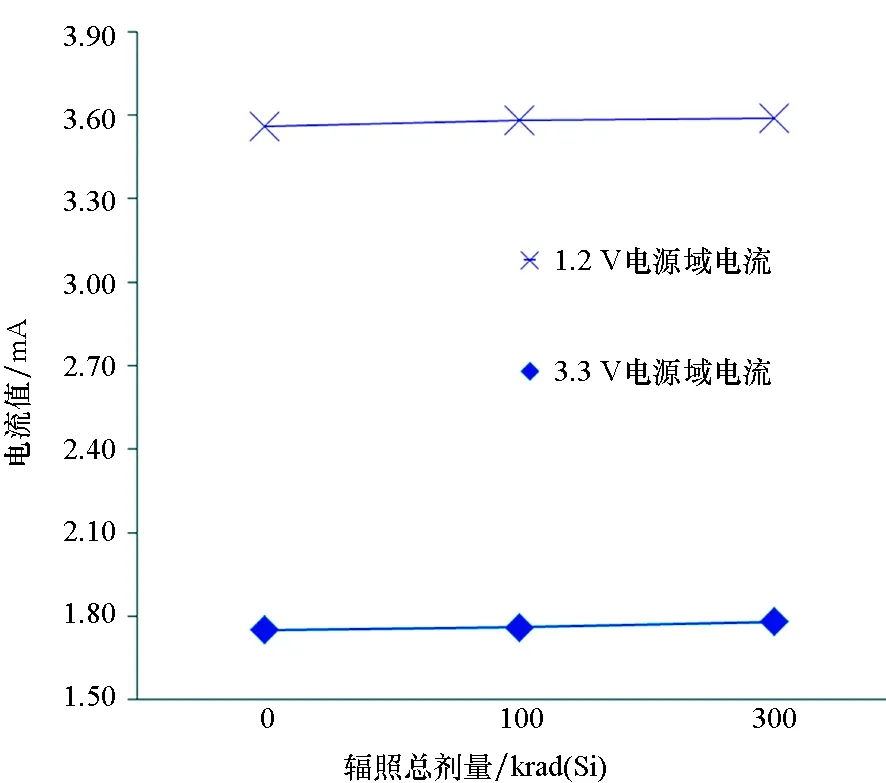

芯片总剂量辐照实验在中国科学院新疆理化技术研究所进行,辐照源为Co60γ 射线,选择的辐照剂量率为70 rad(Si)/s,总剂量范围在100~450 krad(Si)。

在辐照过程中,芯片所加的偏置与芯片实际工作状态相同。芯片偏置条件为:电源为3.63 V(3.3 V+10%)和1.32 V(1.2 V+10%),分别给IO和内核(CORE)供电;其余输入脚都输入25 Hz的方波。从测试的控制芯片DDS控制以及DAC控制端口输出等方面没有出现功能异常,这说明控制芯片的核心算法、峰值检测、状态检测、时序控制、闭环检测等都正常工作。但是在辐照测试过程中观察到芯片工作电流略有增大,这说明芯片的电流-电压特性已经受到影响,符合文献[12]中的结论。图6为测试芯片在辐照前和辐照总剂量分别为100 krad(Si)、300 krad(Si)共3个测量点的工作电流。从图中的电流变化曲线可以看出,芯片电流的变化在0.1 mA以内,变化量远远小于规定的10%。

图6 芯片电流随辐照总剂量的变化曲线Fig.6 Chip current versus total ionizing dose

4 结论

采用上海微系统与信息技术研究所开发的130 nm PD-SOI CMOS抗辐射标准单元库进行了基于PID算法的控制芯片设计。通过使用抗总剂量辐射水平达500 krad(Si)的加固SOI晶圆以及体接触H型栅的版图设计来对芯片进行总剂量加固。芯片流片后采用CQFP164陶瓷管壳封装,测试结果显示芯片功能正确,且调节精度达到5×10-12,与国外进口FPGA相当,在频率稳定度方面芯片优于进口FPGA。辐照总剂量实验表明芯片在总剂量辐射达到300 krad(Si)时依然能够正常且稳定地工作,完全满足空间应用需求,可为卫星抗辐射控制芯片国产化提供技术积累和基础。