图像中值滤波算法上的软硬件优化

2020-07-09李龙华王肃国

李龙华 王肃国

摘 要:针对传统的中值滤波软件处理速度慢,无法达到图像处理高实时性要求的特点。文献中提出了基于FPGA的快速中值滤波算法,充分结合硬件的高实时性和软件的调度复杂性,同时采用流水线结构,使图像中值滤波处理的实时性得到提高。文章对已有的算法进行改进,简化了硬件结构,而又不失图像处理的实时性。该算法通过仿真验证,得出算法在图像中值滤波处理中的可行性,能够满足实时性要求。

关键词:中值滤波;实时性;FPGA;硬件结构;仿真验证;可行性

中图分类号:TP391.41 文献标识码:A 文章编号:2096-4706(2020)21-0097-04

Software and Hardware Optimization of Image Median Filtering Algorithm

LI Longhua,WANG Suguo

(Shandong Vocational Institute of Fashion Technology,Taian 271000,China)

Abstract:Aiming at slow speed of software processing for the traditional median filtering,unable to meet the characteristics of the high real-time requirements of image processing. The literature proposed the FPGA-based fast median filtering algorithm,taking full advantage of high real-time hardware and software scheduling complexity,along with adopting a pipelined structure,so that improve the processing of real-time of image median filtering. The article improves existing algorithm,simplifies the hardware structure,and does not lose the real-time image processing. The algorithm is verified by simulation,and the feasibility of the algorithm in the image median filter processing is obtained,and it can meet the real-time requirements.

Keywords:median filtering;real-time;FPGA;hardware structure;simulation verification;feasibility

0 引 言

物聯网是当今世界的一大研究热点,摒弃了原来只研究软件算法,或者只研究硬件结构的学科研究单一性的问题,真正地将软硬件结合实现快速中值滤波算法,以交叉学科的形式落实到计算机教学中。随着越来越多高职院校相继开设物联网技术(包含校企合作)等专业,以山东服装职业学院为例,开设物联网技术(中兴校企合作专业),使得高职学生对于物联网有了一个全方位的了解学习机会。采用软硬件结合的方式,在软件算法实现过程中,引进硬件方案,从而加速软件算法实现的过程,提高算法效率。学生在学习物联网专业知识之初,对物联网技术有个简单的认识,及对软硬件结合解决软件算法效率较低问题有个初步的了解,故本文以中值滤波算法在软硬件结合技术方面做出研究,引起学生对物联网的学习兴趣。

在高职物联网应用技术专业的技术类课程教学中采用中值滤波算法处理图像为切入点,利用软硬件结合优化算法,可极大提高学生学习程序的兴趣,感受算法的魅力,增进其对专业的了解。因此在物联网应用技术教学中,应用软硬件协同优化图像中值滤波算法具有理论意义和实践意义。文章在传统的中值滤波算法的基础上,引入软硬件协同,采用基于FPGA技术设计,并减少算法在硬件结构设计上的投入。同时,又能满足在图像处理中实时性的要求。相比其他的滤波技术,既能有效的消除脉冲噪声和椒盐噪声,又可以较好的保持图像的边缘信息[1]。

1 中值滤波原理

1.1 中值滤波的基本原理

采用合理算法去除图像噪声是一种有效的方法[2]。中值滤波(Median Filtering)是一种非线性的图像处理技术,能有效地抑制图像中的噪声。相关原理是对图像中的所有像素值的整个区域进行数值排序,找出该值域的中位值,当作该像素邻域的输出值,参与图像的呈现。在这种算法中,最大像素值及最小像素值在算法实施过程中不再作为像素输出。因而,该算法能够在图像的平滑操作中,有效地过滤尖锐噪声,例如常见的椒盐噪声等。算法的数学表达如下:

g(x,y)=median{f(x-i,y-j)};(i,j)∈S (1)

式(1)中g(x,y)和f(x,y)分别为处理后及原图像中的像素值,S为窗口,可以是线性、正方形、十字形等窗口[3]。

1.2 传统的中值滤波算法分析

传统的算法排序是采用冒泡法对像素值比较排序,对于一个像素值为n的窗口,采用冒泡法,要进行以n2的数量级的排序。与此同时,采用冒泡法[4],需要产生第(n+1)/2个大值时方能产生一个中值,所以都要经过若干个时钟周期才能产生一个中值。以3×3窗口为例,采用中值滤波纯软件算法,需要冒泡排序36次。采用5×5,7×7等窗口时,过程将会十分繁琐,根本无法满足图像处理实时性的要求。

针对传统算法在实时性要求较高的工程中无法满足需求的不足,文献中提出基于FPGA的快速中值滤波算法,该算法S选为矩阵模版,以三值排序模块为基础[5]。先在每行内进行排序,再进行列排序,最后在主对角线上的像素进行取中值。以3×3矩阵的模板窗口为例进行分析。行内排序需要9次。同理,列排序也需要9次,最后的取中值运算需要3次。再者,比较次数的多少决定了所需三值排序模块的多少。通过上述分析可知,得到一个3×3的中值,需要进行21次比较,7个三值排序模块。

2 改进中值滤波算法

2.1 算法分析

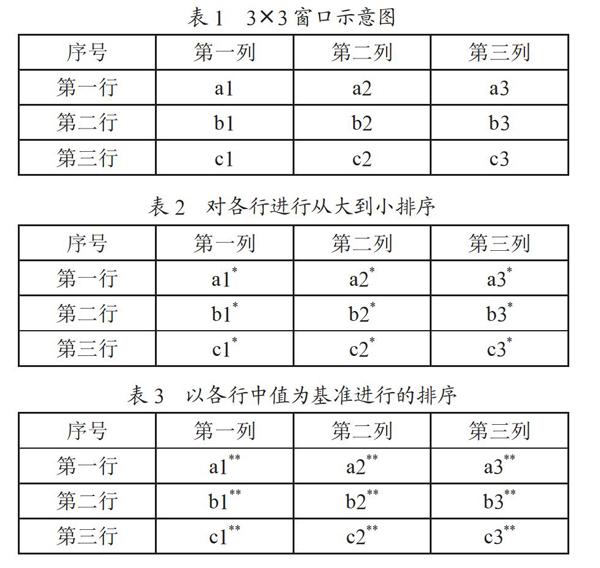

以文献[5]中FPGA的中值滤波算法为基础,本文对此进行改进。再次降低算法的比较次数,所需三值排序模块的数量进一步减少,从而使硬件模块化设计进一步简化。具体过程如表1、表2、表3所示。

其中的中值就是a3**,b2**,c1**三者之间的中间值,具体分析如下。

对三个表的操作如下:第一步,对表1中的每行数值并行处理,即对三个数值从小至大排序,得表2。第二步,根据排序操作,可得出,其中a2*,b2*,c2*为所在行中值。然后,以这三个中值按从小到大顺序,对表2数据进行行间排序,产生表3。

对表3进行分析得出中值,首先排除一定不是中值的点。a1**,a2**显然不是中间值,如果这两个值为中值,其中比其大的值不超过四个。以a2**为例,因为对表1进行的排序是从小到大的,所以a3**比它大。又因为对表2的排序是行间按从小到大的排序,所以b2**,c2**也比它大,自然b3**,c3**也要比a2**大,所以a2**不可能是最大值。同理a1**也不可能是。c2**,c3**显然也不是中值,c2**为例,根据数据处理的方法,得出小于c2**的数有五个,分别是a3**、b1**、b2**、b3**、c1**。同理可得出c3**也不是所需中值。

剩下的五个值a3**、b1**、b2**、b3**、c1**中就包含了我们所需要的中值,因为b1**、b2**、b3**已有顺序,进而无需重复参与排序。按照插入排序的方式,只要a3**、b2**、c1**进行排序并取出其中的中间值,即为我们所要求的。

算法复杂度分析,第一步并行方式对行内数值排序,比较9次,第二步各行中值比较,比较3次,第三步对三个数值进行比较排序,比较3次。由此得出,本文改进算法需要15次比较,比文献[5]中的算法减少了6次。比较次数的降低,从而使三值排序模块的使用个数减少。改进的中值滤波算法只需5个三值排序模块就能够实现。在硬件结构的设计上,可以达到简化的目的。本文算法与纯软件、文献[5]算法的具体比较如表4所示。

2.2 改进中值滤波算法的设计

此算法的设计分为两大部分:一是模块产生部分,二是对产生的模块进行取中值部分。模块产生部分即为N×N窗口生成模块,将带有噪声的图像的像素以窗口形式进行呈现,参与中值滤波算法中去。文章采用3×3窗口,因此需要3×3窗口。对产生的模块进行取中值部分,对已产生的3×3窗口像素进行取中值操作,用于完成中值滤波算法。

2.2.1 3×3窗口生成模块

原理框图如图1所示。

图1中包括7个移位寄存器R1~R7,两个先进先出的存储器FIFO1与FIFO2,FIFO用来存储一行的数据[2],使9个数据输出排列呈如表1所示的3×3模板所对应的图像数据[6]。像素值输入,就相当于一个3×3的窗口扫过整个图像,得到图像中的全部像素。

2.2.2 中值滤波设计

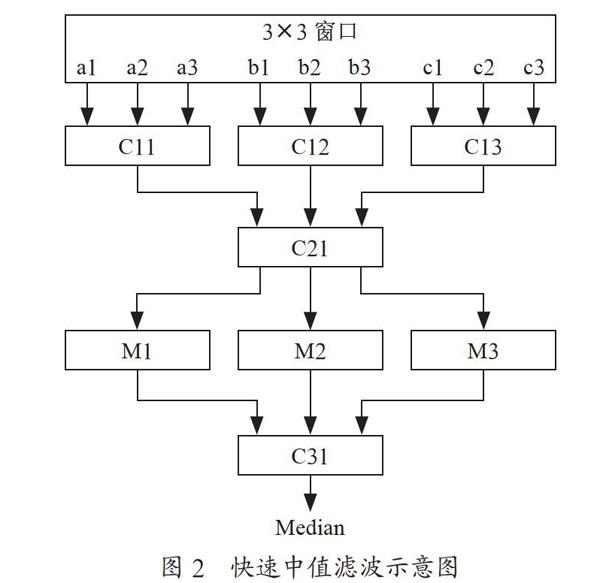

改进中值滤波模块示意图如图2所示。

C为三个数值排序模块[7],M1,M2,M3是已经过上一周期各行排序后的中间值为基准,进行排序产生的新模块。分别以模块M1的最大值,模块M2中间值,模块M3的最小值做为C31的输入值进行排序,输出median。

快速中值滤波算法的实现就是以三点排序的模块为单位,由图2可以看出,此算法利用5个排序模块,比文献[5]中算法实现所需模块数目减少了2个,达到硬件结构设计简化的目的。再加上时序的合理安排,采用流水线实现模式,最终达到处理所需要的效果。

由上可知,三值排序模块是快速中值滤波算法的一个基础,实现此三值排序模块的流程图如图3所示。

其中R1存放a1与a2中较大的值,R2存放两者中较小的值,然后再將R1、R2与R3进行比较,从而对三者进行最终排序[7]。将9个数以行为单位分成三组,进行并行处理,为9个数值的排序取中值缩短了时间,提高算法的处理效率。

3 改进中值滤波算法的仿真

3.1 Quartus II与Modelsim的仿真

通过使用Quartus II 11.0和ModelSim SE 6.5a进行仿真验证,可得到如图4所示的仿真图形。

由图可以看到,时钟clk上升沿有效,复位信号rst_n有效。这里采用了流水线处理方法,流水线处理[8]是提高组合逻辑设计处理效率和吞吐量最常用的方法。如流程图2所示,采用流水线处理方法,虽然第一次输出有较长的的延时,当经过若干个周期的延迟后,可以每个周期产生一个结果。本算法中采用三级流水线结构,经过三个周期后,产生了第一个结果,之后的每个时钟周期都可以产生输出值,这样大大地增加了系统的吞吐量。再者,这种流水线的设计方式解决了系统工作频率的瓶颈问题,提高了系统的带宽以及资源利用率。

3.2 ModelSim与Matlab进行联合仿真

为了节省仿真时间,笔者采用Link for ModelSim组件进行软硬件协助仿真[9],这种仿真方式缩小了算法同硬件实现之间的鸿沟,缩短了仿真验证的时间,且简单易行。通过对加入椒盐噪声的cameraman图片的处理,并与文献[5]中的处理效果进行比较,可以发现处理的效果大致相同。但是,在硬件部分上,该算法的硬件结构得到了进一步简化,节约了硬件资源,也为此系统的设计提供了方便。

4 结 论

物联网技术是一门软硬件协同工作的技术,属于交叉学科。在高职院校引入物联网技术专业,相对高职学生而言,从技术和理论上是一种比较新的事物,从接觸专业开始就应该有一个全面的了解。高职院校的物联网教学,需要采用以点带面的教学方式,找到适当的课程切入点,使学生能够更形象的了解学科组成结构等方面的知识。因此文章为更好实现对物联网应用技术的教学工作,提高学生学习物联网技术的积极性,通过对现有的中值滤波算法进行软硬件协同优化,与单纯的算法实现相比,实时性有很大的提高,其处理稳定性与可靠性有所改善。同时又增加与文献[5]的比较,在不影响快速实现中值滤波算法效率下,又对硬件结构做出优化,节省了硬件投入。不仅可以更好地满足物联网中图像中值滤波算法简单、高效的特点,同时,也对学生了解物联网技术设计的灵活性,了解物联网技术具有广阔的应用前景有很大的帮助。

参考文献:

[1] 韩团军.快速中值滤波算法研究及其FPGA硬件实现 [J].电子器件,2017,40(3):697-701.

[2] 沈学利,王肃国.基于FPGA的改进型中值滤波算法研究 [J].微电子学与计算机,2014,31(1):21-24.

[3] 马丽圆,常锦才.一种迭代的自适应中值滤波算法 [J].软件,2020,41(9):69-71.

[4] 张海生.FPGA在图像处理系统设计与仿真中的应用研究 [J].电子世界,2020(21):155-156.

[5] 李新春,赵璐.基于中值滤波算法滤波器的FPGA实现 [J].计算机系统应用,2011,20(9):82-85+72.

[6] 赵亮,刘鹏,王晓曼,等.基于FPGA快速中值滤波算法的硬件实现 [J].长春理工大学学报(自然科学版),2018,41(5):97-100+115.

[7] 仙云森.基于FPGA的图像处理算法研究及硬件设计 [D].大连:大连理工大学,2008.

[8] 潘松,黄继业,潘明.EDA技术实用教程——Verilog HDL版:第4版 [M].北京:科学出版社,2010.

[9] 夏宇闻.Verilog数字系统设计教程:第2版 [M].北京:北京航空航天大学出版社,2008.

作者简介:李龙华(1988—),女,汉族,山东泰安人,助教,硕士,研究方向:计算机网络技术;王肃国(1987—),男,汉族,山东济宁人,助教,硕士,研究方向:计算机应用技术。