一种高精度定时器设计方法

2020-06-12柯小路王继生李洋

柯小路 王继生 李洋

(南京电子技术研究所 江苏省南京市 210039)

1 引言

雷达是由诸多具有不同功能的相对独立模块组成的一个复杂系统,不同模块之间必须按照一定的时序协调工作。定时控制器是雷达系统的重要组成部分,为雷达全机提供所需的各种时序控制信号。当前雷达的工作方式日趋多样,定时时序关系愈发复杂,同时,对定时器的小型化、通用性、多功能性的要求越来越迫切,越来越多的雷达系统采用独立的定时控制器来实现对整个雷达各分系统的同步时序控制。随着FPGA资源及性能的提升,其被广泛应用于雷达系统各模块,基于FPGA的多功能定时控制器能够较好地满足以上需求[1-2]。

当前,定时器的基本原理已经比较成熟,近年来的研究主要集中在实际实现方面[3-7]。一方面相控阵雷达功能多样化、复杂化,对定时灵活性要求逐步提高,雷达定时器已从单一或有限固定时序向参数化可调整定时转变;另一方面雷达性能的提升对定时的精度需求越来越高。为此,本文基于FPGA平台和嵌入式技术,提出一种通用的参数化定时架构,在此基础上提出一种高精度定时器设计方法,满足定时灵活性与高精度需求。

2 定时器原理

以定时计数的参考基准划分,定时信号主要可分为两类:帧(脉组)同步定时、脉冲同步定时。帧同步定时每帧产生一个,以帧起始信号为基准,包括帧起始、帧结束以及部分触发信号;脉冲同步定时则在每个重复周期内产生,以重复周期起始信号为基准,包括发射、接收相关定时,一般情况下同一帧的不同重复周期内相对时序关系不变。

基于FPGA的定时信号产生其原理如图1所示。利用基准时钟,同步周期计数器自帧起始时刻开始计数,其它所有定时信号以此为基准,计算与其相对位置计数值,当同步计数器计数到某个定时计数值时,产生一个脉冲定时信号。帧定时参数每帧内更新一次,而一帧内可能含多个重复脉冲,脉冲定时参数需在每个脉冲结束前进行更新。所有定时信号基于同一个计数器产生,确保了各信号之间的抖动最小。

3 定时器设计

3.1 硬件架构

定时器以Xinlinx公司的FPGA作为核心处理器件,外围扩展DDR、FLASH及各种接口芯片,其硬件框图如2所示。

3.2 软件架构

3.2.1 参数化定时器

由定时产生原理可知,定时信号依赖于一组定时位置参数,即计数器的计数值,当这组值确定,对应的时序关系随即确定。因此,若能够适时改变这些参数,就可以产生不同的定时时序。参数化定时的基本思想就是使得这些定时计数值可参数化配置,从而产生一系列复杂定时时序。

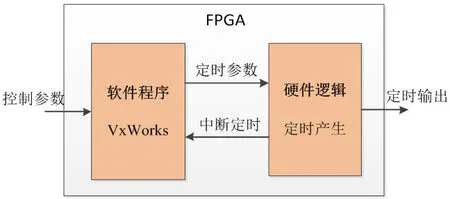

得益于可编程器件和SOPC技术的快速发展,我们得以在单片FPGA上运行操作系统,使得定时参数实时受控改变成为可能。参数化定时将定时产生划分为软件程序和硬件逻辑两部分,其中软件部分为硬件逻辑提供定时相关参数,而硬件逻辑通过图1所示原理,基于计数器产生对应的定时信号。参数化定时产生的原理框图如图3所示。

图1:定时产生原理框图

参数化定时器以Xilinx FPGA作为核心器件实现嵌入式SOPC控制系统,基于内嵌的高性能Power PC440硬核,使用VxWorks实时操作系统,软件程序主要完成以下功能:

(1)控制指令的接收与解析;

(2)定时器计数值的计算与实时更新;

(3)通过处理器局部总线(PLB)传输定时参数至定时产生逻辑。

定时产生逻辑接收PLB总线传输的定时参数,根据计数值产生定时信号,为VxWorks系统提供中断定时,以实时更新定时参数。

3.2.2 高精度定时器

为保证各分系统的时钟同步,定时器利用外部信号源统一提供的同源基准时钟产生同步定时信号。通常外部基准时钟频率较高(100MHz或更高),在FPGA内先经过时钟分频产生较低频率的时钟后再用于定时产生。但随着雷达系统性能的提升,对定时的精度要求越来越高,从1MHz到10MHz、20MHz,甚至直接以外部基准时钟为刻度。

提高定时精度最直接的方法是使用对应的时钟进行计数,如需100MHz精度定时则用100MHz时钟计数。但这种方法将面临两个问题:

(1)计数时钟频率提高,相同的计数周期需要更宽的寄存器位数,大大增加逻辑资源消耗;

(2)时钟提高将增加时序收敛难度,尤其是在资源占用率较高的情况下,时序收敛更为困难。

此外,该方式兼容性较差,每次更改定时精度时,软硬件程序均需更改。

针对以上问题,考虑到实际应用中,通常并非所有定时信号都需高精度,而仅是与发射、接收相关的几个定时需要高精度,故提出图4所示基于延时的高精度定时产生方法。

从图4中可以看出,基于延时的高精度定时产生基本原理是将定时分成整数和小数两部分:整数部分采用分频时钟产生,小数部分采用基准时钟产生。例如,基准时钟为100MHz,所需定时精度为20MHz,要产生一个位置为11.55us的定时,则整数部分可通过10MHz分频时钟计数,计数值为115,而0.05us则通过延迟5个基准时钟刻度来实现。20MHz定时精度对应的延迟值只有0和5个时钟两种情况,而100MHz定时精度对应的延迟值则有0~9共10种情况。基于参数化定时架构,定时延迟参数可通过软件配置给定时产生逻辑,从而实现灵活改变,满足定时产生需求。

将定时分为整数和小数两部分产生的主要优点包括:

(1)使得程序主要逻辑运行在较低时钟,少量逻辑运行在较高时钟,利于时序收敛;

(2)只需针对需要提高精度的定时信号进行处理,不用整体增加寄存器位宽,节省逻辑资源;

(3)定时精度调整方便,只需通过软件改变延迟参数值即可,无需再修改硬件逻辑。

表1:两种定时产生方式主要资源对比

图3:参数化定时原理框图

图4:基于延时的高精度定时原理框图

图5:32路定时时序测量图

4 测试验证

某场景基准时钟频率为120MHz,需产生32路定时信号,其中6路定时信号精度为120MHz,其它定时信号精度均为10MHz,定时最大周期1s。

分别使用120MHz作为计数时钟和基于延迟的高精度定时方法进行定时程序设计,为达到1s周期需求,10MHz精度需24位计数器,而120MHz精度需27位计数器,编译后主要资源的占用情况对比如表1所示。

从表1中可以看到,基于延迟的高精度定时产生方式可有效减少逻辑资源消耗。

基于定时在线测试设备进一步对两种方法的定时产生效果进行比较,结果表明采用相同的控制参数,两种方法所产生的定时均可达到预期精度,某工作模式下定时时序如图5所示。

5 结论

本文介绍了一种以FPGA为硬件平台的高精度定时器设计方法。该定时器基于参数化设计,实现定时时序的灵活可控;与直接使用高频时钟计数不同,它将定时信号分为整数和小数两部分产生从而实现一种通用架构,在资源占用、时序收敛和通用性等方面均取得良好效果,可满足一类雷达的定时器设计需求。