HFETRC棒控系统故障处理与分析

2020-06-03江易蔚何佳谦张先萌

江易蔚,王 雷,蒋 波,何佳谦,张先萌

(中国核动力研究设计院 第一研究所,成都 610213)

目前,在建某试验堆计划在高通量工程试验堆临界装置(HFETRC)上开展堆芯临界物理试验。针对临界物理试验的内容及要求,必须对HFETRC 棒控系统进行控制棒组件、堆芯孔道布置、安全棒数量以及掉棒时间测量方式等进行改造。

本文针对棒控系统改造后频繁调试中出现的故障进行排查、处理,对故障原因进行分析并提出预防措施。

1 HFETRC棒控系统组成及原理

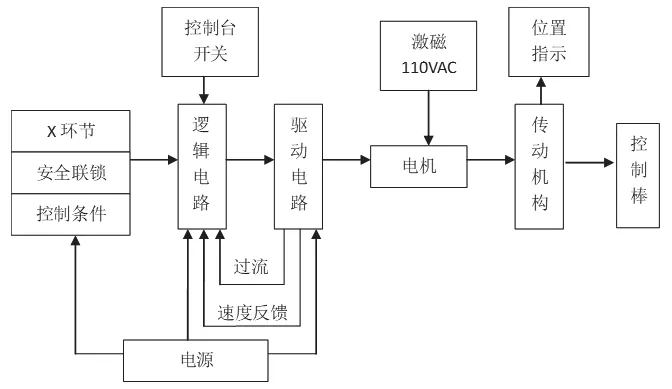

HFETRC 棒控系统用于对安全棒、手动棒的升降控制。系统由低压电源、X 环节、安全联锁、控制条件、棒控逻辑、电机驱动等插件组成。其组成框如图1 所示。

图1 HFETRC棒控系统组成框图Fig.1 Composition diagram of HFETRC rod control system

HFETRC 棒控系统是带有反馈环节的闭环控制系统,输入信号经过放大、移相和选通电路,给出上升或下降信号来控制可控硅的导通角,以此来控制电机的方向和转速。测速反馈环节将速度负反馈信号和输入信号进行比较,根据误差信号的大小来控制电机的速度,使电机的速度趋于定值。

2 棒控系统故障现象与处理

本次棒控系统经过改造后,控制棒重量长度、堆芯布置以及安全棒数量与以往不同,频繁通断电调试后系统出现的故障或问题现象分为以下几类:

2.1 逻辑插件顶部灯/底部灯故障

故障分析:由棒控逻辑电路图可知,逻辑插件到顶/底部灯分别由顶部行程开关和底部行程开关信号,通过光耦转换为电平信号,然后经过逻辑芯片进行逻辑运算后再通过达林顿管驱动。由于故障不影响提升下降信号,所以故障点应该为逻辑芯片和达林顿管。

检查方法:排查故障原因只需要测量芯片输入输出角的电压是否符合逻辑关系,就能发现故障芯片进行维修更换。

2.2 无法正常手动提升(下降 )/自动提升

故障分析:由图1 可知,棒控系统是由控制台开关控制,逻辑电路进行逻辑运算与放大,调速电路进行移相选通(移相电路也在逻辑插件中),最后得到的上升或下降信号控制驱动电路的可控硅导通角,由此控制电机的转动方向和转速。因此,无法提升下降或者自动提升可能的故障点是棒控逻辑电路、棒控调速电路、驱动电路3 个电路中。

检查方法:

1)在测试机柜上,发送提升下降信号,使用万用表测量逻辑电路提升下降测点,判断逻辑运算电路输出是否正常,就能发现故障芯片进行维修更换。

2)若提升下降测点输出正常,需进一步测试棒控逻辑的调速电路,调速电路由速度控制电压电路,检查过程中,使用示波器测量调速电路的输出波形,如未测得输出脉冲,就可判定出器件损坏,更换既可排除故障。

表1 HFETRC棒控系统故障列表Table 1 Fault list of HFETRC rod control system

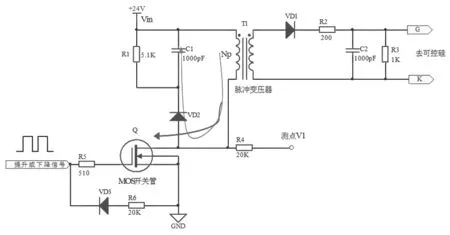

3)如果在驱动电路测点未测得脉冲信号,由电路分析可判断是脉冲变压器或MOS 管损坏。测量脉冲变压器或MOS 管损坏的离线电阻既可判断元器件是否故障。

2.3 掉棒时间自动计数

故障分析:由棒控逻辑电路图可知,控制棒顶部底部行程开关都是常闭开关,当触发停堆保护信号时控制棒离顶逻辑插件送出高电平信号,控制棒到底时高电平信号被拉低。掉棒时间测量自动计数并且计数不停止,说明在棒控逻辑插件插入时,掉棒时间这个输出点产生了从低电平到高电平的上升沿。

检查方法:排查故障应从掉棒时间这一条逻辑通路上测试逻辑芯片工作是否正常。

3 故障原因分析及风险预防措施

电子元器件可靠性寿命周期的典型失效分布符合浴盆曲线规律可划分为三期:早期失效期、随机(偶然)失效期、损耗失效期。经分析,符合HFETRC 棒控系统电子元器件失效的原因有以下几点:

3.1 损耗失效

1)老化失效

由于HFETRC 棒控系统已停用多年,所在地区湿度温度也较高。高温高湿度的同时作用,会加速金属件的腐蚀和绝缘材料的老化。对半导体器件,如果水汽渗透进管芯,还会引起电参数的变化[3]。棒控系统中损坏的二极管、逻辑芯片与功率器件都有可能是该原因造成。

2)使用损耗

图2 电机驱动开关缓冲吸收电路Fig.2 Buffer absorption circuit of motor driven switch

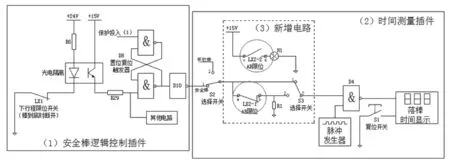

图3 HFETRC控制棒落棒时间测量原理图Fig.3 Principle diagram of hfetrc control rod drop time measurement

因变压器只能是在原边开关管导通期间储存能量,当它截止时才向负载释放能量,故高频变压器在开关管在开关工作过程中,既起变压隔离作用,又是电感储能元件。在多次的开关过程中,变压器和MOS 管的性能逐渐降低。当开关管导通时,能量存储在变压器初级绕组的电感量Lp和漏感量Llk 中,当开关管关闭时,Lp 中的能量转移到副边输出了[2]。但由于前端提升下降频率为100KHz,漏感随着频率增大而增大,漏感Llk 中的大部分能量虽然在RCD缓冲回路的作用下转移到RCD 箝位电路中,可仍对变压器以及MOS 管有着一定的电应力冲击损耗减少其使用寿命[2]如图2 所示。HFETRC 棒控系统经过改造后需要对系统状态进行全面的检查,需要频繁的提升下降试验,频繁的试验加速了脉冲变压器T1/T2 以及MOS 开关管的使用损耗,使得其损坏概率增大。

3.2 随机失效

1)上电顺序错误引起的失效

由于棒控系统的逻辑电路以及调速等电路中的逻辑门电路,在上电的瞬间状态不确定输出为X(0 或1),可能会导致触发产生提升或下降信号,使得驱动电路中MOS 开关管导通,直流输入电压24VDC 加在了变压器原边与MOS开关管两端如图2 所示。正常情况下的提升或下降信号的触发脉冲,其频率为100KHz,脉宽5uS。上电瞬间触发脉冲,这个脉冲持续时间较长通常为毫秒级,脉宽远远大于正常触发脉冲宽度。当MOS 管较长时间内导通,MOS 管、变压器工作,通过变压器的电流较大,线圈发热量持续上升降低了变压器绝缘等性能,甚至将变压器击穿烧毁、短路,过流亦可能导致MOS 管的损坏。

该现象的预防方法为:棒控机柜上电时,上电顺序应该为首先将棒控逻辑插件通电,使得逻辑门器件输出稳定。然后将电机驱动插件上电,避免干扰脉冲输入MOS 管。

2)ESD 现象

逻辑芯片ESD 现象是指芯片在制造、使用和运输过程中,由于外部环境和内部结构的一些因素可能会积累大量静电荷,当芯片与大地或其他一些低电位物体接触时,这些积累的电荷会通过芯片的I/O 管脚瞬间释放;或是带有大量静电荷的物体接触已经接地的芯片时,通过芯片放电,发生电荷转移,形成巨大的瞬态电流[1]。

在HFETRC 棒控系统运行维护中应做好静电防护。静电放电防护的基本原则主要有两种:一是抑制静电电荷的产生和积累;二是安全、迅速、有效的消除已产生的静电电荷。目前在工程实践中采取的静电防护主要方法为:接地、中和、增湿、屏蔽等。

3)误操作导致的过度电应力

由于HFETRC 的落棒时间测量装置经过改造,新加入了一套时间测量行程开关与到底位置指示灯,后加入的行程开关在测量电路中的位置为如图5 的LX2-1,目的是在掉棒缓冲段之前结束棒控逻辑插件发送来的掉棒时间高电平信号,测量出在缓冲段前的快速掉棒时间。改造后的时间测量后有4 个后加的触点,作用分别为图3 的abcd 所示。

由图3 可以看到,开关LX2-2 的c 端是带有15V 的电压。由于HFETRC 系统改造后只有两张测量插件而有4 根安全棒,测量不同的安全棒会有触点接线插拔工作。在对后面触点进行插拔操作时,如果拔插顺序不当,先插入底部灯H1 上面触点C 后,如果此时控制棒在底部LX2-2 闭合,会将+15V 电压引入开关触点的另一头。如果此时接入触点D,可能将15V 电压引入机柜外壳或插件电路,导致15V 电源短路,或导致插件故障或烧毁。插件插入落棒时间自动计时的故障可能是该原因导致。

该现象的预防方法为:时间测量插件安装和更换测点时,下限灯H1 两个触点安装顺序应为先安装触点D 再安装触点C,防止低压电源短路。

同时,对新加入的限位开关电路供电处增加保护电路,串联一个电流保险丝,防止15V 电源短路,引入过大的电流进入逻辑芯片电路,对电路造成冲击。同时在逻辑插件芯片输出端并联一个压敏电阻,利用压敏电阻非线性的伏安特性,防止ESD 现象引入过高的电压进电路,把窜入电路的瞬时过压限制在系统电路能承受的范围之内,保护耐压能力较差的逻辑芯片等电路[4,5]。

4 结束语

本文针对HFETRC 的维修与改造情况介绍了HFETRC棒控系统调试过程中出现的故障现象,对此次故障现象进行了故障分析,找出故障点,提出了故障处理措施,并对棒控系统插件的故障的原因进行了分析,提出预防故障方法。

通过HFETRC 棒控系统调试过程中故障分析与处理,保障了某试验堆堆芯临界物理试验在HFETRC 上顺利完成,也为其它试验堆仪控系统电子元器件失效引起的故障分析处理提供参考。