基于FPGA+AD9365 的信号干扰源设计与实现

2020-05-27吴伙土

吴伙土

(厦门市合佳兴电子有限公司,福建 厦门 361015)

0 引言

随着生活水平的提高,个人隐私越来越受重视。如果个人身上物品或车辆被不法分子放置跟踪器,将处于极度危险中。因此,本设计方案针对小型化、便携式、低功耗以及简单操作使用的特殊场景,采用 基 于Xilinx 的FPGA 7Z035-2FFG676I 和ADI 的Transceiver AD9365 捷变收发器为核心器件平台,实现纯数字化的软件无线电干扰源。民用的GPS 信号频率是(1 575.42±1.023)MHz,信号强度低,信号主瓣能量都集中在2.046 MHz(1 dB)带宽内[1-2]。所以,本设计方案配置AD9365 直接发射以1 575 MHz 为中心频点、带宽5 MHz 的高斯白噪声,外面不需要增加额外射频功率放大器器件。AD9365 的发射输出端直接把差分信号通过宽带巴伦转成单端射频发射信号,所产生的射频信号频点与GPS 一致。信号带宽完全大于GPS的信号带宽,这样能完全覆盖GPS 的能量,从而能够对GPS 信号进行有效干扰,防止不法分子跟踪。该方案电路具有集成度高、体积小、掩蔽性好以及功耗低等特点,并设计成电池直接供电,方便直接随身携带使用。

1 AD9365 介绍

AD9365 是一款高性能高集成的射频(RF)Agile Transceiver 捷变收发器[3],集成射频前端与灵活的混合信号基带部分集为一体,内部集成12 bit 的DAC 和ADC。射频接口1个发射端口(1T)和1个接收端口(1R),收发频率范围200 MHz~2.3 GHz,射频收发带宽200 kHz~10 MHz,本振步进2.5 Hz,支持TDD 和FDD 模式。接收最大增益75 dB 左右,发射最大功率8 dBm 左右。基带数据接口为LVDS 或COMS 模式。外界主控芯片通过SPI 接口直接对AD9365 内部寄存器地址和寄存器值进行读写配置。

2 系统总体方案设计

本设计信号干扰源方案采用ADI 的捷变收发器AD9365 和Xilinx 的7Z035,系统总体框图如图1 所示。

图1 信号干扰源系统框图

图1 中,FPGA 为整个系统的主控芯片。FPGA的PS 通过SPI 对AD9365 进行相应的参数配置,使AD9365 工作在所需要的频点、带宽和发射功率。FPGA 的PL 采用折线逼近方法[4],快速产生高斯白噪声序列,然后把数字基带信号通过CMOS 数据接口模式发送给AD9365。DDR3 为系统运行所需的DRAM。Flash 用来存储系统bin 文件[5]。用户接口包含用户按钮和LED 指示灯,用来控制系统工作和系统工作状态指示。电池和充电管理模块中,电池通过电源管理芯片给整个系统提供各路所需不同电压的供电,且用户可以对电池充电。

3 AD9365 的配置流程

通 过ADI 的AD9361 Evaluation Software v2.1.5(64-bit)软件,在这个GUI 上设置本方案所需要 的AD9365 工 作 参 数:Device 选 择AD9365,RX Disabled,TX1 Enabled,REF_CLK_IN 40 MHz,Standard 选择Custom,Tx Samping Rate 30.72 MSPS,Tx RF Bandwidth 5 MHz,TX Frequency 1 575 MHz,数据接口设置成CMOS 模式(SwapPort,Dual Port),FDD模 式(Dual Port,Full Port),Data Rate(Double Data Rate),DATA_CLK Rate 填30.72 MHz。

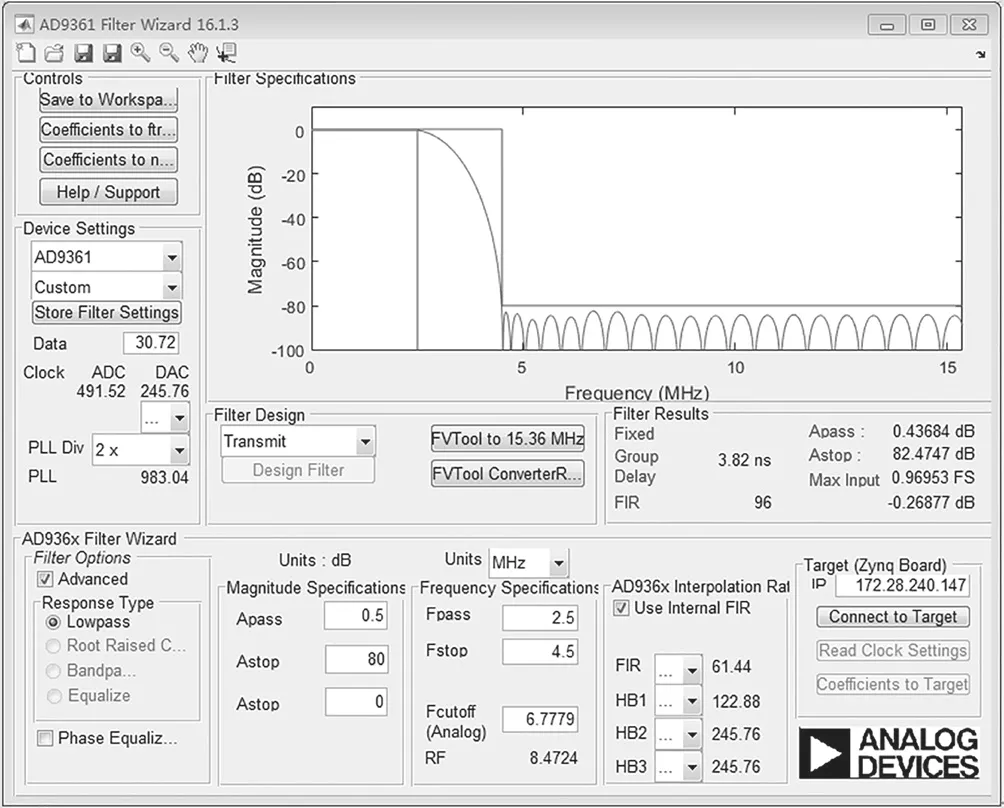

由于这个GUI 工程是自己定制的1 575 MHz 频点、5 MHz 带宽模板,在设置数字时钟和滤波器的选择卡时,需要在TX Filter Response 使用Use Custom TxFIR coeffcients file[6]。这个FIR 滤波器系数文件需要在Matlab 软件中安装AD9361 Filter Wizard 应用程序,打开这个运用程序,设置Transmit 的FIR 滤波器参数,如图2 所示。

图2 Transmit 滤波器设置参数

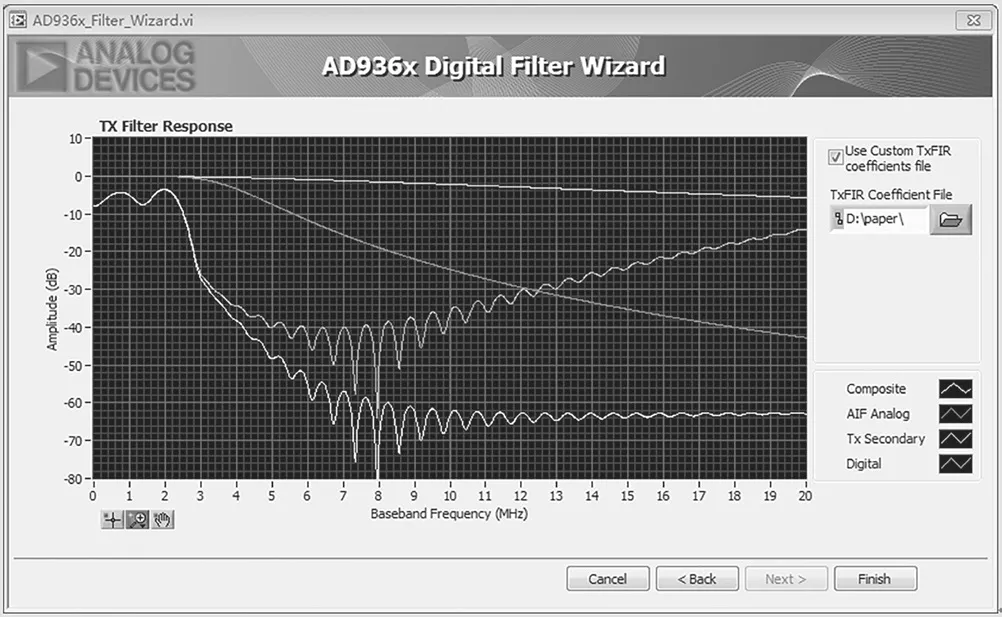

图2 中ADC 和DAC、Data Clock、FIR、HB1、HB2、HB3 的参数必须与上面AD9361 Evaluation Software 的GUI 中一致。然后,设计定制的5 MHz FIR滤波器,通带起伏Apass 设为0.5 dB,阻带衰减Astop设为80 dB,通带带宽Fpass 设为2.5 MHz,截至频率设为4.5 MHz。点击Design Filter 按钮,自动生成FIR的响应图。注意,FilterResults中的FIR 阶数是96,因为AD9365 内部的滤波器最大阶数是128 阶,因此导入这个用户定制的滤波器阶数必须小于128 阶,否则GUI 最终导出的生成脚本配置文件的滤波器系数是空的,以及其他配置参数丢失,导致不能正常配置AD9365。经过反复设置试验,图2 中的4.5 MHz 截止频率生成的滤波器阶数96 阶,比较靠近AD9365 芯片上限的128 阶,这样最终的滤波器效果会较好。点击Coefficients to ftr 保存所设计的滤波器系数文件5M.ftr,然后把这个文件导入GUI,实际的滤波器响应如图3所示。

设置完上述所有参数后,通过AD9361 Evaluation Software 的主页点击Create Init Script,导出Low Level Scripting 寄存器脚本文件。把这个寄存器配置脚本文件综合到FPGA 工程中,FPGA 的PS 端通过SPI 接口通信对AD9365 进行上电初始化配置。部分寄存器值如下:

图3 TX Filter 响应图

4 工程验证

FPGA 工程的PL 部分采用Verilog 语言编写,PS 部分采用C 语言编写。根据AD9365 的手册和GUI的数字接口配置,FPGA 的PS 端通过SPI 接口连接AD9365,对AD9365 进行初始化配置并回读校验是否配置正常,FPGA 的PL 端口将高斯白噪声数字信号通过CMOS 模式输入到AD9365 的P0 端口。

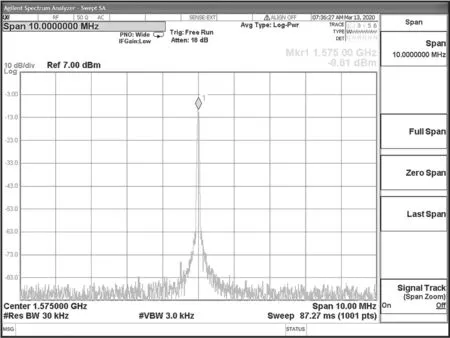

4.1 发射单音测试

首先验证AD9365 芯片单音发射的性能是否正常。通过SPI 接口直接对AD9365 的寄存器地址和值进行配置0x3F4=0xd3。该寄存器地址的功能是芯片内部发射单音信号输出到频谱仪,观察发射的射频通路是否正常,正确频率为1 575 MHz。把AD9365 的TX 接口连接到频谱仪,输出结果如图4 所示。在频谱图中可以看到,AD9365 发射状态正常。

图4 TX 发射单音信号频谱

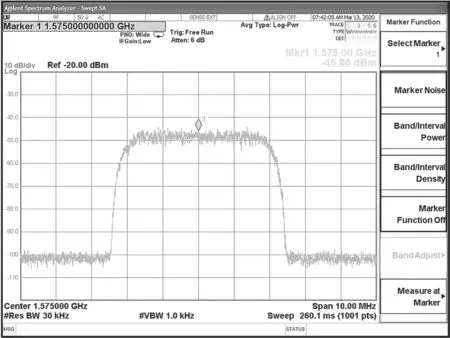

4.2 整机产生宽带干扰信号测试

测试FPGA 自身产生的高斯白噪声信号,经过AD9365 内部FIR 滤波器和上变后输出。AD9365 的发射端口连接频谱仪。从图5 频谱仪界面观察到,AD9365 的发射端中心频点是1 575 MHz,带宽是5 MHz,幅度-45 dBm,与程序预先设计一致,符合设计要求。

图5 实际发射信号频谱

5 结论

本文介绍了基于Xilinx FPGA+AD9365 的信号干扰源平台的设计与实现,详述了如何使用ADI 的AD9361 Evaluation Software v2.1.5(64-bit)的GUI软件配置AD9365,并导出配置参数脚本文件,以及在Matlab 软件中调用AD9361 Filter Wizard 应用程序,设计用户自己定制所需带宽的FIR 滤波器。最后,工程测试验证平台性能,达到了预期的设计效果。本设计方案通过使用AD9365 集成射频收发器替代传统分立元件方案,大大减小了整个系统的体积,明显缩短了硬件开发和调试周期,整体成本具有一定优势。后期市场拓展应用中,该硬件方案使用射频0~6 GHz 全带宽巴伦直接输出,属于捷变收发器AD9365 全带宽一收一发软件无线电平台,目前只用到AD9365 的发射功能,保留了接收功能。根据该平台硬件支持收发频点范围是200 MHz~2.3 GHz,最大可传输信号带宽是10 MHz。只需要更新软件工程升级,不需要更改硬件平台,并可以开发运用成其他产品,如自组电台、无线图传、补点器以及各种不同频点不同带宽的干扰源等。