动态随机存储器的故障溯源

2020-05-25TaeYeonOh

Tae Yeon Oh

多种来源的漏电流和寄生电容会引起DRAM的故障,在DRAM开发期间,工程师需仔细评估这些故障模式,当然也应该考虑工艺变化对漏电流和寄生电容的影响。

从20nm技术节点开始,漏电流一直都是动态随机存取存储器(DRAM)设计中引起器件故障的主要原因。即使底层器件未出现明显的结构异常,DRAM设计中漏电流造成的问题也会导致可靠性下降。漏电流已成为DRAM器件设计中至关重要的一个考虑因素。

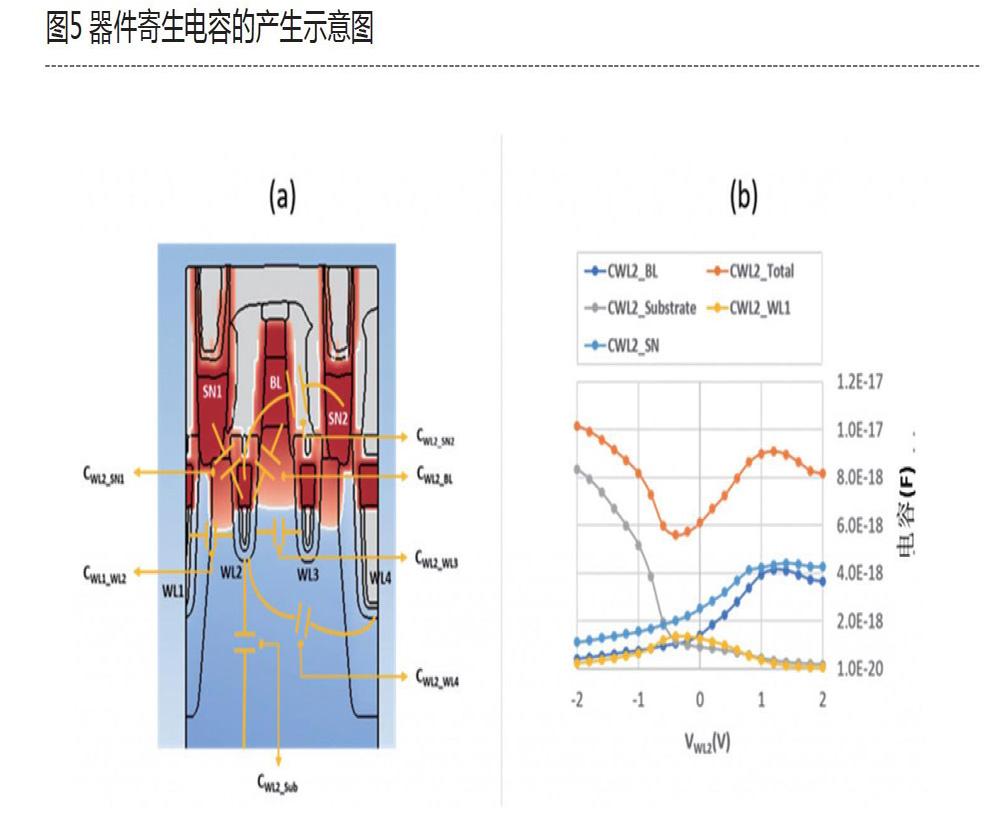

DRAM存储单元(如图1(a))在电源关闭时会丢失已存储的数据,因此必须不断刷新。存储单元在数据丢失前可存储数据的时间,即保留时间,是DRAM的一个关键特性,保留时间的长短会受到漏电流的限制。

有两种重要的漏电机制会影响DRAM的数据保留时间。

第一种是单元晶体管漏电。DRAM中的单元晶体管漏电主要由于栅诱导漏极泄漏电流(GIDL)(如图1(b)),它是由漏结处高电场效应引起的漏电流。在负栅偏置下,栅极会产生一个耗尽区(N+漏极区),该耗尽区进而在区域中产生一个增强电场,这个电场造成的能带弯曲则导致了带间隧穿(BTBT)。此时,在栅极移动的电子和少数载流子可以穿过隧道进入漏极,从而产生不必要的漏电流。

DRAM中的第二种漏电机制是位线接触 (BLC)与存储节点接触(SNC)之间的电介质泄漏(如图1(c))。电介质泄漏通常发生在电容内部,此时电子流过金属和介电区域(如图1(d))。当电子通过电介质层从一个电极隧穿到另一个电极时,便会引起电介质泄漏。随着工艺节点的缩小,BLC和SNC之间的距离也在逐渐缩短,因此,这个问题正在变得愈发严重。这些结构元件的制造工艺偏差也会对位线接触和存储节点接触之间的电介质泄漏产生负面影响。

虚拟制造平台SEMulator3D可使用设计和工艺流数据来构建DRAM器件的3D模型。完成器件的“虚拟”制造之后,用户可通过SEMulator3D查看器从任意方向观察漏电路径,并且可以计算推导出总的漏电值。这一功能对了解工艺变化对DRAM漏电流的影响大有帮助。SEMulator3D中的漂移/扩散求解器能提供电流-电压(IV)分析,包括GIDL和结点漏电计算,以实现一体化设计技术的协同优化。用户还可以通过改变设计结构、掺杂浓度和偏置强度来查看漏电值的变化。

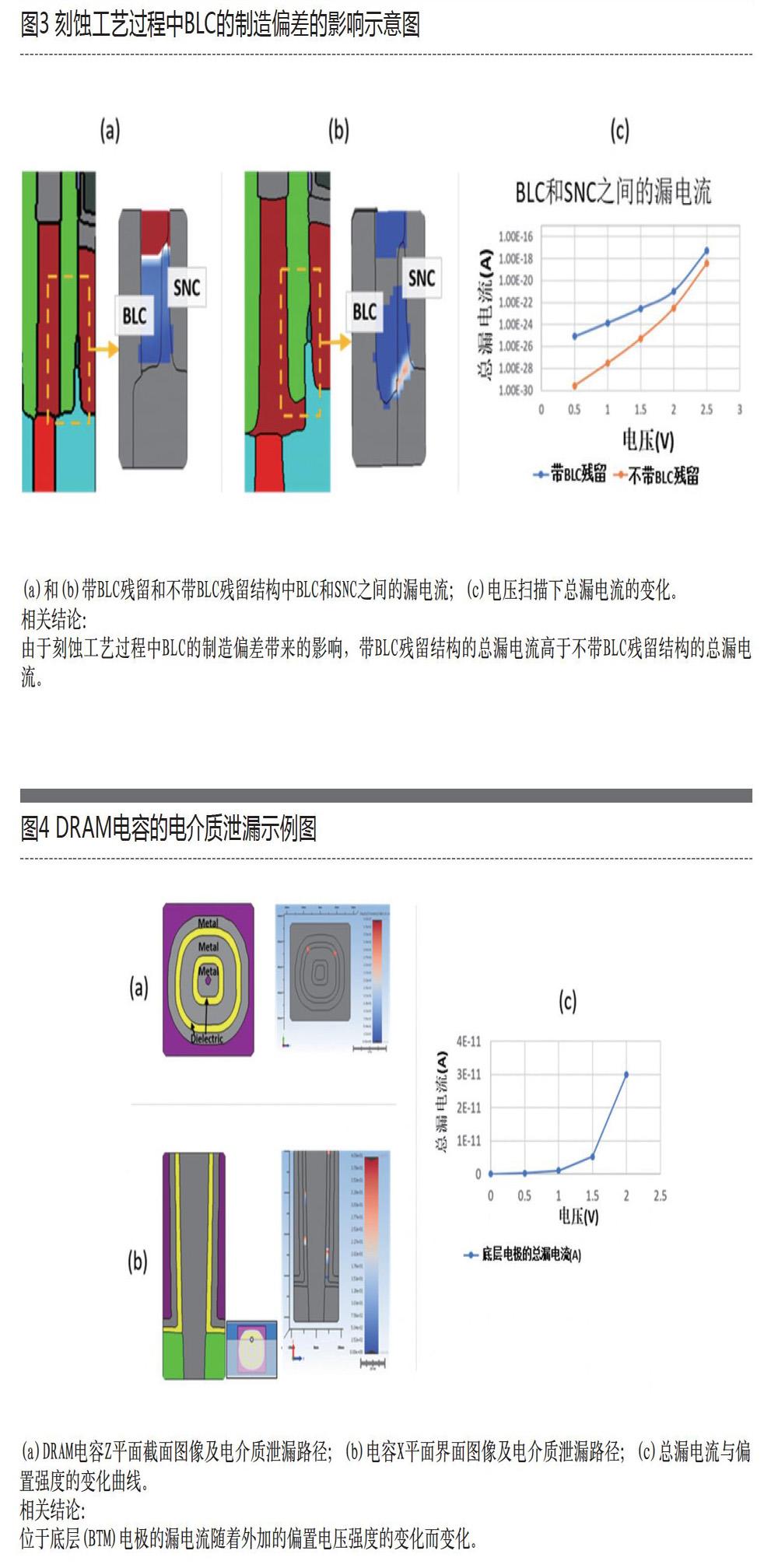

图2表明GIDL会随着栅极氧化层厚度的变化而增加。栅极氧化层越薄,建模器件的栅极与漏极之间的电势越高。

图3显示了SEMulator3D中的电介质泄漏路径以及位线接触和存储节点接触之间的总电流差,突出了刻蚀工艺过程中BLC的制造偏差带来的影响。如图3(c)所示,由于工艺偏差的影响,带BLC残留结构的总漏电流高于不带BLC殘留结构的总漏电流。

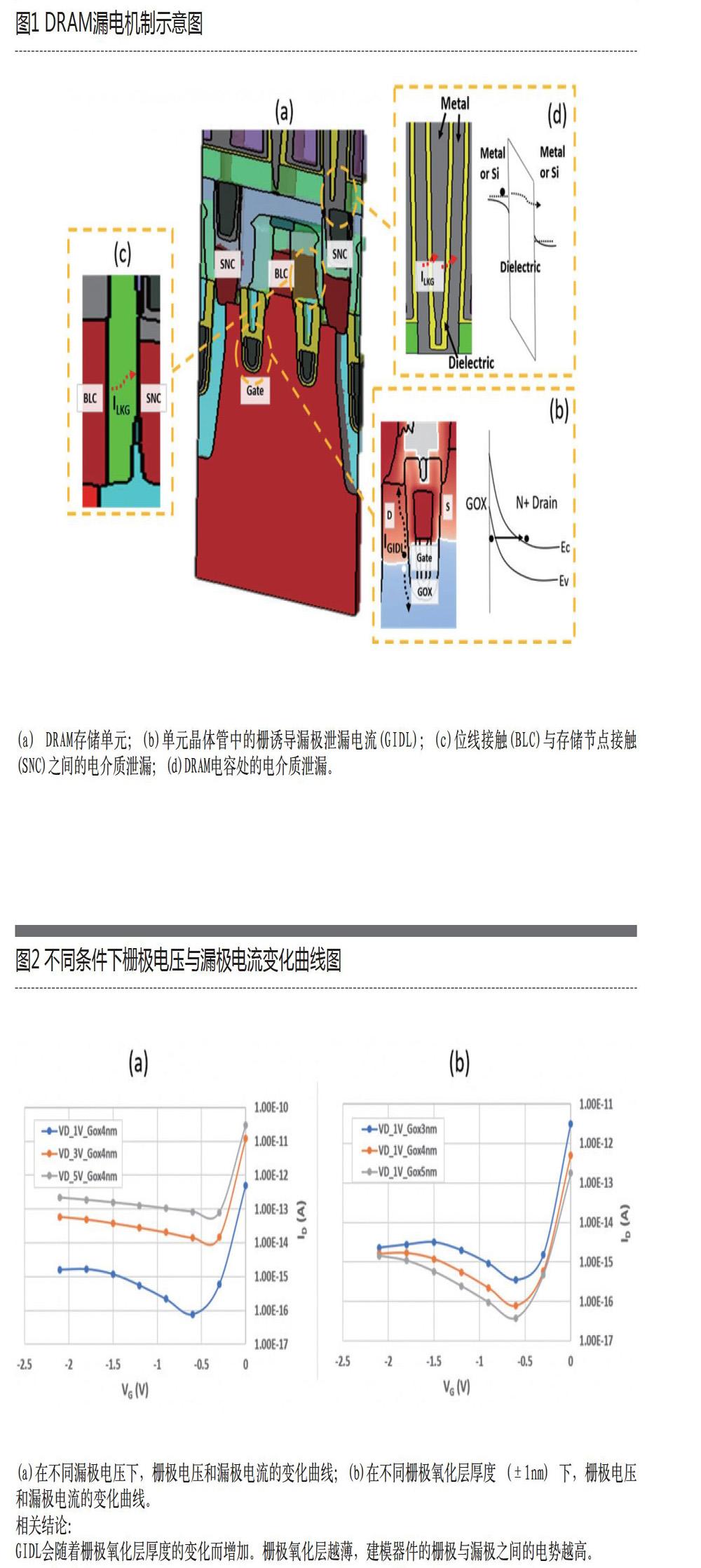

图4所示为DRAM电容的电介质泄漏的例子。图4(a)和4(b)分别是DRAM的Z平面和X平面截面图,以及在SEMulator3D器件模型中观察到的电介质泄漏路径在这两个平面上的投影。图4(c)显示了位于底层(BTM)电极的漏电流随着外加的偏置电压强度的变化而变化。

影响DRAM性能的另一个重要因素是器件的寄生电容。DRAM开发期间应进行交流(AC)分析,因为位线耦合会导致写恢复时间(tWR)延迟,并产生其他性能故障。掺杂的多晶硅不仅用于晶体管栅极,还用于位线接触和存储节点接触,这会导致多个潜在的寄生电容产生(如图5(a)),所以,必须对整个器件进行电容测量。SEMulator3D内置AC分析功能,可测量复杂的模拟3D结构的寄生电容值。例如,通过模拟将交流小信号施加到字线WL2,SEMulator3D可以获取全新设计的DRAM结构中字线WL2与其它所有节点之间的电容值,以及它们随着电压变化而变化的曲线(如图5(b))。

总而言之,多种来源的漏电流和寄生电容会引起DRAM的故障。在DRAM开发期间,工程师需仔细评估这些故障模式,当然也应该考虑工艺变化对漏电流和寄生电容的影响。通过使用预期工艺流程和工艺变化来“虚拟”构建3D器件,然后分析不同工艺条件下的寄生和晶体管效应,简化DRAM的下一代寻径过程。SEMulator3D集成了3D工艺模型、R/C分析和器件分析功能,可以快速地验证DRAM器件结构在不同工艺假设下是否容易发生漏电流或寄生电容故障。