LCD驱动实时显示控制电路的Verilog设计

2020-05-07杨翠娥

杨翠娥

(太原工业学院,山西 太原 030008)

0 引言

FPGA芯片作为大规模可编程器件,以其高集成度、高速、可反复编程等特点在电子产品设计中得到了广泛的应用。作为FPGA的数据输出外设,一般有LED数码管输出及LCD液晶显示输出较为常见。而对LCD液晶显示输出控制是FPGA设计的一个难点,一种方法是可以通过8051IP核加ROM模块通过汇编程序实现,资源消耗大;另一种方法是直接用Verilog程序设计实现控制时序,简单明了,资源利用率高,而且易于移植。一般资料给出的Verilog程序设计完成的LCD显示控制只能显示固定地址的字符,本设计给出的LCD显示控制模块,可以对输入端口的数据实时显示,且可以移植应用到各种需要LCD外设的FPGA设计中。

1 LCD1602工作原理简介

LCD1602液晶显示器是一种应用广泛的字符型液晶显示模块。1602是指显示的内容为16*2,即显示两行,每行16个字符。目前大多数的字符液晶都是基于HD44780液晶芯片的,控制原理基本相同,因此基于HD44780写的Verilog控制程序可以很方便地应用于其他型号的字符型液晶。LCD1602通常有16条引脚线,除了电源、地管脚,其他就是控制读写的端口及输出8位数据口。HD44780内置了DDRAM、CGROM和CGRAM。其中DDRAM用来寄存待显示的字符代码。共80个字节,其地址和字符的对应关系可参考其他资料[1]。1602液晶模块内部的字符发生存储器(CGROM)已经存储了160个不同的点阵字符图形,每一个字符都有一个固定的代码。在程序中时可以直接用比如P1=“A”这样的方法,PC在编译时可以自动把“A”转换为对应的41H代码。对DDRAM中的内容和地址进行操作,需要通过不同的指令来完成。通过Verilog程序设计也可以实现对LCD1602的指令控制、写入数据指令控制及如何在指定位置显示字符等的功能。

2 基于Verilog的LCD1602驱动程序设计

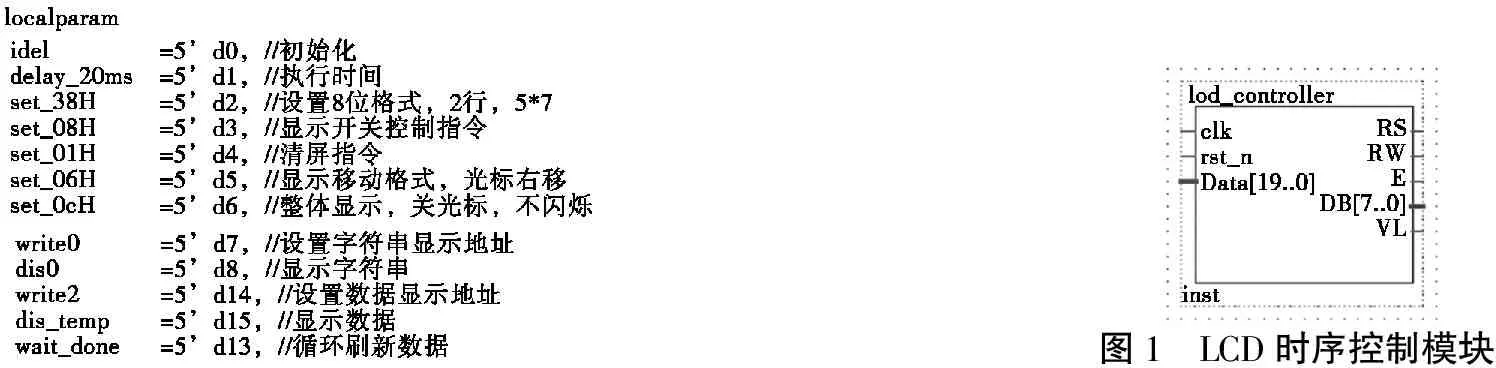

图1所示为用Verilog程序设计的LCD时序控制模块,输入端口除了时钟和复位端,还有20位的数据输入端口;输出端口和LCD字符显示器管脚对应。根据Verilog程序设计特点,完成对LCD的时序控制可通过状态机的设计方法。下面一段程序内容用关键词localparam首先定义了12个不同的参数,分别对应于LCD显示控制、数据、地址的读写控制等不同的工作状态。

图1 LCD时序控制模块

以dis_temp(显示数据)状态为例,下面给出了对应的Verilog程序。首先要判断状态执行的时间,LCD1602完成一次数据的显示需要一定的时间,在此设定为20ms。如果时间到就可以进行此状态的工作及转换到下一个状态,如果时间不到就一直保持此状态。显示输入数据时,因为一个字符占8个字节,所以要完整显示电压值比如“0.02V”五个字符时,要设定显示数据宽度为40位,即39到0;每次显示一个字符,光标右移再显示第二个字符,所以cnt要计数5次,以完成5个字符的循环显示。

下面的程序给出了如何把输入的二进制数实时显示为对应的显示字符,如最高4位数据,除了正常数字0~9对应显示“0~9”的字符外,根据具体设计内容,还增加了10,11的二进制编码,在此用于显示小数点“.”和电压的单位“V”二个字符。

3 基于FPGA的LCD实时显示设计举例

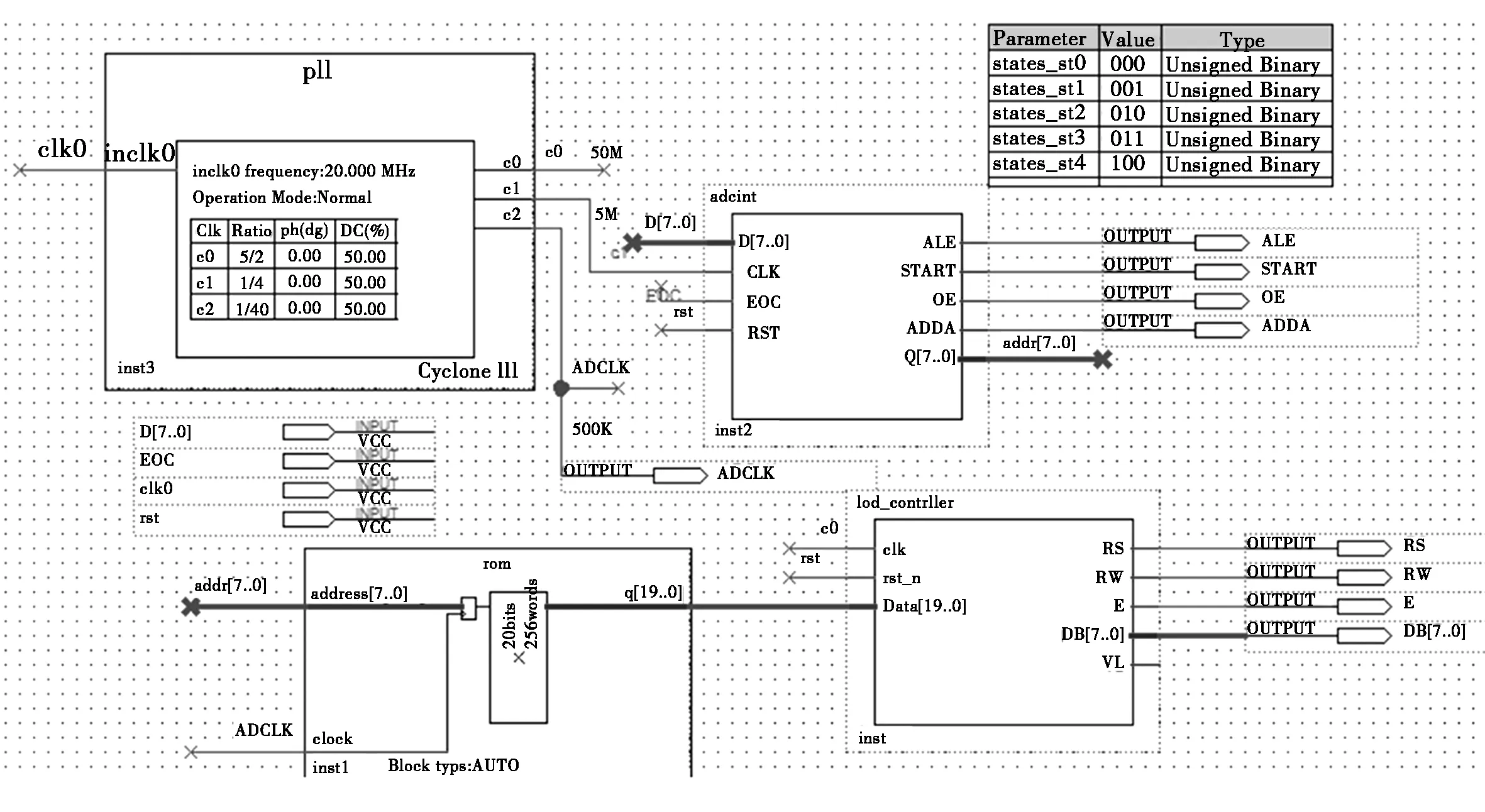

如图2所示给出了基于FPGA的数字电压表及LCD显示设计的顶层电路图,图中共有四个模块:锁相环PLL模块把系统时钟clk0通过分频和倍频输出三个时钟,分别提供给AD转换控制模块、LCD时序控制模块及ROM数据读取模块作为工作时钟所用,其中ADCLK同时输出给外部AD0809芯片使用;ADCINT模块是基于Verilog设计的AD0809状态转换控制模块,完成对外部AD0809芯片模拟量到数字量的转换控制[2];由于AD0809芯片输出的是8位二进制数,其电压分辨率为5V/256,约为0.02V,要想通过LCD直接显示对应的电压值,还需要通过ROM模块实现转换。ROM模块的功能是通过建立初始化mif文件,形成二进制与电压的对应关系,然后把AD0809芯片输出的8位二进制数作为ROM的地址,这样就完成了二进制数到对应电压值的转换。ROM模块数据的输出作为给LCD显示控制模块的数据输入,通过上述实现的LCD显示控制模块完成对输入数据的LCD显示输出。

图2 数字电压表顶层电路图

如下给出了mif初始化文件的部分内容[3]:

可以看出,通过编码,设定1010(A)为显示小数点字符,1011(B)为显示电压的单位“V”字符,地址每加1,对应显示的内容增加0.02V,这样就可以通过LCD控制模块控制LCD实时显示所输入的模拟电压值。图3为LCD显示的实时电压测量数据。

图3 LCD显示的实时电压测量数据

4 结束语

Verilog硬件设计语言是实现FPGA设计的主要设计输入方法之一,语法简单,结构明了,尤其是状态机的设计描述方法可以很方便地完成FPGA的各种模块设计。本论文通过对LCD显示控制的Verilog状态机设计,完成了对LCD实时数据显示控制,该设计程序模块化,标准化,可广泛应用到FPGA的系统设计中。