4电平S类数字功放的电平合成策略*

2020-05-06陈剑斌

周 强,朱 蕾,陈剑斌

(国防科技大学 第六十三研究所, 江苏 南京 210007)

无线通信技术及业务需求的迅速发展,对射频功放的效率和线性等指标都提出了更高要求。基于增量求和调制[1](Delta-Sigma Modulation, DSM)和开关模式功放[2-3](Switch-Mode Power Amplifier, SMPA)的S类数字功放[4-7](Digital Power Amplifier, DPA),因其结构简单,兼具高效率、高线性、可重构特性,适合在全数字发信机中应用[8-9]。但DSM编码效率较低[10]和对调制器处理速率要求高等问题,限制了S类DPA在射频、微波频段的应用。

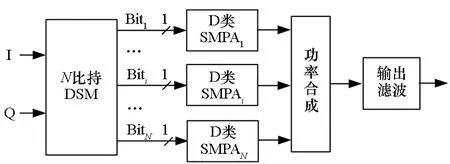

图1 多电平S类数字功放Fig.1 Multilevel class-S digital power amplifier

针对上述问题,文献[11]采用3比特DSM,通过增加量化电平,减小了量化误差,提高了输出信噪比。由于N比特DSM包含2N个量化电平,其输出脉冲序列无法直接驱动现有D类或E类等SMPA,如图1所示,需采用N个SMPA单元,并通过功率合成实现2N电平输出。通过面积等效等策略,文献[12]将多电平DSM输出序列转换为2电平,降低了后级SMPA的实现难度,但显著增加了功率管的开关频率及其开关损耗,降低了SMPA效率。基于H桥D类SMPA以及功率管的开关特性,文献[13]采用多个H桥单元输出电平合成(Level Synthesis, LS)实现了多电平直接输出,省去了功率合成单元,并在超短波频段实现了一种基于2比特DSM的4电平S类DPA,输出功率10 W,效率大于60%,三阶互调达57 dBc。

然而,仍未见文献分析LS实现策略对功放性能的影响。因此,在文献[13]的基础上,针对2比特DSM输出序列,本文研究了4电平S类DPA的LS策略,分析了不同LS策略对功放性能的影响。

1 4电平合成策略

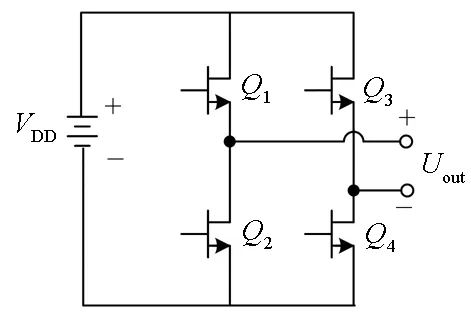

2比特DSM输出序列具有11、10、01、00共4种状态,因此后级SMPA需对应输出U、U/3、-U/3和-U共4种电平(U为归一化电平)。受SMPA电路限制,即使输出电平能力较强的H桥D类SMPA[4](如图2所示,VDD为电源电压,Uout为输出电平),忽略功率管导通压降,最多也只能输出VDD、0、-VDD共3种电平。即,Q1/Q4导通、Q2/Q3截止时,Uout=VDD;Q2/Q3导通、Q1/Q4截止时,Uout=-VDD;Q1/Q3导通、Q2/Q4截止或Q2/Q4导通、Q1/Q3截止时,Uout=0。因此,4电平SMPA需对2个H桥D类SMPA输出电平进行合成。

图2 H桥D类SMPAFig.2 H-bridge class-D SMPA

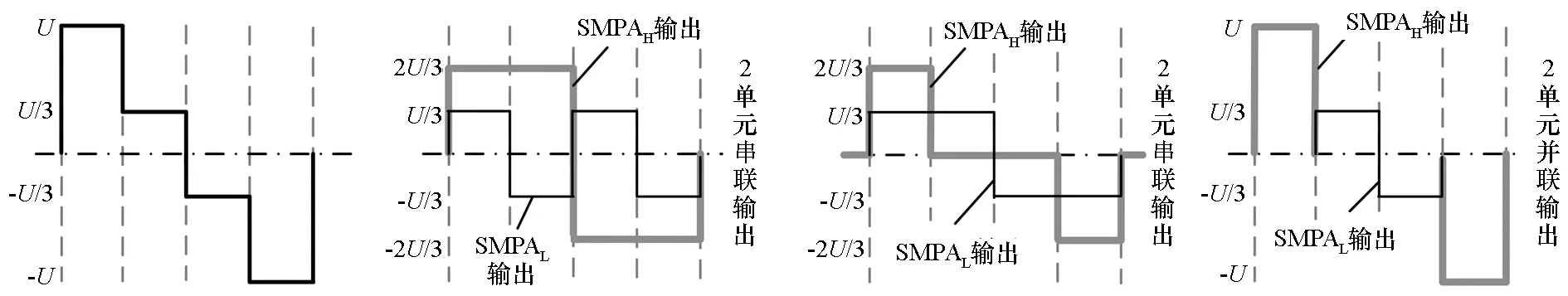

以H桥D类SMPA为基本单元,根据SMPA单元的电源电压、输出电平及其合成方式的不同,所需4电平合成可有多种实现方式。在文献[11-12]采用的常规LS策略(LS1)基础上,本文提出了如图3(b)、(c)所示的LS2和LS3。其中,根据2个SMPA单元的电平合成方式,3种LS策略可分为“代数相加”(LS1、LS2)和“选择输出”(LS3)两类。

所谓“代数相加”,即通过2个SMPA单元输出电平的代数相加实现4电平合成,可通过2个H桥单元串联输出实现。根据所需输出电平,可分别确定高压单元(SMPAH)的VDD为2U/3,低压单元(SMPAL)的VDD为U/3。根据SMPAH输出电平的不同,“代数相加”策略又可分为LS1和LS2。其中,LS1如图3(a)所示,2个H桥单元分别实现±2U/3和±U/3输出,输出电平代数相加即可实现4电平(U=2U/3+U/3、U/3=2U/3-U/3、-U/3=-2U/3+U/3、-U=-2U/3-U/3)合成输出。LS2如图3(b)所示,其SMPAH除输出±2U/3电平外,还需实现0电平输出,与SMPAL输出的±U/3电平代数相加即可实现4电平(U=2U/3+U/3、U/3=0+U/3、-U/3=0-U/3、-U= -2U/3-U/3)合成输出。

所谓“选择输出”,即LS3,如图3(c)所示,根据所需输出电平,选择具有该电平输出能力的单元直接输出对应电平,同时使另一个单元无电平输出(即输出开路),可通过2个SMPA单元并联输出实现。其中,SMPAH的VDD为U,SMPAL的VDD为U/3,2个SMPA单元分别输出±U和±U/3电平。

根据所需合成的电平,图4给出了3种LS策略对应各SMPA单元输出电平及合成示意。从图中可以看出,LS1的2个SMPA单元任何时刻均有电平输出;LS3任何时刻仅一个单元有电平输出;而LS2介于两者之间,其中,SMPAL在任何时刻均有电平输出,SMPAH仅在输出±U电平时才有输出。

(a) 代数相加Ⅰ (LS1)(a) Algebraic addition Ⅰ(LS1) (b) 代数相加Ⅱ(LS2)(b) Algebraic addition Ⅱ(LS2) (c) 选择输出 (LS3)(c) Select output (LS3)图3 LS1、LS2、LS3示意Fig.3 Schematic diagram of LS1, LS2, and LS3

(a) 所需输出电平(a) Desirable output level (b) LS1(b) LS1 (c) LS2(c) LS2 (d) LS3(d) LS3 图4 LS1、LS2、LS3对应的电平合成示意Fig.4 Schematic diagram of level synthesis for LS1, LS2, and LS3

2 LS策略对S类DPA性能的影响

2.1 LS策略对Pout和Pcon的影响

对于电压型SMPA,Pout取决于VDD、功放内阻Rs和负载电阻RL,Pout可表示为:

(1)

式中:ηce为编码效率;n为输出电平数;Ui为理想条件下(忽略Rs)的第i种输出电平;ki为该输出电平所占比例;Us=Rs·IL为Rs带来的导通压降,IL为功放输出的负载电流。由式(1)可知,Rs带来的Us将降低功放实际的输出电压幅度,进而影响Pout。Pcon取决于Rs和IL,可表示为:

(2)

由式(2)可知,Pcon正比于Pout和Rs。因此,为降低Pcon和提高Pout,均需减小Rs。

假设所有功率管的Ron相等,则Rs=kRon,k为同时导通的功率管数量。由于LS1和LS2在任何时刻均有4个功率管导通,而LS3仅2个功率管导通,因此LS1和LS2具有相同Pout和Pcon,LS3则具有最小的Pcon和最大的Pout,而且Pcon仅为LS1和LS2的一半左右。

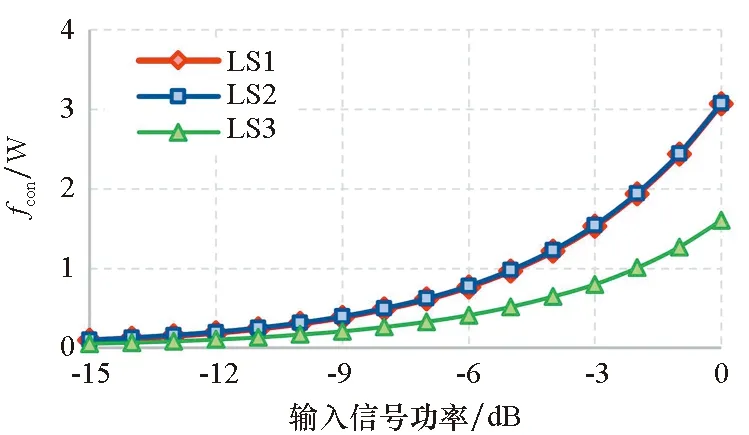

图5和图6分别给出了3种LS策略的Pout和Pcon仿真对比。其中输入信号为载波频率fc=35 MHz的单音信号,2比特输出序列由4阶带通DSM[13]产生,采样频率fs=600 MHz,功率管采用原Triqunt公司2.5 mm栅宽GaN HEMT管芯,Ciss和Coss分别约为4.5 pF和1.5 pF,Ron约1.8 Ω,U取54 V,RL取50 Ω,采用理想输出滤波器。仿真结果验证了前文的分析,相比LS1和LS2,LS3的Pout增加了10%以上,而Pcon减小约47%。

图5 LS1~LS3的Pout仿真对比Fig.5 Simulation contrast between LS1~LS3 for Pout

图6 LS1~LS3的Pcon仿真对比Fig.6 Simulation contrast between LS1~LS3 for Pcon

2.2 LS策略对Pdrv和Psw的影响

Pdrv(此处仅指驱动功率管开关切换带来的瞬态驱动功耗)和Psw取决于SMPA中所有功率管在单位时间内的总开关切换次数(即平均开关频率fav)以及Ciss、Coss充放电前后功率管的栅源、漏源电压之差ΔVgs和ΔVds。假设所有功率管具有相同寄生参数,则Pdrv和Psw可分别表示为:

(3)

(4)

其中,ΔVdsH、ΔVdsL和favH、favL分别为SMPAH和SMPAL功率管的ΔVds和fav。

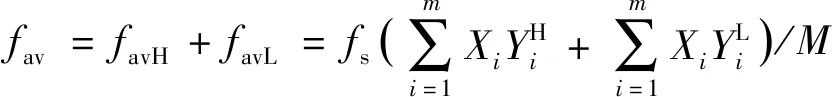

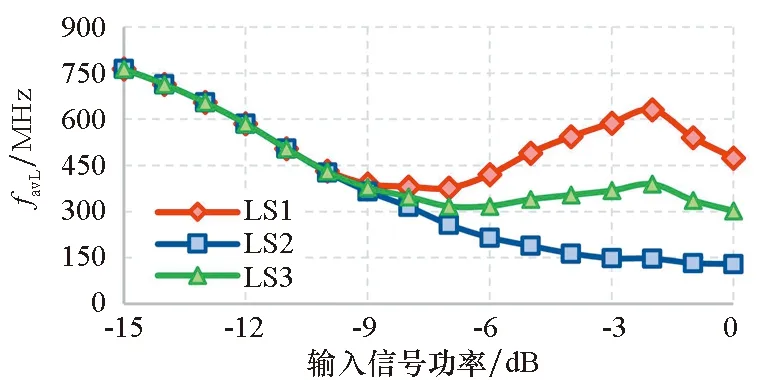

对于2比特DSM序列,估计fav时不仅要考虑对应输出电平的变换次数,还需要考虑电平变换时LS对应各SMPA单元功率管的开关切换次数。fav可由式(5)估计:

(5)

对于一定长度的2比特DMS输出序列,当fs=600 MHz时,图7给出了电平变换次数的仿真对比,图例中1~6分别对应上述6类输出电平变换。从图7中可知,第2、3、5类电平变换次数基本可忽略,输出电平仅在相邻电平间变换;当输入信号功率较小时,输出电平主要在±U/3间变换,随着输入功率的增加,U/3⟺-U/3的变换次数相应减小,电平在U和U/3、-U和-U/3间的变换次数逐渐增加。

图7 电平变换次数的仿真对比Fig.7 Compared the number of level switches

对应上述6类输出电平变换,由图4以及H桥D类SMPA的控制逻辑,表1给出了不同LS策略下SMPA所有功率管的总开关切换次数对比。可以看出,相比于LS1,在U/3⟺-U/3变换时,由于改变了各SMPA单元的输出电平,LS2和LS3对应功率管的总开关切换次数仅为LS1的一半,因此可显著减小fav。

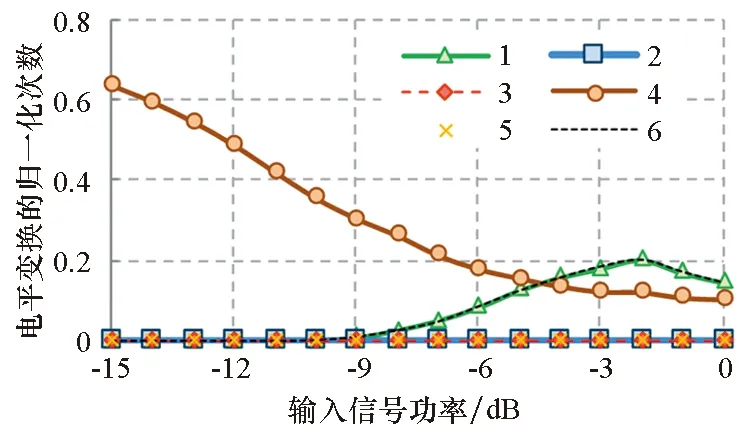

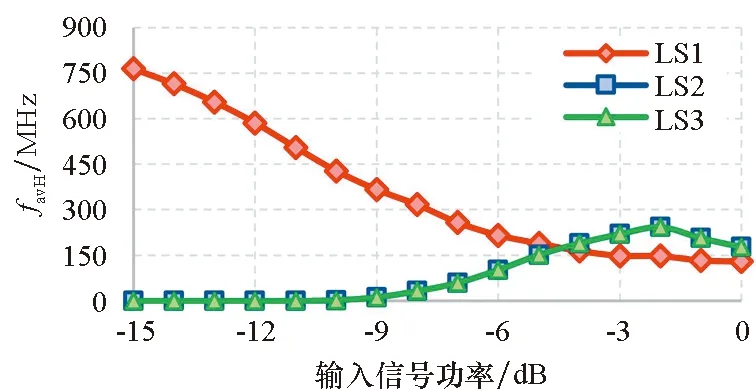

根据图7、表1和式(5),图8~10分别给出了3种LS策略的favH、favL和fav对比。可以看出,LS1的favH等于LS2的favL,LS2和LS3具有相同favH。当输入信号较小时(功率回退6 dBc以上),2比特DSM退变为1比特,输出电平仅在±U/3间切换,此时LS1~LS3具有相同favL且与LS1的favH相等,并随输入信号功率的减小而迅速增大,而LS2和LS3的favH基本为零。因此当输入较小时,LS2和LS3的fav仅为LS1的1/2。当输入较大时,LS1的fav最大,LS3次之,LS2最小且为LS1的1/2。

表1 电平变换时功率管总开关切换次数对比Tab.1 Compared the total switching times of transistors

图8 LS1~LS3的favH仿真对比Fig.8 Simulation contrast between LS1~LS3 for favH

图9 LS1~LS3的favL仿真对比Fig.9 Simulation contrast between LS1~LS3 for favL

图10 LS1~LS3的fav仿真对比Fig.10 Simulation contrast between LS1~LS3 for fav

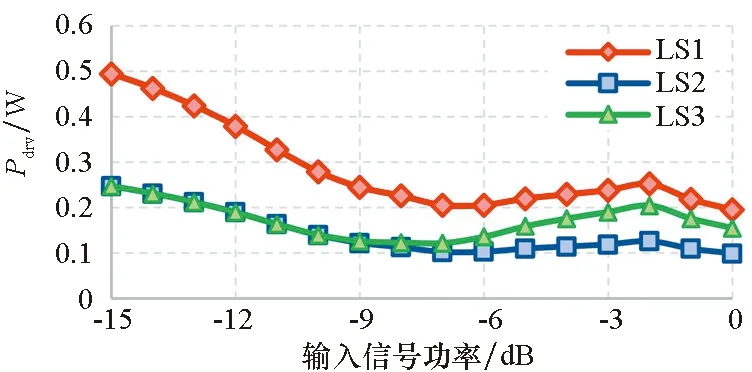

对驱动器件而言,为使所有功率管工作在开关状态且保持Ron等参数一致,就需施加相同且对应的驱动电压,因此不同LS策略的功率管均具有相同的Ciss和ΔVgs。为使GaN HEMT管芯完全工作在开关状态,可令ΔVgs为5 V。图11给出了3种LS策略的Pdrv对比,由于Pdrv与fav成正比,因此输入较小时,LS2和LS3具有明显优势,其Pdrv相等且仅为LS1的一半;输入较大时,LS1的Pdrv仍为最大,LS3次之,LS2最小且为LS1的一半。

图11 LS1~LS3的Pdrv仿真对比Fig.11 Simulation contrast between LS1~LS3 for Pdrv

对功率管而言,如图3所示,不同LS策略对应SMPAH和SMPAL的VDD不同,即使输出相同电平,各单元的输出电平和对应功率管的控制逻辑也不相同,因此不同LS策略各单元对应功率管的ΔVds并不完全相同。

其中LS1和LS2通过2个SMPA单元串联输出实现电平合成,具有相同电路拓扑和电源配置,虽然各SMPA单元输出电平不同,但任意时刻均有4个功率管导通,忽略Ron的导通压降,则有ΔVds=VDD。因此LS1和LS2具有相同ΔVdsH和ΔVdsL,即ΔVdsH=2U/3、ΔVdsL=U/3。LS3的2个SMPA单元并联输出,在任意时刻仅2个功率管导通,对应不同输出电平变换,各功率管的ΔVds也各不相同。参照式(4)和式(5),LS3的Psw可由式(6)计算:

(6)

表2 LS3各功率管的ΔVds和等效开关次数Tab.2 Compared the ΔVds and equivalent switching times of transistors for LS3

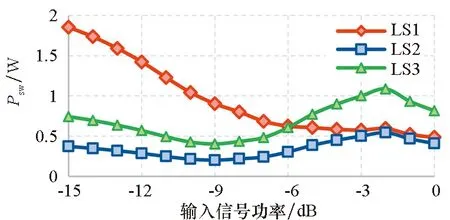

图12 LS1~LS3的Psw仿真对比Fig.12 Simulation contrast between LS1~LS3 for Psw

2.3 LS策略对Ps和η的影响

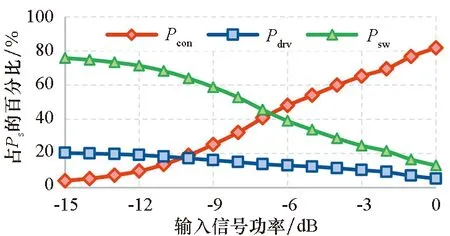

图13 LS1中Pcon、 Pdrv和 Psw占Ps的比例Fig.13 Proportion of Pcon, Pdrv, and Psw in Ps for LS1

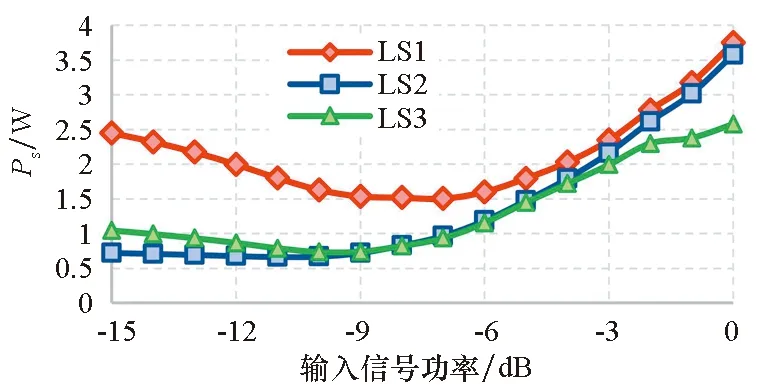

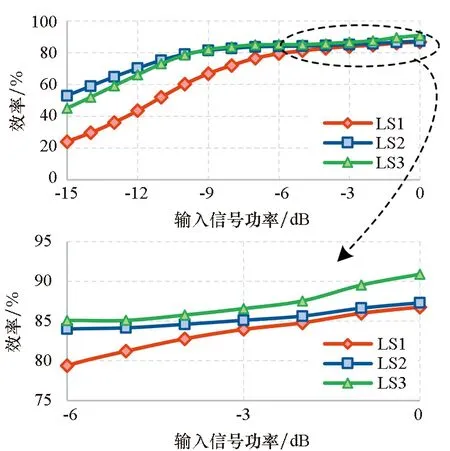

图13给出了LS1的Pcon、Pdrv和Psw分别占功放总损耗Ps(Ps=Pcon+Pdrv+Psw)的比例。从图13可以发现,当输入较大时,由于Pcon正比于Pout,Pcon占Ps绝大部分,随着输入信号功率回退,Pcon所占比重逐渐降低,而Psw的比重却逐渐增大,并最终成为Ps的主要部分。可见要减小LS1的Ps,一方面可在输入较大时减小Pcon,另一方面可在输入较小时减小Psw。由于LS2实现了后者,LS3两者都实现了,因此如图14和图15所示,LS2和LS3的Ps均小于LS1,且明显提高了η(η=Pout/(Ps+Pout))。特别在输入较小时,LS2和LS3更具优势,其Ps仅为LS1的30%~40%,η可提高约20%。当输入较小时,由于在Psw上的优势,LS2具有最小的Ps和最高的η;当输入较大时,由于在Pcon上的优势,LS3相对最优。

图14 LS1~LS3的Ps仿真对比Fig.14 Simulation contrast between LS1~LS3 for Ps

图15 LS1~LS3的η仿真对比Fig.15 Simulation contrast between LS1~LS3 for η

3 结论

理论分析和仿真结果表明,LS2和LS3可显著减小Pcon、Pdrv和Psw等器件损耗,获得更优输出性能,尤其功率回退状态下,对功放性能的提升更为显著,因而有利于提高高峰均比调制信号的功率放大性能。

对比LS2,在相同输出电平条件下,LS3具有更大输出功率且在输入较大时具有效率优势,因而LS3在理论上有优势。但在实践中,由于LS3需要更高电源电压,同时受SMPA单元并联输出的电平箝位效应影响,将增加各SMPA单元功率管的电压应力,其最大电压应力约为LS2的2倍。在选取功率管时,考虑器件击穿电压并预留足够余量,LS3允许的电源电压及最大输出电平将小于LS2,从而显著降低了LS3在功率和效率方面的优势。此外,LS3高压和低压SMPA单元间的输出功率存在较大差距,需解决单元间的功率均衡问题。因此,LS2在工程实践中将更具优势。